首先,本人查找了异步复位同步释放原理网络相关资料。大都没有讲清楚相关原理性的东西,令人困恼。

现花了一天时间进行原理性的解答:理解为什么异步复位、同步释放能够实现?

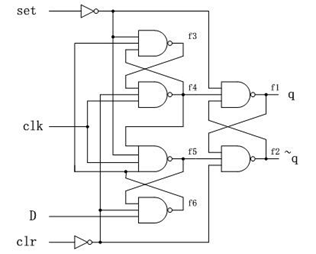

首先要知道复位D触发器的工作原理,复位信号作用于最后端口也作用于触发器逻辑中间。

当复位端有效时(一般为1),复位信号直接作用于最后一级的SR锁存器(需要知道锁存器的原理以及触发器的原理,这个是电子的基础),此时触发器直接输出q为0。

当复位信号无效时(为0时),复位信号为0,不能驱动最后一级SR锁存器,此时输出q=输入的d,其中由时钟信号与复位信号共同进行控制数据的变化,使q=d。

该图为set,clr都为复位端的图,我们理解时,使用单独set进行理解。

异步复位、同步释放。

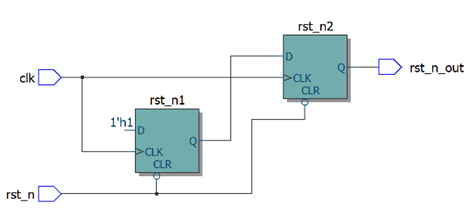

module code ( clk,rst_n,rst_n_out); input clk; input rst_n; output rst_n_out; //wire rst_n_out_n; //输入输出没定义类型,默认是wire型 reg rst_n1; reg rst_n2; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin rst_n1 <= 1'b0; rst_n2 <= 1'b0; end else begin rst_n1 <= 1'b1; rst_n2 <= rst_n1; end end assign rst_n_out = rst_n2; endmodule

先以rst_n为0,复位端即为1(将此时为复位状态作起点),此时q1与q2同时由复位信号rst_n控制,直接输出为0。

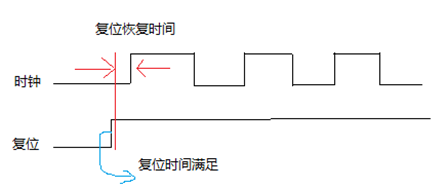

当rst_n从0变为1过程中时,此时复位端变为0,将无法直接作用与触发器的输出端。此时的状态,q1由d1决定,q2由d2确定。此时由于q1有时钟上升沿与复位信号共同作用与第一触发器

,由于d1为,q1输出将根据clk来决定,而此时由于时钟与复位信号已经作用与第二触发器,此时d2为之前q1=0的状态,由于d2为0,根据D触发器的原理,无论clk为什么,q2=0,于是q2继续输出为0。

当第一触发器不满足复位信号与时钟信号的恢复时间时,即不满足第一级触发器内部延时,这个时候,第一级触发器将发生亚稳态状态,而此时第二级触发器已经上升沿完毕,

需要等下一个上升沿才能继续改变q2数据。

当亚稳态时间过去之后(亚稳态时间不会超过一个周期,超过一个周期仍然会影响到第二级触发器),下一个周期时钟来临时,此时第一触发器已经能够正常的输出为1,而第二触发器也能够直接等于d2,这时输出rst_n_out = 1,完成复位。

也就是说异步复位、同步释放的本质就是,将原本由异步复位信号在有效时能直接作用于输出端,改为延后一个周期通过在复位信号无效时进行时钟控制,即同步释放。