Xilinx 复位准则:

(1)尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

(2)如果必须要复位,在同步和异步复位上,则尽量使用同步复位,一定要用异步复位的地方,采用“异步复位、同步释放”;

(3)复位电平选择高电平复位;

(这里说明,由于 Altera 和 Xilinx 器件内部结构的不同,Altera 的 FPGA 推荐低电平复位)

参见:不得不读的 FPGA 设计白皮书——Xilinx FPGA 复位策略白皮书翻译(WP272)【FPGA探索者】

一、异步复位同步释放

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

比如针对输入的异步复位信号rst,使用本地时钟clk将其同步化以后得到一个新的复位信号sys_rst,当使用sys_rst时,是将sys_rst作为同步复位信号还是异步复位信号?

/***** 此程序来自公众号:硅农 ********/

always @(posedge clk or posedge rst)

begin

if(rst)begin

rst_r0 <= 1'b1;

rst_r1 <= 1'b1;

end

else begin

rst_r0 <= 1'b0;

rst_r1 <= rst_r0;

end

end

assign sys_rst = rst_r1;

如下图所示,选方式 1 还是方式 2 ?

针对此问题查找了很多资料,网络上多是将 sys_rst 继续按照方式 1 异步复位使用,Xilinx 复位白皮书 wp272 中提到的异步复位同步释放如图所示:

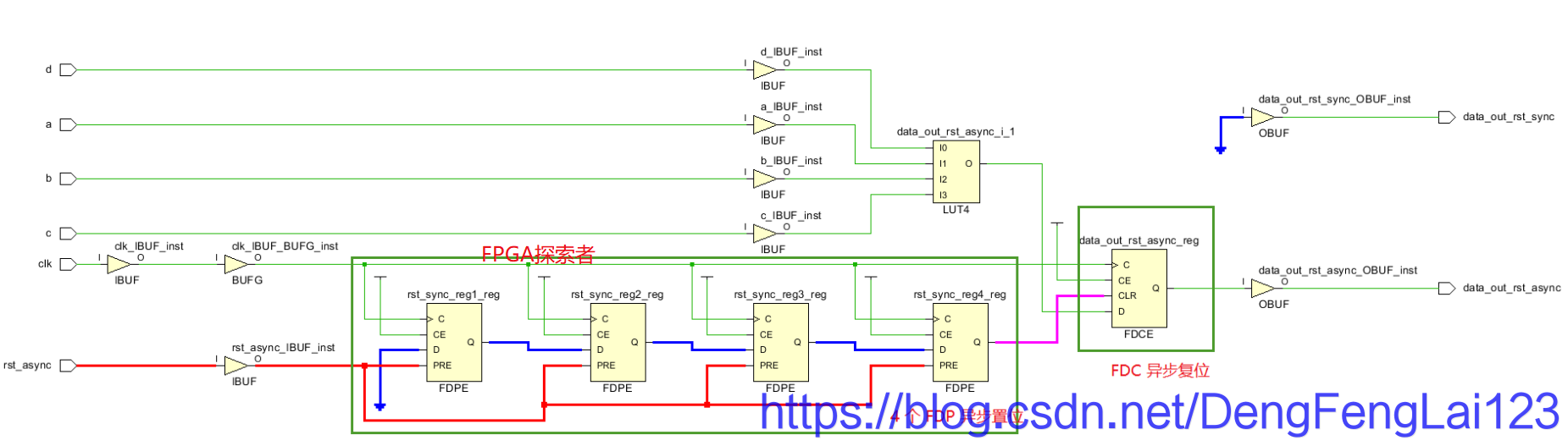

对于输入的异步复位 Asynchronous Reset,首先使用了 4 个触发器来做同步(一般用 2 个即可,4 个出现亚稳态的概率更小),触发器类型为 FDP(异步置位),同步化以后的复位信号去使用时综合出的触发器类型为 FDR(同步复位),即在 Xilinx 中是将 sys_rst 按照方式 2 同步复位使用。

使用 FDP 异步置位的原因是因为 Xilinx 推荐高电平复位,当异步复位信号到来时,输出复位电平“1”,即异步置位 FDP,当复位消失后,D 触发器在每个时钟边沿输出前一级触发器的值,一定周期后,最后一级的 FDP稳定输出“0”。

使用 Xilinx A7 系列 FPGA 实现异步复位、同步释放代码,确定同步化后的复位使用情况。

二、Xilinx复位程序对比

1.将同步化后的复位当作异步复位信号

/****** FPGA探索者 ******/

always @(posedge clk or posedge rst_async)

begin

if(rst_async == 1'b1) begin

rst_sync_reg1 <= 1'b1;

rst_sync_reg2 <= 1'b1;

rst_sync_reg3 <= 1'b1;

rst_sync_reg4 <= 1'b1;

end

else begin

rst_sync_reg1 <= 1'b0;

rst_sync_reg2 <= rst_sync_reg1;

rst_sync_reg3 <= rst_sync_reg2;

rst_sync_reg4 <= rst_sync_reg3;

end

end

wire sys_rst;

assign sys_rst = rst_sync_reg4;

always @(posedge clk)

begin

if(sys_rst == 1'b1) begin

data_out_rst_async <= 1'b0;

end

else begin

data_out_rst_async <= a & b & c & d;

end

end

综合并布局布线后的原理图如图所示,显然,综合后对 sys_rst 复位,将其作为异步复位综合出 FDCE 同步使能异步复位(这里不考虑使能),和白皮书 WP272 给出的参考电路显然不一致。

| 原语(Primitive) | 功能描述 | 原语(Primitive) | 功能描述 |

|---|---|---|---|

| FDCE | 同步使能,异步复位 | FDRE | 同步使能,同步复位 |

| FDPE | 同步使能,异步置位 | FDSE | 同步使能,同步置位 |

2.将同步化后的复位当作同步复位信号

/****** FPGA探索者 ******/

always @(posedge clk or posedge rst_async)

begin

if(rst_async == 1'b1) begin

rst_sync_reg1 <= 1'b1;

rst_sync_reg2 <= 1'b1;

rst_sync_reg3 <= 1'b1;

rst_sync_reg4 <= 1'b1;

end

else begin

rst_sync_reg1 <= 1'b0;

rst_sync_reg2 <= rst_sync_reg1;

rst_sync_reg3 <= rst_sync_reg2;

rst_sync_reg4 <= rst_sync_reg3;

end

end

wire sys_rst;

assign sys_rst = rst_sync_reg4;

always @(posedge clk)

begin

if(sys_rst == 1'b1) begin

data_out_rst_async <= 1'b0;

end

else begin

data_out_rst_async <= a & b & c & d;

end

end

综合并布局布线后的原理图如图所示,显然,综合后对 sys_rst 复位,将其作为同步复位综合出 FDRE 同步使能异步复位(这里不考虑使能),和白皮书 WP272 给出的参考电路一致。

异步复位相比较同步复位,在 Xilinx 的 FPGA 中资源是一致的,异步复位的优势在于复位信号一来就能检测到,不需要保持至少一个时钟周期才能在时钟边沿检测到,通过仿真来验证上述电路是否能实现异步复位一来就能检测到。

三、仿真结果

设置时钟 50 MHz,时钟周期 20 ns,给一个持续时间 3 ns 的异步复位信号,且持续时间均不出现在时钟上升沿检测期间,可以看到:

(1)rst_async 异步复位一旦给出,用于同步的4个寄存器rst_sync_reg1 ~ 4 立刻输出高电平 “1”,在下一个时钟上升沿检测到同步复位并将输出data_out_rst_async 复位;

(2)异步复位信号释放后,经过同步的 sys_rst 经过一定周期后在时钟边沿同步释放;

按照同样的复位,将 sys_rst 看作异步复位,仿真结果如下,相比于上图,区别在于异步复位信号 rst_async 一旦产生,输出立刻复位,且同样是同步释放,好像这种处理才更符合异步复位、同步释放。。。。。。

那么为什么 Xilinx 白皮书还是将 sys_rst 按照同步复位去做的呢?难道写错了?

综合考虑可能有这样的因素:

(1)当作同步复位的差别只在于复位时间会稍晚一些,要在时钟的下一个边沿检测到,但是还是能够识别到输入的 rst_async 异步复位信号,所以从复位角度来说,都能够后实现复位效果;

(2)根据 Xilinx 复位准则,我们知道同步复位相比异步复位有很多好处,具体参见:Xilinx FPGA 复位策略 ,既然两者对后级复位没有功能上的差别,那么优先选择同步复位;

经过异步复位同步释放处理后,相比于纯粹的异步复位,降低了异步复位信号释放导致亚稳态的可能性;相比同步复位,能够识别到同步复位中检测不到的复位信号(如上图所示的 rst_async 在同步复位是检测不到的);综合两者的优势,异步复位同步释放。

四、Altera复位

Altera还是把这个同步后的复位当作异步复位来用的,且推荐低电平复位。

从上面的分析来看,这里当作异步复位还是同步复位对于复位结果本身没有太大的影响,区别在于 Xilinx 是推荐同步复位来节省资源(比如DSP48E或BRAM,异步复位比同步复位耗资源),而 Altera 的 FPGA 中带异步复位的触发器,想要同步复位需要消耗更多的资源。

欢迎关注:FPGA探索者,获取 FPGA 设计、数字信号处理资料