之前介绍了quartus同modelsim的联合仿真,这次介绍ISE/VIVADO和modelsim的联合仿真

ISE和VIVADO的配置方法基本一致,这里我就以ISE为例,ISE没有modelsim的集成安装包,所以要先下载一个modelsim,

我的环境: Windows 10 64 位, Xilinx ISE Design Suite 14.7(D:\Xilinx\14.7), Modelsim SE-64 10.1c

(D:\modeltech64_10.1c)。

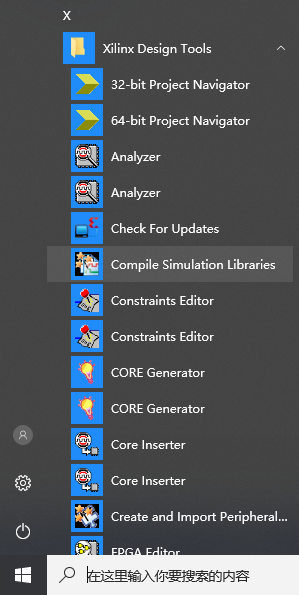

由于我装的 Modelsim SE 是通用版的,只自带了少许的仿真库(Simulation Library),所以还要编译一下 Xilinx 的仿真库。只有 XE 才自带 Xilinx 的仿真库,如果装的是 XE 版便不必编译仿真库了。编译库可以用 ISE 带界面的工具,也可以用命令行下的,这里只讲前者,如果想用前者,可以自己百度,其实两者原理都是一样的。打开编译库工具“Simulation Library Compilation Wizard”:win 7打开方法“开始—所有程序—Xilinx ISE Design Suite 14.7(版本不同就不同) —ISE Design Tools—64-bit Tools(32 位的选 32-bit Tools) —Simulation Library Compilation Wizard”。

Win10打开方法如下图

打开工具之后,在“Select Simulator”下面选中你所装好的 Modelsim 版本,我这儿选“Modelsim SE”,在“Simulator Executable Location”下面填入 Modelsim.exe 的所在的文件夹,点“Browse…”按钮添加也行,我这儿是“D:\modeltech64_10.1c

\win64”(不含双引号,下同,除非有特别的说明),下图,

然后 Next。

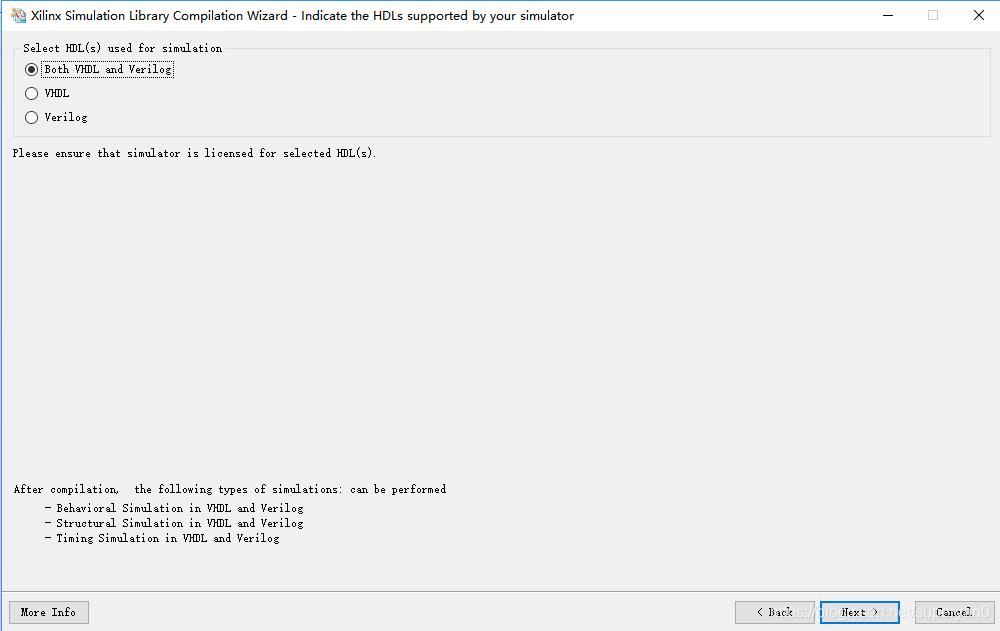

之后是选择需要编译的语言,选“Both VHDL and Verilog”,一般两种都要用,如图,然后 Next。

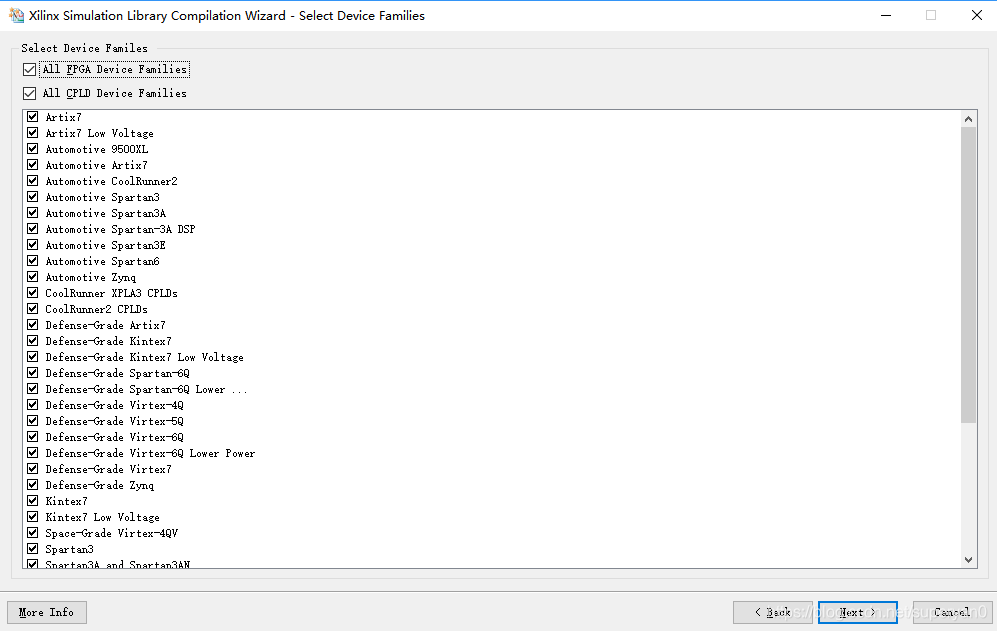

接下来是选择设备,默认是全选,如果有一些你实在用不上就不选吧,这样可以省点时间和硬盘空间,如图,还是 Next。

下一步默认就行,全选上,下面的两行留空,那是添加额外库的, Next。

这一步比较关键,在“Output directory for compiled libraries”下面填入输出已编译库的路径,默认也行。个人建议新建一个单独的文件夹,好管理,只要版本一样的,下次直接拿来用,重装也不怕。不过 文 件 夹 的 名 字 和 整 个 路 径 中 绝 对 不 能 有 中 文 或 空 格 , 切 记 、 切 记 !!! 我 这 儿 是 “D:\modeltech64_10.1c\Xilinx_lib”。其他的选项默认便可,之后点“Launch Compiled Process”,如图。

之后就开始编译了等待编译完后就会出现一些编译日志,Next, Finish。只要没有 Err 就成, Warn 无视。若有 Err,就回顾下版本对不对,路径有没有中文或空格。

下面设置 ISE 和 Modelsim 的关联。在“D:\Xilinx\14.7\

ISE_DS\EDK”文件夹中找到“modelsim.ini”,“D:\Xilinx

\14.7”这个是你的 ISE 安装目录,实在不行就进入安装目录然后搜索 “modelsim.ini”,

打开“modelsim.ini”,用记事本打开时不要用自动换行功能,菜单中“格式—自动换行”把勾去掉。

找到“[Library]”,下面一行的“others = $MODEL_TECH/../modelsim.ini”和行的开头的分号(;)

的全部都无视。那些行开头没有分号的,格式一般是“X···X = 路径”,一直到“[vcom]”之上的都要,全部复制。

然后在 Modelsim 的安装目录下,我这儿是“D:\modeltech64_10.1c”,找到“modelsim.ini”,名字一样。

先去换个文本编辑工具吧,用记事本打开它会是乱糟糟的一片,没法改。打开后,同样是找到“[Library]”,

在它的下面粘贴上刚刚复制的那一大段东西,注意,行开头不要有分号(;),而且人家原有的就别动

它,别删掉了。只要在“[Library]”和“[vcom]”之间粘贴就行,然后保存。

打开 ISE,“开始—所有程序—Xilinx ISE Design Suite 14.7(版本不同就不同)—ISE Design Tools—64-bit

Project Navigator”,

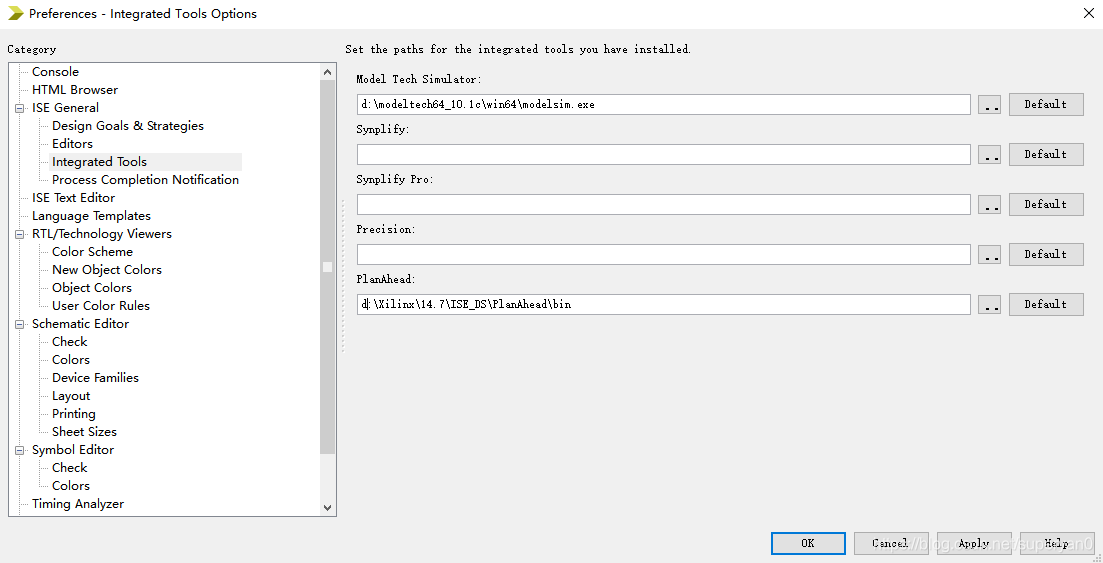

然后在 ISE 的菜单上“Edit—Preferences…”调出 Preferences 设置窗口,在左边的“Category”下选中“ISE

General—Integrated Tools”。在 Integrated Tools 项设置中,右边的“Model Tech Simulator:”下面填入Modelsim.exe 的 文 件 路 径 , 点 旁 边 的 “.. ” 按 键 选 中 Modelsim.exe 也 行 ,

我 这 儿 是 “ D:\modeltech64_10.1c\win64\modelsim.exe ”( 不 要 双 引 号 ) 。如图。

到现在已经准备好了,接下来就是使用它了。新建一个工程,就不多说了,注意在“Simulator”一项选“Modelsim-SE Mixed”,“Mixed”支持两语言,“SE”是版本,选你自己对应的就成。

忘了选或想重新选的在Project –Design Properies…重新配置。

新建你的 VHDL 或 Verilog 文件,这个不多说。 如果是 VHDL 文件,则要打开两个库。 在菜单上“Edit—Preferences…”调出 Preferences 设置窗口,选中“Category”下面的“ISE Text Editor”,之后在右边“ISE Text Editor”设置中下面的那个大白框里有四行代码,把后面两行,“use IEEE.STD_LOGIC_ARITH.ALL;”

和“use IEEE.STD_LOGIC_UNSIGNED.ALL;”复制一下,然后粘贴在你的 VHDL 文件的库声明中,也就是打开这些库。完成之后,切换到仿真模式,就是点工程上面的“Simulation”,可能不同版本会不一样, ISE9.1i 是在 “Source for” 的下拉菜单中选择 Behavioral simulation, 不过意思明白就行。 建立 Test Bench 文件, 若

是 VHDL 的, 也按上面说的处理一下,就是把那两个库声明一下。在“Hierarchy”框选中 Test Bench 文件,在下面的那个框中点“Modelsim Simulator”前的加号。展开得到“Simulate Behavioral Model”,在它上面点右键,选“Process Properties…”,如图 27。这里如果直接选“Run”可能会出现如图 28 的警告,如果不出现警告而且能调用 Modelsim 仿真,那恭喜你成功了,不然就接着看吧。有警告时,如果前面的设置没问题,直接点“No”就可以用 Modelsim 仿真了。为了搞定这个警告,咱们接着整。把"D:\modeltech64_10.1c\modelsim.ini"复制到你所建的工程目录下也能搞定这个警告,不过这样太麻烦,每次都得复制,还是往下看吧。选“Process Properties…”后弹出 Process Properties

设置窗口,在右边的“Compiled Library Directory”后面填入之前编译库时设置的已编译库的路径,点旁边的“…”按钮来选定也行。如果编译库时使默认的路径,那这里就不用改了,不过得把下面的“Ignore Pro-Compiled Library Warning Check”给勾上,不然也可能有警告,反正我用默认路径时就是有警告,不知道为什么。其实只要你前面设置的正确了,这里直接把“Ignore Pro-Compiled Library Warning Check”给勾上,路径都不设也是可以的,搞定后点“Ok”。

在“Simulate Behavioral Model”上点右键,选“Run”就可以调用 Modelsim 进行仿真了。