版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/vivi_and_qiao/article/details/85346421

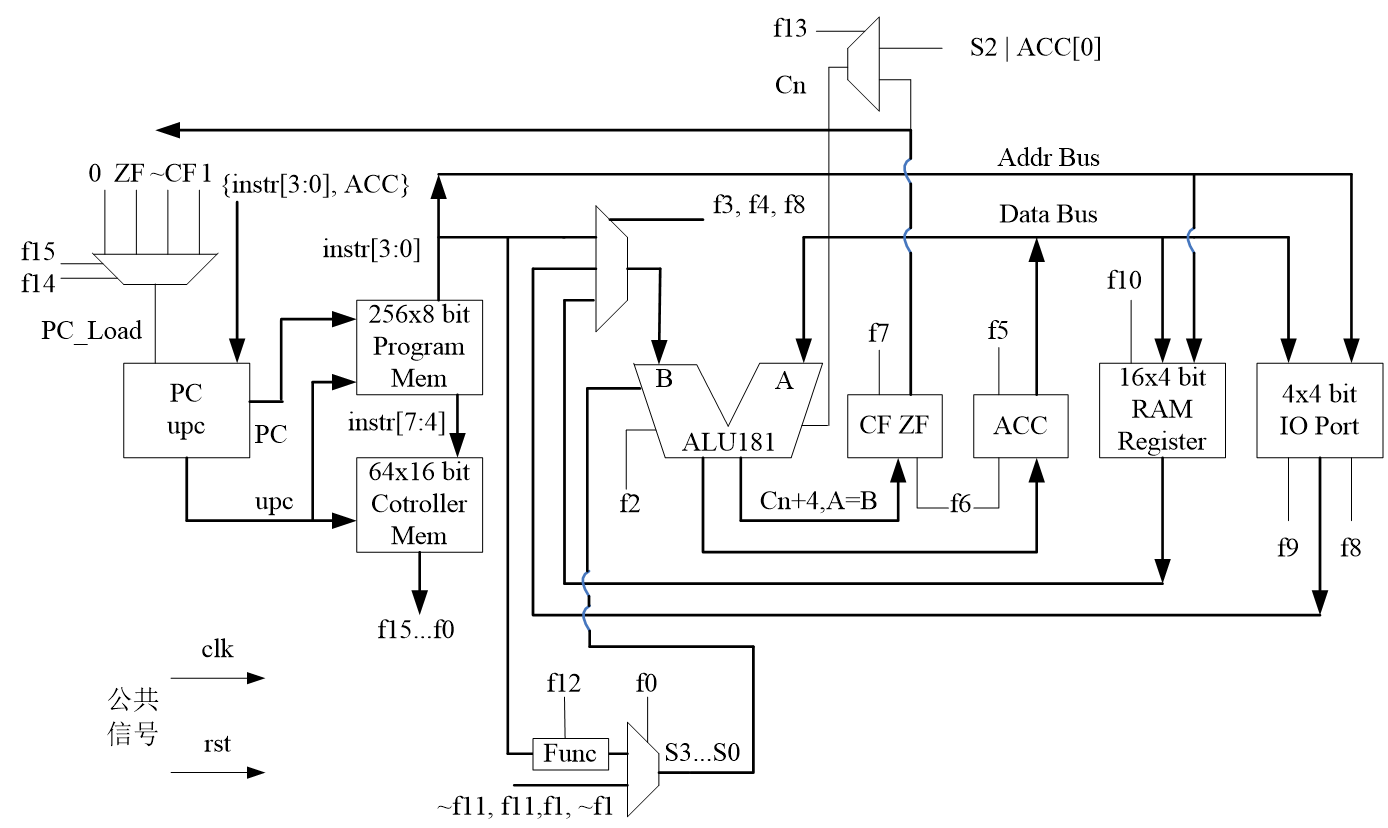

理解简单模型机的工作原理,理解程序计数器,算数逻辑运算单元,控制单元,的工作原理。学会设计以及使用指令完成一定的功能,并将程序写入FPGA开发板并结合led灯数码管予以显示。

通过模型机设计可以掌握用verilog来硬件描述电路,掌握modlesim的仿真与调试,掌握基于ISE开发的基本流程

整个模型机modelsim模型仿真以及通过ISE软件上位机在FPGA上实现模型机的算数逻辑运算和流水灯,以及竞赛报告答辩ppt,及其演示视频的完整项目打包文件请点击以下链接:

https://www.fageka.com/i/WDmVhPq0405

整体功能----划分为9个子功能,协同完成。子功能对应子模块。

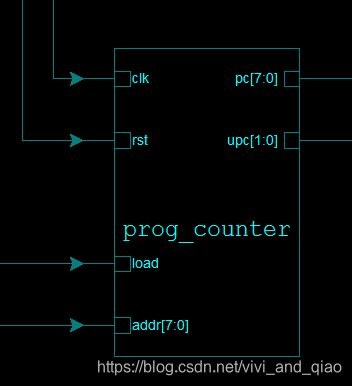

①Prog_counter模块

②Prog_memory模块

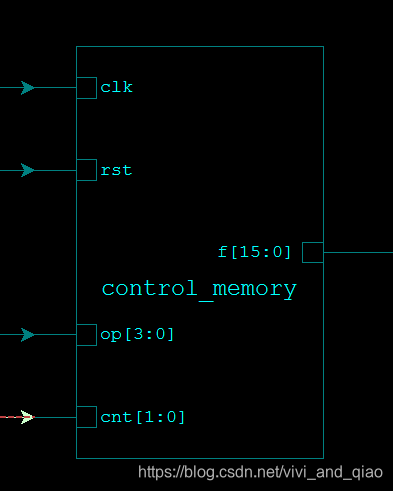

③Control_memory模块

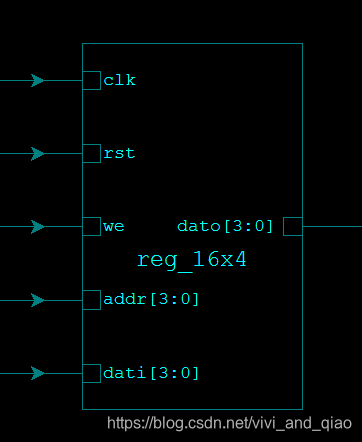

④Reg_16x4模块

⑤Acc模块

⑥Alu_flag模块

⑦Alu_function模块

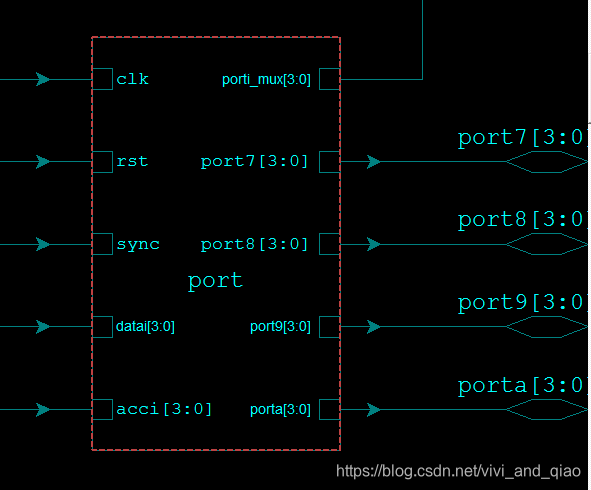

⑧Port模块

⑨Alu_74181模块

1. 模型机构成图:

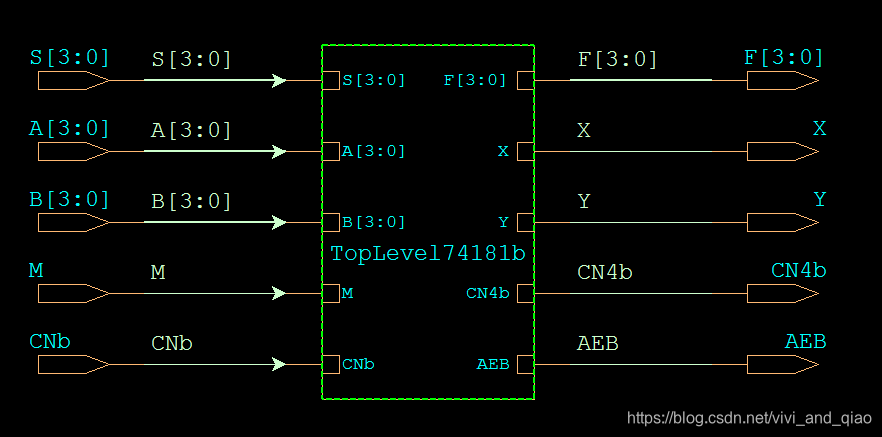

2. 算术逻辑运算器ALU的设计:

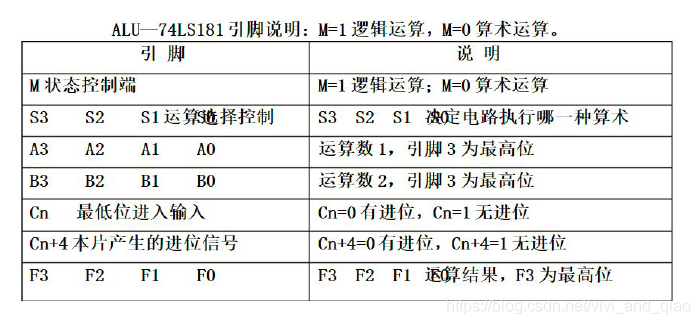

3. ALU-74LS181引脚说明:

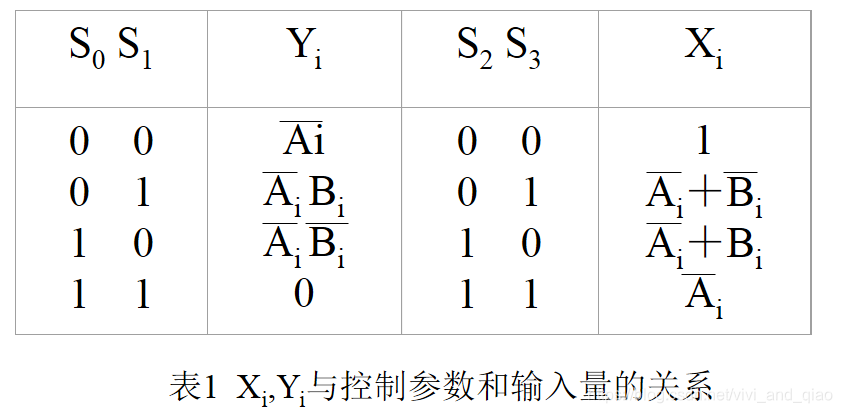

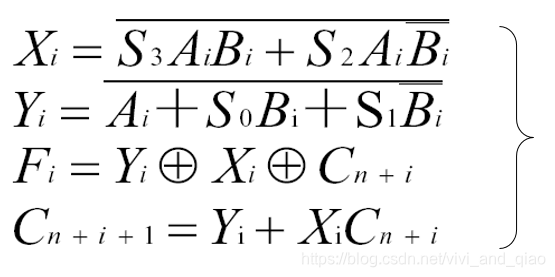

4. 逻辑表达式:

5. 进一步化简可得ALU的一位逻辑表达式如下:

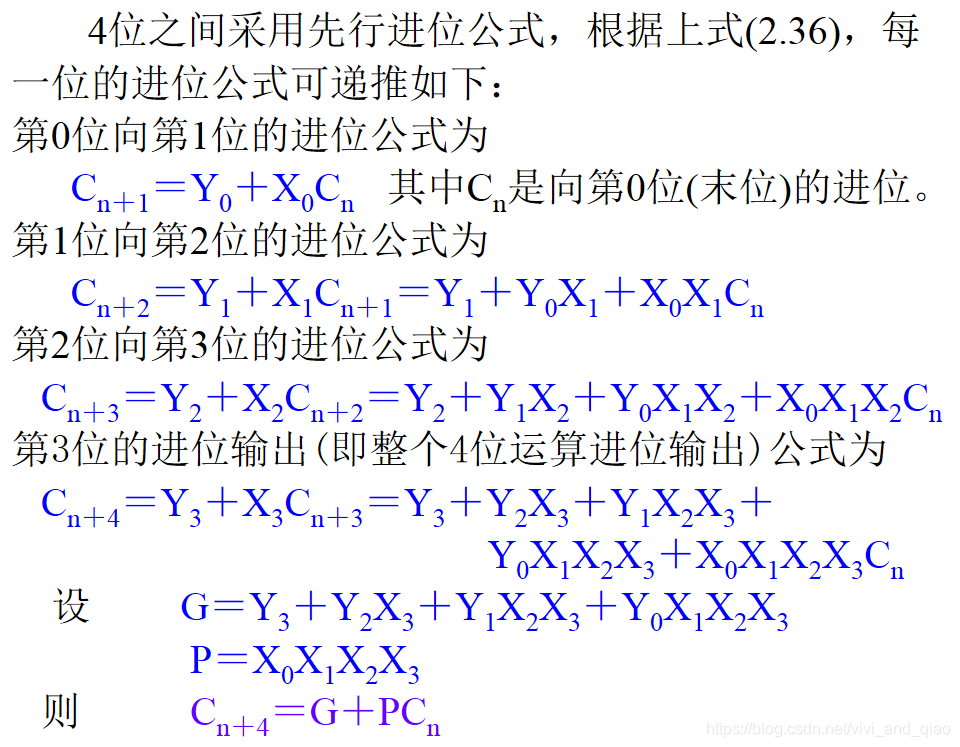

6. 4位之间采用先行进位公式:

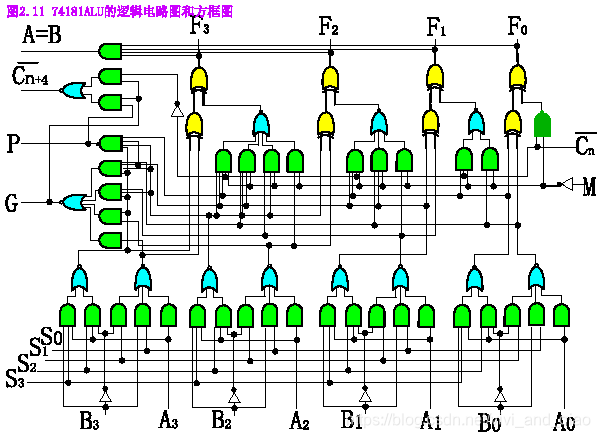

7. 用正逻辑表示的4位算术/逻辑运算单元(ALU)的逻辑电路图:

8. 4位的ALU74LS181运算功能发生器算数运算和逻辑运算:

9. 微指令和微程序的详细设计:

10. 存储器设计:

11. IO端口设计:

12. 程序计数器设计:

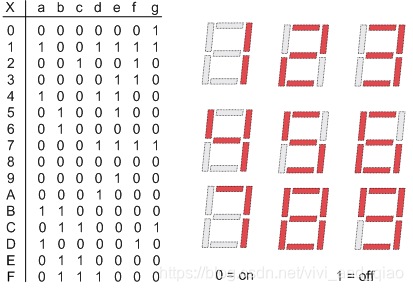

13. 数码管设计:

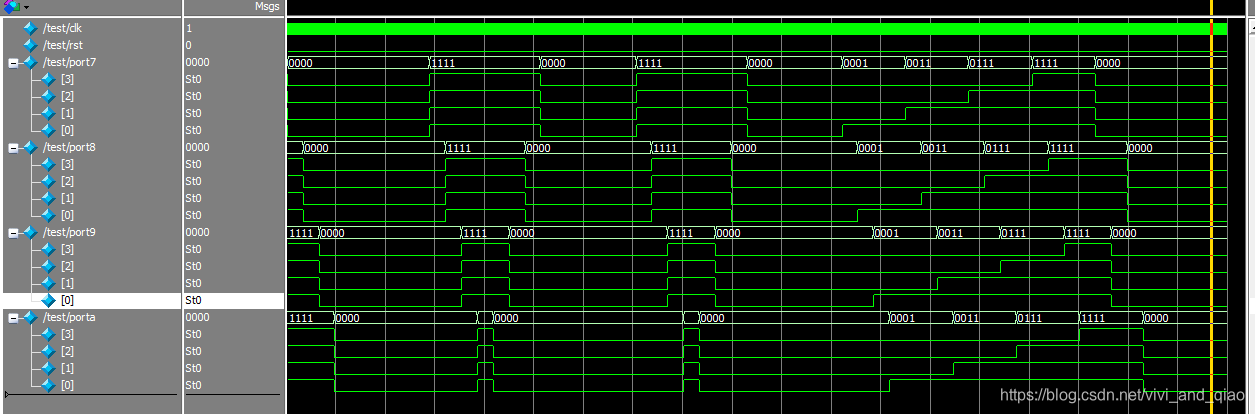

14. 顶层综合仿真记录:

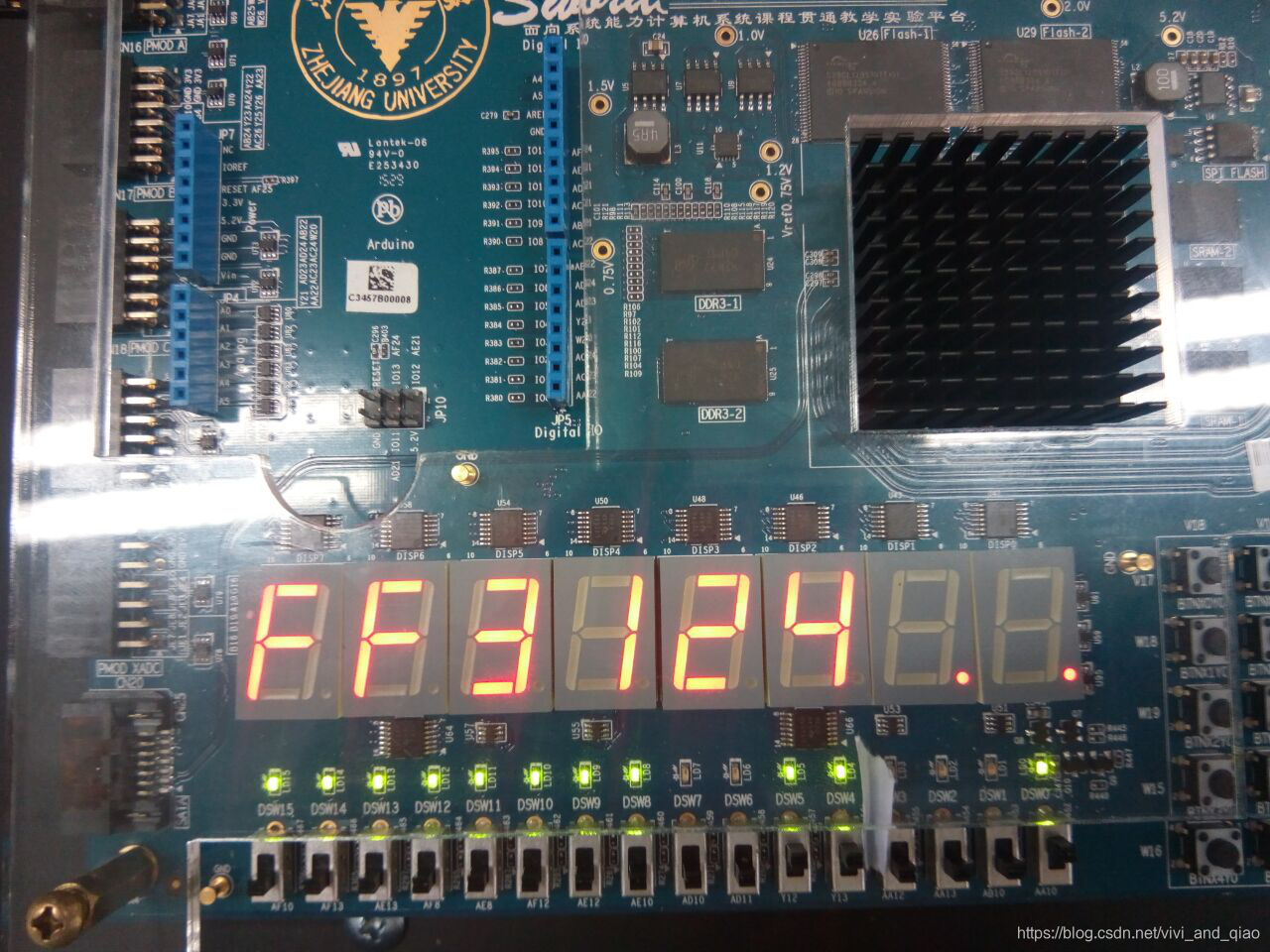

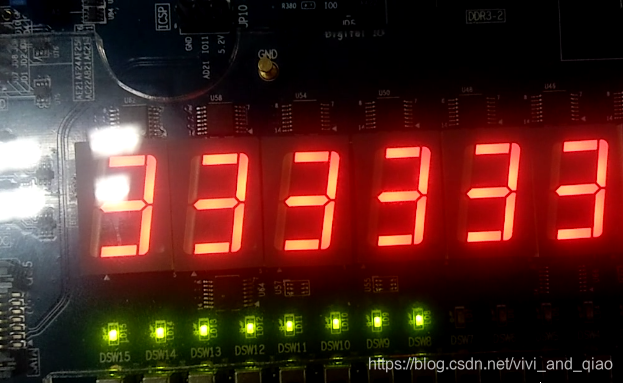

15. 运行结果截图:

74LS181代码实现:

`timescale 1ns/1ns

`include "./define.v"

module alu_74181 (S, A, B, M, CNb, F, X, Y, CN4b, AEB);

input [3:0] A, B, S;

input CNb, M;

output [3:0] F;

output AEB, X, Y, CN4b;

TopLevel74181b Ckt74181b (S, A, B, M, CNb, F, X, Y, CN4b, AEB);

endmodule /* Circuit74181b */

/*************************************************************************/

module TopLevel74181b (S, A, B, M, CNb, F, X, Y, CN4b, AEB);

input [3:0] A, B, S;

input CNb, M;

output [3:0] F;

output AEB, X, Y, CN4b;

wire [3:0] E, D, C, Bb;

Emodule Emod1 (A, B, S, E);

Dmodule Dmod2 (A, B, S, D);

CLAmodule CLAmod3(E, D, CNb, C, X, Y, CN4b);

Summodule Summod4(E, D, C, M, F, AEB);

endmodule /* TopLevel74181b */

/*************************************************************************/

module Emodule (A, B, S, E);

input [3:0] A, B, S;

output [3:0] E;

wire [3:0] ABS3, ABbS2;

assign ABS3 = A&B&{4{S[3]}};

assign ABbS2 = A&~B&{4{S[2]}};

assign E = ~(ABS3|ABbS2);

endmodule /* Emodule */

/*************************************************************************/

module Dmodule (A, B, S, D);

input [3:0] A, B, S;

output [3:0] D;

wire [3:0] BbS1, BS0;

assign BbS1 = ~B&{4{S[1]}};

assign BS0 = B&{4{S[0]}};

assign D = ~(BbS1|BS0|A);

endmodule /* Dmodule */

/*************************************************************************/

module CLAmodule(Gb, Pb, CNb, C, X, Y, CN4b);

input [3:0] Gb, Pb;

input CNb;

output [3:0] C;

output X, Y, CN4b;

assign C[0] = ~CNb;

assign C[1] = ~(Pb[0]|(CNb&Gb[0]));

assign C[2] = ~(Pb[1]|(Pb[0]&Gb[1])|(CNb&Gb[0]&Gb[1]));

assign C[3] = ~(Pb[2]|(Pb[1]&Gb[2])|(Pb[0]&Gb[1]&Gb[2])|(CNb&Gb[0]&Gb[1]&Gb[2]));

assign X = ~&Gb;

assign Y = ~(Pb[3]|(Pb[2]&Gb[3])|(Pb[1]&Gb[2]&Gb[3])|(Pb[0]&Gb[1]&Gb[2]&Gb[3]));

assign CN4b = ~(Y&~(&Gb&CNb));

endmodule /* CLAmodule */

/*************************************************************************/

module Summodule(E, D, C, M, F, AEB);

input [3:0] E, D, C;

input M;

output [3:0] F;

output AEB;

assign F = (E ^ D) ^ (C | {4{M}});

assign AEB = &F;

endmodule /* Summodule */