第一题

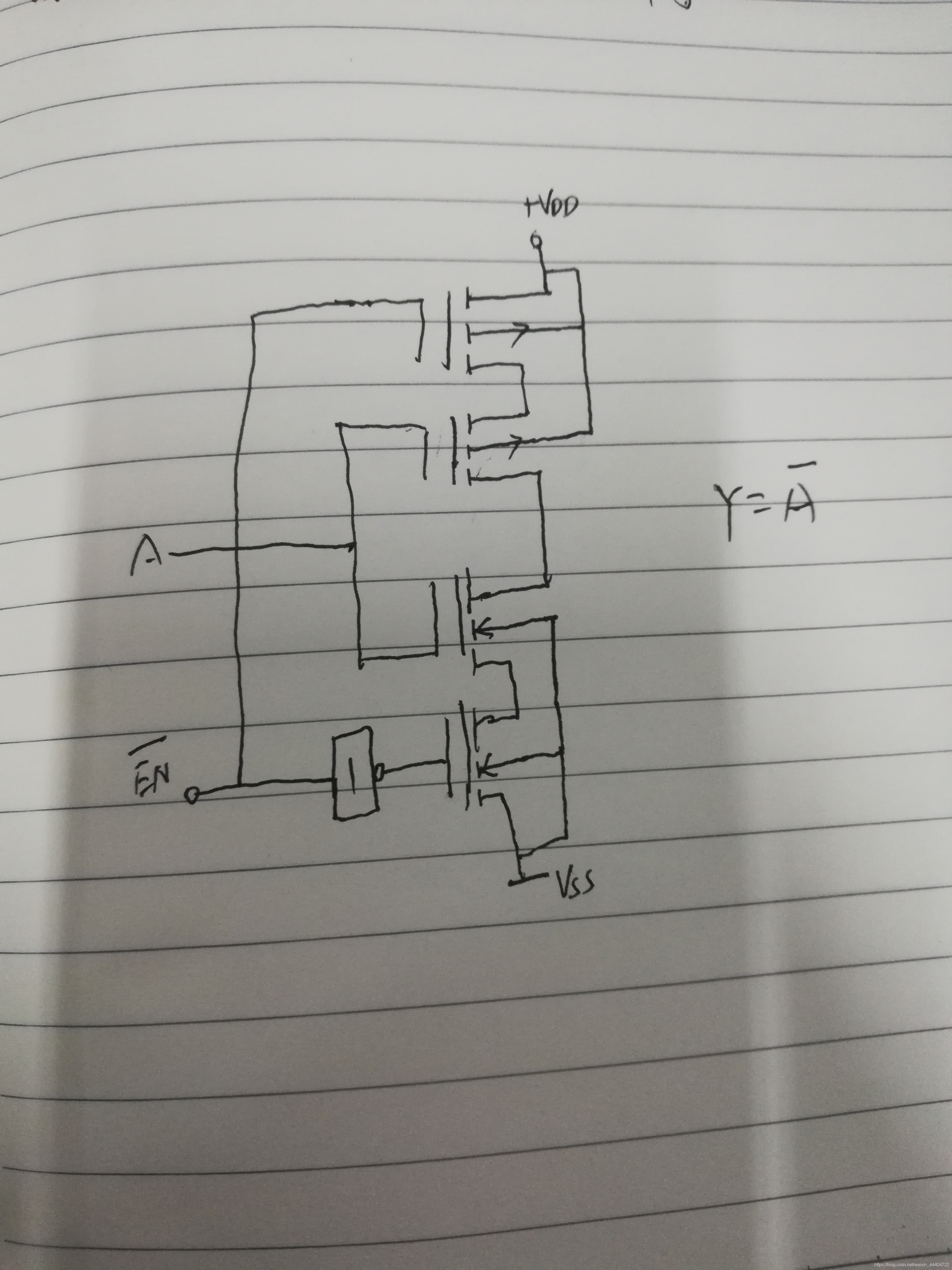

三态门电路

第二题

建立时间:是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这时钟上升沿被稳定的传入触发器,tsu就是最小的稳定时间;

保持时间:是指触发器的时钟信号上升沿到来后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的传入触发器,th就是指这个最小的保持时间(类似于输出延时)

第三题

在cmos电路中,静态功耗主要是漏电流引起的功耗,对于常规cmos电路,在稳定时不存在直流导通电流,理想情况下静态功耗为0(因为对于cmos电路本身,由于mos管的对称性,nmos和pmos中总有一个处于截止状态,所以从VDD到地之间电流为0),但是由于漏电流的存在,使得cmos电路的静态功耗并不为0。

第四题

A B Cin Sum Cout

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fulladder is

port{A,B,Cin:in std_logic;

Sum,Cout:out std_logic};

end fulladder;

architecture full of fulladder is

begin

process(A,B,Cin) begin

if (A=‘0’ and B=‘0’ and Cin=‘0’ ) then

Sum<=‘0’;

Cout<=‘0’;

elsif(A=‘0’ and B=‘0’ and Cin=‘1’ ) then

Sum<=‘1’;

Cout<=‘0’;

elsif…

else

Sum<=‘1’;

Cout<=‘1’;

end if;

end process;

end full;

第五题 状态机设计四路选择器

entity foursel is

port{d0,d1,d2,d3 : in std_logic;

shuchu: out std_logic};

end foursel;

architecture four of foursel is

type state is (s0,s1,s2,s3);

signal presentstate,nextpresentstate : state; --定义信号链接各个状态

begin

process(x,d0,d1,d2,d3) begin

case presentstate is

when s0=> shuchu<=d0;

when s1=> shuchu<=d1;

when s2=> shuchu<=d2;

when s3=> shuchu<=d3;

when other=>null;

end case;

end process;

szuEDA复试第三套

猜你喜欢

转载自blog.csdn.net/weixin_44404722/article/details/88407868

今日推荐

周排行