1、数制转换

R进制数转换为十进制数:按权展开,相加

十进制数转化为R进制数:整数部分,除R取余法,除到商为0为止。小数部分,乘R取整法,乘到积为0为止。

二进制数转化八进制数:三位一组,整数部分左边补0,小数部分右边补0。反之亦然。

二进制数转化十六进制数:四位一组,整数部分左边补0,小数部分右边补0。反之亦然。

2、什么是竞争和冒险?如何消除?

之前写过类似的系列文章,参考自《FPGA之道》:竞争

如果在某一个时刻,从组合逻辑的某一个输入端到其输出端存在两条以上的电信号通路时,就称该组合逻辑在当前状态下针对这个输入端存在竞争。

举例:

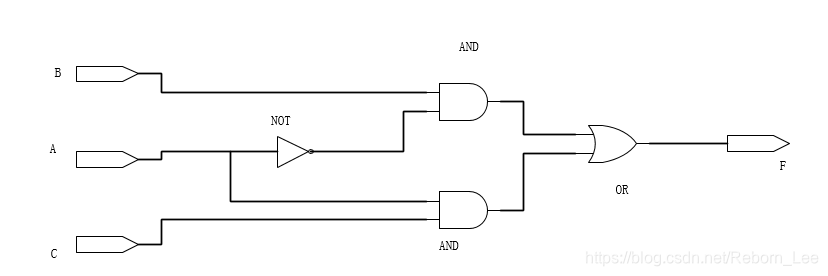

当B=1、C=1时,电路可以化简为:

输入为A先于not(A)A非到达或门,因此,如果初始令A为1,则NOT(A)为0,之后A变化为0,则由于A先到或门,导致有一小段零脉冲出现在输出中,这是非预期的。

信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,FPGA设计中最简单的避免方法是尽量使用时序逻辑同步输入输出。

在FPGA中消除险象的方法:

后向消除中最具有代表性的方法就是时序采样法,在消除险象的各种方法中,时序采样法的使用最为广泛。可以说,只要你描述的是一个时序逻辑,你就已经有意或无意的使用了时序采样法来消除险象。

时序采样法几乎是万能的,因为对于任何一个组合逻辑来说,其输入与输出之间总存在一个最大延迟的路径。设这个最大的路径延迟为T,如果其输入在0时刻变化一次后就保持不变,那么T时刻后,其输出肯定会稳定到新输入应该对应的输出上,而在0到T时刻之间,该组合逻辑的输出可能会出现一系列不稳定现象。

因此,如果该组合逻辑是同步逻辑的一部分,那么我们只需要适当选择周期大于T的信号作为时钟就可以绕过0到T这段有问题的时刻,而采样到T时刻以后的稳定且正确的输出。并且由于每次组合逻辑的输入改变后都会在接下来至少T时刻以上的时间保持不变,因此也能保证输出具有足够的时间达到稳定。

由此可见,时序采样法的最大优点就是根本不关心组合逻辑的内容,因此适用面非常广。

---------------------

作者:李锐博恩(Reborn)

来源:CSDN

原文:https://blog.csdn.net/Reborn_Lee/article/details/84503277

版权声明:本文为博主原创文章,转载请附上博文链接!

3、用D触发器带同步高置数和异步高复位端的二分频的电路,画出逻辑电路,Verilog描述。

reg Q;

always @(posedge clk or posedge rst)begin

if(rst == 1'b1)

Q <= 1'b0;

else if(set == 1'b1)

Q <= 1'b1;

else

Q <= ~Q;

end用Quartus生成RTL电路图:

尝试过用ISE生成,可是ISE唯一一点让我不满意的就是这个图的生成,看起来很让人眼花缭乱,不简洁:

当然,生成的原理图是一模一样的,只是元件风格问题。Quartus更接近于手写。

为了比较也是拼了,Vivado生成的原理图也比较简洁:

看来还是得用Vivado呀,可是一些芯片,vivado还不支持!支持一些高大上的芯片。