版权声明:本博客内容来自于个人学习过程中的总结,参考了互联网、数据手册、帮助文档、书本以及论文等上的内容,仅供学习交流使用,如有侵权,请联系,我会重写!转载请注明地址! https://blog.csdn.net/Reborn_Lee/article/details/87989388

1、什么是高阻态?

高阻态:电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

之前写过和高阻态相关的博文:https://blog.csdn.net/Reborn_Lee/article/details/83756121

2、集成时钟门控单元(Integrated Clock Gating Cell)

门控时钟之前也写过相关博文:门控时钟专题

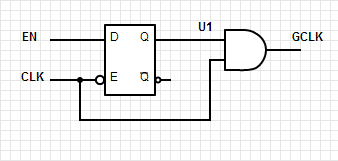

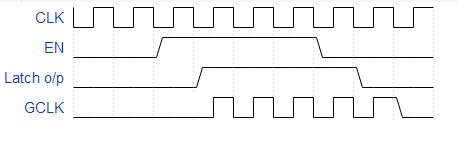

时钟门控是一种通过时钟使能信号关闭模块时钟来降低时钟功耗的常用技术。时钟门控功能仅需要一个AND或OR门。 考虑你正在使用带时钟的AND门。 高EN边沿可能随时出现,可能与时钟边沿不一致。 在这种情况下,AND门的输出将比时钟占空比的时间短1。 您最终会在时钟信号中出现毛刺。

为避免这种情况,使用了一种特殊的时钟门控单元,它使EN与时钟边沿同步。 这些叫集成时钟门控单元或ICG。

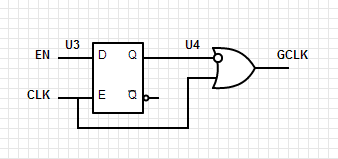

通常有两种类型的实现方式:

而如下链接给出的方法貌似用的是触发器:http://vlsi.pro/integrated-clock-gating-cell/

与门实现方式:

或门实现方式:

最后总结一句,使用门控时钟,可以降低功耗,因为只有在En有效范围内提供时钟。