一:可侧性设计简介(DFT)

1:什么是可测性?

相当于debug中给程序段加入断点。

设计工具自动将扫描插入到设计中,在设计通过仿真后,在设计阶段的后期,扫描被插入到设计中。扫描的目的是未来观察一个设计或者是整个芯片的内部变化。

2:JTAG

用一组特别的测试端口来控制扫描操作,这组端口被称为JTAG。

二:简单扫描举例

我们在实战一中加入扫描链

1:在Intro_Top中加入JTAG测试端口,加入5个1比特端口,先不连接它们,这5个端口分别是:ScanMode,ScanIn,ScanOut,ScanClr,ScanClk

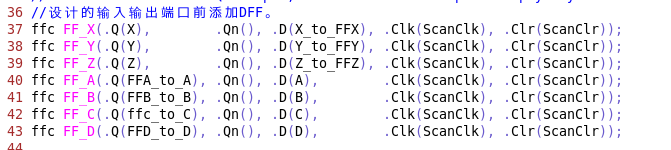

2: 在Intro_Top(顶层设计)中的每一个I/O路径都插入D触发器,但JTAG的I/O除外

3:在testbench里给ScanClk和ScanClr添加驱动,即赋值

以上即可简单实现扫描链,也简单呈现了扫描链的大致情况,下面是拓展

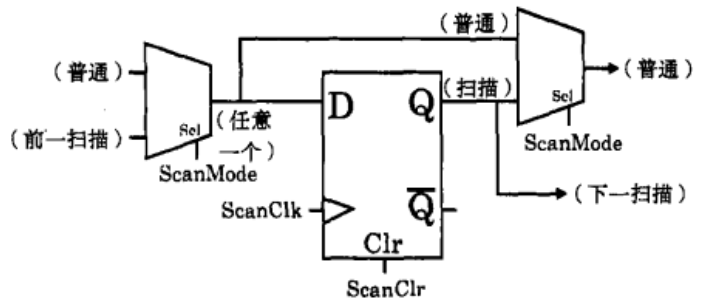

4:加入多路选择器来去除所有的同步行为,一个ff寄存器上被加上了两个多路选择器