最近做项目卡住了,仿真已经通过了,可是将程序下载到板子调试时,chipscope中获取信号时,所有信号一直保持高或者低,没有任何变化。后来查资料知道,我只做了功能仿真,没有做时序仿真,可能还有没有发现的问题。事实证明,每个仿真都需要做。

一、前言

FPGA设计验证包括功能与时序仿真和电路验证。

功能仿真是指仅对逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计的要求。仿真过程中没有加入时序信息,不涉及具体器件的硬件特性,如延时特性等,因此也叫前仿真。它是对HDL硬件设计语言的功能实现能力进行仿真,以确保HDL语言描述能够满足设计者的最初意图。

时序仿真则是在HDL可以满足设计者功能要求的基础上,在布局布线后,提取有关的器件延迟、连线延时等时序参数,并在此基础上进行的仿真,因此,也称为后仿真,它是接近真实器件运行的仿真。

我使用的是ISE_14.7,集成MODELSIM_10.1a。仿真的方法分为直接和间接两种。直接是指从ISE 上起动MODELSIM。间接是单独起动MODELSIM,然后使用ISE 生成的用于仿真的文件夹netgen。

下面分别介绍功能仿真和时序仿真,本文只介绍直接从ISE上启动MODELSIM。本文参考的实例为之前的博文《verilog实现中值滤波》。

二、功能仿真

1、建立工程

此步骤不再详细描述,可参考文件《黑金Sparten6开发板Verilog教程V1.5》第四部分 LED流水灯例程。该部分详细介绍从新建一个项目, 建立仿真文件,从ISE中启动ModelSim进行功能仿真以及到最后下载到FPGA的全过程。像我这样的小白可以通过学习这部分,对如何使用FPGA进行一个简易项目的开发,有个直面的感性认识。

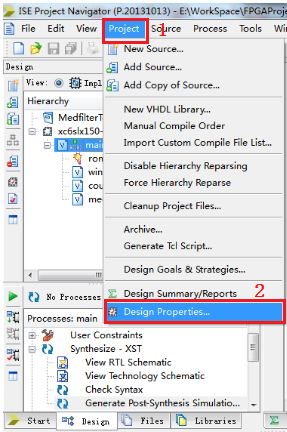

2、在用Modelsim仿真前,在ISE中需要确认一下设置,点击菜单的“Project->Design Properties…”。

3、如下图所示,确认这里“Simulator”的选择为“Modelsim-SE Mixed”,这在新建工程时我们已经设定好了,为保万无一失,我们还是确认一下。

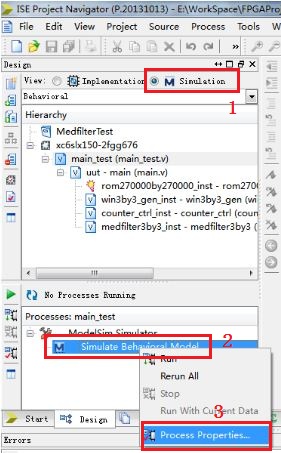

4、先切换到Simulation模式, 再选中main_test.v文件, 最后右键选择Simulate Behavioral Model后选择Process Properties..。

5、弹出“Process Properties”设置窗口,在右边的“Compiled Library Directory”后面填入之前编译库时设置的已编译库的路径“C:\Xilinx\Xilinx_lib”。这个在Xilinx的安装路径下。其他选项默认设置即可,点击“OK” 完成设置。

6、接下去我们开始写测试脚本文件,右击main.v->New Source...

7、如图所示,选择新建源文件类型是“Verilog Test Fixture”,再输入测试脚本文件的名字和存放目录。

8、这里“Associate Source”是选择测试脚本对应的设计源文件,如果工程中有多个设计源文件,可以选择任意一个设计源文件进行仿真。这里我选择的是顶层模块的设计源文件main.v,对整个工程进行仿真我们只有一个设计源文件,然后点击“Next”。下一个界面点击“finish”,即完成仿真文件的创建。

9、这里的测试脚本只是一个基本的模板,它把设计文件mian_test的接口在这个模块里面例化申明了,我们还需要自动动手添加复位和时钟的激励。完成后的脚本文件如下:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 16:45:09 10/17/2018

// Design Name: main

// Module Name: E:/WorkSpace/FPGAProject/ImageProcessingTest/main_test.v

// Project Name: ImageProcessingTest

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: main

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module main_test;

/***输入端口Inputs在测试文件中的数据类型为reg***/

// Inputs

reg CLK;

reg RSTn;

reg Start_sig;

/***定义计数器,记录存储的像素个数100*100=10000=10,0000,0000,0000***/

reg [13:0] pix_cnt;

/***输出端口Outputs在测试文件中的数据类型为wire***/

// Outputs

wire Done_sig;

wire [7:0] Data_out;

/***定义整型变量fouti***/

integer fouti;

// Instantiate the Unit Under Test (UUT)

main uut (

.CLK(CLK),

.RSTn(RSTn),

.Start_sig(Start_sig),

.Done_sig(Done_sig),

.Data_out(Data_out)

);

initial begin

// Initialize Inputs

CLK = 0;

RSTn = 0;

Start_sig = 0;

fouti = $fopen("medfilter2_re.txt");//@@@

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

/***添加复位信息***/

RSTn = 0;

Start_sig = 1;

pix_cnt = 0;

#100;

// To start the syste

RSTn = 1;

pix_cnt = 1;

end

/***添加时钟激励***/

always #10 CLK = ~CLK;

/***计数***/

always@(posedge CLK)

begin

if(Done_sig)

pix_cnt <= pix_cnt + 1;

end

/***通过计数停止仿真***/

always@(posedge CLK)

begin

if(pix_cnt == 14'd10001)

begin

Start_sig <= 0;

$display("Image Medfilter Completed!\n");

$display("The all time is %d \n",$time);

$stop;

end

end

/***将结果数据Data_out写入txt文档中***/

always@(posedge CLK)

begin

if(Done_sig)

begin

$fwrite(fouti, "%d", Data_out, "\n");

$display("%d",pix_cnt);

end

end

endmodule10、保存后main_test.v已经成了这个仿真的顶层了,它下面是设计文件main.v。我们选择仿真模式Behavioral(行为仿真),然后选中main_test.v文件,随后双击“Simulation Behavioral Model”,随后Modelsim将被调用,启动仿真。

11、弹出Modelsim后,我们可以打开Wave查看。如果想添加信号到Wave中查看,点击uut,在Name窗口下选择要添加的信号,例如rom_data,右击选择Add Wave,随后就可以在Wave窗口中观察rom_data信号。

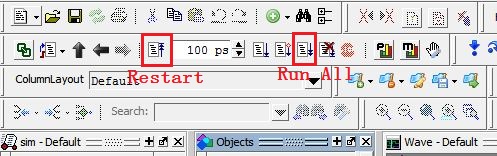

12、点击Restart按钮复位一下,再点击Run All按钮。Modelsim会运行到$stop的地方。

补充:每次添加信号比较麻烦,可以点击“save Format”, 将添加好的信号保存,方便下次使用。

点击"File",选择"Open",打开文件“wave.do”。如下图所示。

在“wave.do”文件中,复制下图蓝色部分的语句,在命令行窗口运行这些语句,即可将之前保存的信号添加到wave窗口中。

三、时序仿真

时序仿真一共有四类:

第一类:综合(Synthesize),综合后可生成综合后仿真模型(Generate Post-Synthesis Simulation Model)。

在Implementation状态下,点击Synthesize-XST下Generate Post-Synthesis Simulation Model。

第二类:实现(Implement)中的翻译(Translate),生成Generate Post-Translate Simulation Model。

第三类:实现(Implement)中的映射(Map),生成Generate Post-Map Simulation Model。

第四类:实现(Implement)中的布局布线(Place&Route),生成Generate Post-Place&Route Simulation Model。

综合后,进行ISE的实现(Implement),包括翻译、映射、布局布线。在这三个过程中都可以生成一个仿真模型,翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真。下面讲解如何使用布局布线后产生的仿真模型进行时序仿真。

1、启动Modelsim仿真

生成仿真模型之后,切换到"Simulation"模式,选择“Post-Route”,然后双击ModelSim Simulator下Simulate Post-Place & Route Model,随后Modelsim启动。

2、如何编写仿真文件及如何使用Modelsim观察信号变化,同功能仿真。

四、参考资料

1、《黑金Sparten6开发板Verilog教程V1.5》

链接:https://pan.baidu.com/s/17Ubnroqc3oNEXt_W2XkXgg

提取码:1m7m

2、《用ISE 与Modelsim 进行FPGA 后仿真(时序仿真)的两种方法》

链接:https://pan.baidu.com/s/1w3msgwOHQX0LIkg1nk4yqg

提取码:bv41

3、《FPGA应用开发入门与典型案例》