并行数据的并行转串行

主要设计思路

Y: y0 y1 y2 y3 y4 y5 y6

C: c0 c1 c2 c3 c4 c5 c6

{y,c} ---{y},{c} 即 y0 c0 y1 c1 y2 c2 y3 c3 y4 c4 y5 c5 y6 c6

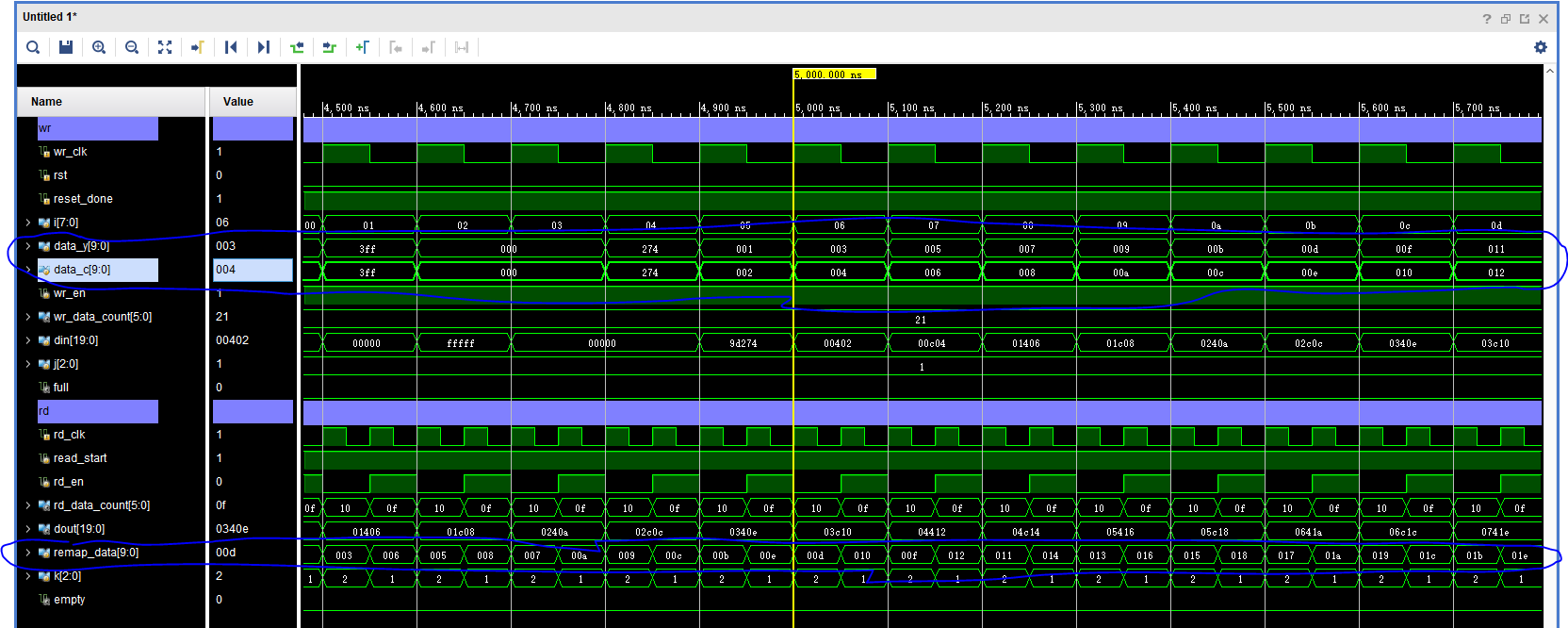

代码验证与仿真

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2018/11/27 14:01:44 // Design Name: // Module Name: data_map // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module data_map ( input wire wr_clk, input wire rd_clk, //rd_clk 的频率是wr_clk 的两倍 input wire reset_done, input wire rst ); //--------------------------------------------------------------------------------------------- // 生成y,c并行的数据序列 reg [7:0] i = 0; reg [9:0] data_y = 0; reg [9:0] data_c = 0; always @ (posedge wr_clk or posedge rst) begin if(rst) begin data_y <= 0; data_c <= 0; i <= 0; end else if(reset_done) begin case(i) 0: begin data_y <= 10'h3FF; data_c <= 10'h3FF; i <= i + 1'b1; end 1: begin data_y <= 10'h000; data_c <= 10'h000; i <= i + 1'b1; end 2: begin data_y <= 10'h000; data_c <= 10'h000; i <= i + 1'b1; end 3: begin data_y <= 10'h274; data_c <= 10'h274; i <= i + 1'b1; end 4: begin data_y <= 10'h001; data_c <= 10'h002; i <= i + 1'b1; end 5: begin data_y <= 10'h003; data_c <= 10'h004; i <= i + 1'b1; end 6: begin data_y <= 10'h005; data_c <= 10'h006; i <= i + 1'b1; end 7: begin data_y <= 10'h007; data_c <= 10'h008; i <= i + 1'b1; end 8: begin data_y <= 10'h009; data_c <= 10'h00A; i <= i + 1'b1; end 9: begin data_y <= 10'h00B; data_c <= 10'h00C; i <= i + 1'b1; end 10: begin data_y <= 10'h00D; data_c <= 10'h00E; i <= i + 1'b1; end 11: begin data_y <= 10'h00F; data_c <= 10'h010; i <= i + 1'b1; end 12: begin data_y <= 10'h011; data_c <= 10'h012; i <= i + 1'b1; end 13: begin data_y <= 10'h013; data_c <= 10'h014; i <= i + 1'b1; end 14: begin data_y <= 10'h015; data_c <= 10'h016; i <= i + 1'b1; end 15: begin data_y <= 10'h017; data_c <= 10'h018; i <= i + 1'b1; end 16: begin data_y <= 10'h019; data_c <= 10'h01A; i <= i + 1'b1; end 17: begin data_y <= 10'h01B; data_c <= 10'h01C; i <= i + 1'b1; end 18: begin data_y <= 10'h01D; data_c <= 10'h01E; i <= i + 1'b1; end 19: begin data_y <= 10'h01F; data_c <= 10'h020; i <= i + 1'b1; end 20: begin data_y <= 10'h021; data_c <= 10'h022; i <= i + 1'b1; end 21: begin data_y <= 10'h023; data_c <= 10'h024; i <= i + 1'b1; end 22: begin data_y <= 10'h025; data_c <= 10'h026; i <= i + 1'b1; end 23: begin data_y <= 10'h027; data_c <= 10'h028; i <= i + 1'b1; end 24: begin data_y <= 10'h000; data_c <= 10'h000; i <= 0; end default: begin data_y <= 10'h000; data_c <= 10'h000; i <= 0; end endcase end end //--------------------------------------------------------------------------------------------- // fifo 写控制,写满fifo 一半后开始读 reg [ 2:0] j = 0 ; reg read_start = 0 ; reg wr_en = 0 ; reg [19:0] din = 0; always @ (posedge wr_clk or posedge rst) begin if(rst) begin j <= 3'd0; read_start <= 1'b0; wr_en <= 1'b0; din <= 20'd0; end else if(reset_done) begin case(j) 3'd0: begin if(!full) begin wr_en <= 1'b1; j <= j + 1'b1; end else wr_en <= 1'b0; end 3'd1: begin if(full) begin wr_en <= 1'b0; j <= j + 1'b1; end else if(empty) read_start <= 1'b0; else begin din <= {data_y , data_c}; if(wr_data_count >= 11'd16) read_start <= 1'b1; end end 3'd2: begin if(wr_data_count <= 11'd16) begin wr_en <= 1'b1; j <= 3'd1; end end default: begin wr_en <= 1'b0 ; read_start <= 1'b0 ; end endcase end end //--------------------------------------------------------------------------------------------- // fifo 读控制,读使能信号rd_en 是一个1,0,1,0的脉冲序列 reg rd_en = 0; reg [2:0] k = 0; always @ (posedge rd_clk or posedge rst) begin if(rst) begin rd_en <= 1'b0; k <= 3'd0; end else if(reset_done) begin case(k) 3'd0: begin if(read_start && !empty) begin rd_en <= 1'b1; k <= k + 1'b1; end else rd_en <= 1'b0; end 3'd1: begin if(empty) begin rd_en <= 1'b0; k <= 3'd0; end else begin rd_en <= 1'b0; k <= k + 1'b1; end end 3'd2: begin if(empty) begin rd_en <= 1'b0; k <= 3'd0; end else begin rd_en <= 1'b1; k <= 3'd1; end end default: begin rd_en <= 1'b0; k <= 3'd0; end endcase end end //--------------------------------------------------------------------------------------------- wire [19 : 0] dout; wire full; wire empty; wire [5 : 0] rd_data_count; wire [5 : 0] wr_data_count; fifo_generator_0 U0 ( .rst(rst), // input wire rst .wr_clk(wr_clk), // input wire wr_clk .rd_clk(rd_clk), // input wire rd_clk .din(din), // input wire [19 : 0] din .wr_en(wr_en), // input wire wr_en .rd_en(rd_en), // input wire rd_en .dout(dout), // output wire [19 : 0] dout .full(full), // output wire full .empty(empty), // output wire empty .rd_data_count(rd_data_count), // output wire [5 : 0] rd_data_count .wr_data_count(wr_data_count) // output wire [5 : 0] wr_data_count ); //--------------------------------------------------------------------------------------------- //输出的串行数据,当re_en 为高时,输出高十位,当re_en 为低时,输出低十位 reg [9:0] remap_data; always @ (posedge rd_clk or posedge rst) begin if(rst) remap_data <= 0; else if(rd_en) remap_data <= dout[19:10]; else remap_data <= dout[9:0]; end //--------------------------------------------------------------------------------------------- endmodule /* add_force {/data_map/wr_clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/data_map/rd_clk} -radix hex {1 0ns} {0 25000ps} -repeat_every 50000ps add_force {/data_map/rst} -radix hex {1 0ns} {0 200ns} add_force {/data_map/reset_done} -radix hex {0 0ns} {1 2000ns} */

仿真结果:

成功将并联数据转换成串行的。