代码:

module bit1_bit4(

input clk_50M_i,

input rst_n_i,

input data_i,

input data_en_i,

output [3:0]data_o,

output data_en_o

);

reg data_i_tmp1;

reg data_i_tmp2;

reg data_en_i_tmp1;

reg data_en_i_tmp2;

reg [3:0]data_o_tmp;

reg data_en_o_tmp;

reg [3:0]cnt;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)begin

data_i_tmp1 <= 1'b0;

data_i_tmp2 <= 1'b0;

data_en_i_tmp1 <= 1'b0;

data_en_i_tmp2 <= 1'b0;

end

else begin

data_i_tmp1 <= data_i;

data_i_tmp2 <= data_i_tmp1;

data_en_i_tmp1 <= data_en_i;

data_en_i_tmp2 <= data_en_i_tmp1;

end

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

data_o_tmp <= 4'b0;

else if(data_en_i_tmp2)

data_o_tmp <= {data_o_tmp[2:0],data_i_tmp2};

else

data_o_tmp <= 4'b0;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

cnt <= 4'b0;

else if(data_en_i_tmp2)

cnt <= cnt + 1'b1;

else

cnt <= 4'b0;

always@(posedge clk_50M_i or negedge rst_n_i)

if(!rst_n_i)

data_en_o_tmp <= 1'b0;

else if(cnt == 4-1)

data_en_o_tmp <= 1'b1;

else

data_en_o_tmp <= 1'b0;

assign data_o = data_o_tmp;

assign data_en_o = data_en_o_tmp;

endmodule

测试:

`timescale 1ns/1ns

module bit1_bit4_tb();

parameter clk_period = 20;

reg clk_50M_i;

reg rst_n_i;

reg data_i;

reg data_en_i;

initial begin

clk_50M_i = 1'b0;

rst_n_i = 1'b0;

data_i = 1'b0;

data_en_i = 1'b0;

#100

rst_n_i = 1'b1;

#200

#clk_period data_i = 1'b1; data_en_i = 1'b1;

#clk_period data_i = 1'b1;

#clk_period data_i = 1'b0;

#clk_period data_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

#clk_period data_i = 1'b0; data_en_i = 1'b1;

#clk_period data_i = 1'b1;

#clk_period data_i = 1'b1;

#clk_period data_i = 1'b0;

#clk_period data_en_i = 1'b0;

#200

#clk_period data_i = 1'b1; data_en_i = 1'b1;

#clk_period data_i = 1'b1;

#clk_period data_i = 1'b1;

#clk_period data_i = 1'b0;

#clk_period data_en_i = 1'b0;

#200

#clk_period data_i = 1'b0; data_en_i = 1'b1;

#clk_period data_i = 1'b0;

#clk_period data_i = 1'b0;

#clk_period data_i = 1'b1;

#clk_period data_en_i = 1'b0;

#200

#clk_period data_i = 1'b1; data_en_i = 1'b1;

#clk_period data_i = 1'b0;

#clk_period data_i = 1'b0;

#clk_period data_i = 1'b0;

#clk_period data_en_i = 1'b0;

end

always #(clk_period/2) clk_50M_i = ~clk_50M_i;

bit1_bit4 bit1_bit4_inst(

.clk_50M_i(clk_50M_i),

.rst_n_i(rst_n_i),

.data_i(data_i),

.data_en_i(data_en_i),

.data_o(),

.data_en_o()

);

endmodule

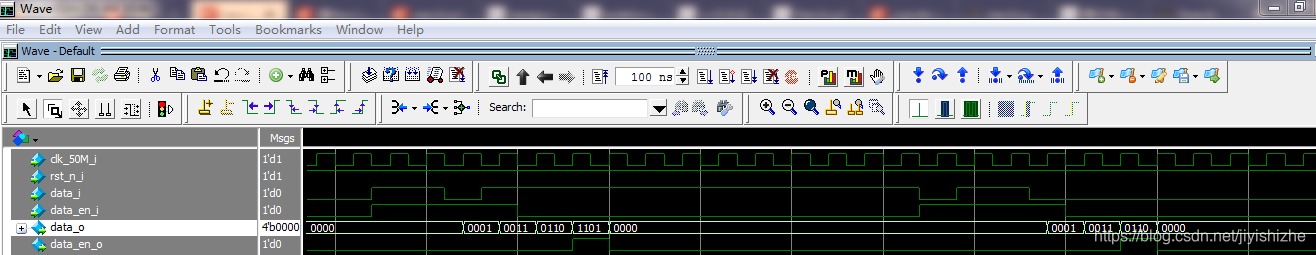

仿真截图:

说明:无意中看到了一些博客上的数据串并转换,逻辑上基本都能实现,但绝大部分都不能用,连基本的信号使能、时序打拍都没有,信号命名也很随便,就简单的实现了移位寄存器,直接复用的价值几乎为零,所以才有了我这两篇博客的诞生。时间比较赶,后面有时间会再优化一下,希望提供一种规范化的实用代码思路大家一起学习