Intel Platform Firmware Resilience

Intel PFR是一项安全技术,目的是保护服务器系统免遭PDoS攻击。在Whitley平台设计中,PFR是一个可选的特征。实现PFR特征需要硬件和软件的协作。本文档用于描述PFR的硬件设计需求。关于PFR固件开发指南在其他文档有阐述。

Intel PFR的关键前提是无论一个系统是否存在固件保护,黑客都有办法绕过这些保护措施。Intel PFR提供了固件保护和恢复功能,它可以检测系统是否遭受了攻击,以及遭受攻击后,将系统恢复到一个正常状态。这个过程是快速的且无需用户干涉的,非常适合大型数据中心。Intel PFR技术是通过把信任的根源放置到Intel Xeon处理器(Intel PFR-Enabled)和平台的PFR CPLD实现的。同时,处理器和PFR CPLD授权平台上的其他各种固件,如果必要,可以把这些固件恢复到正常状态。在运行过程中,Intel PFR技术提供了对关键总线(诸如SPI和SMBus,它们可以访问NV存储)的主动过滤能力。这可以避免对关键部件(诸如SPI Flash,电源固件,热交换背板固件和数字电压调节器固件)损坏的攻击。

Intel PFR也提供一种可选的PIT功能(运输途中保护),保护系统在运输中免遭篡改。

固件保护和恢复

Intel PFR提供多层固件攻击保护和固件恢复机制,因此增加了平台的弹性:

- 显式检查:运行在Intel Xeon处理器(PFR-Enabled)的厂商代码模组(VCM)对平台固件执行签名验证(比如,SPI描述,BIOS,BMC,Intel ME, NIC).

- 隐式检查:PFR CPLD监测平台引导过程,检查与正常引导行为的差异.

- 主动过滤:PFR CPLD维护一个针对不同平台元件允许的SPI和SMBus命令白名单,这可以过滤恶意的访问和操作。

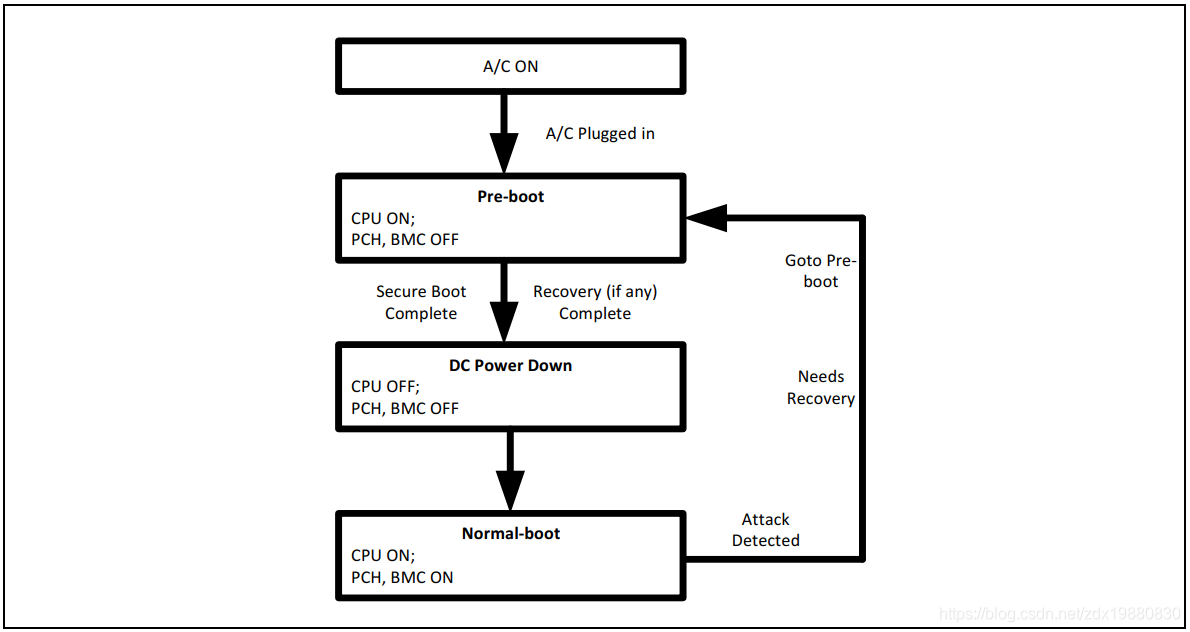

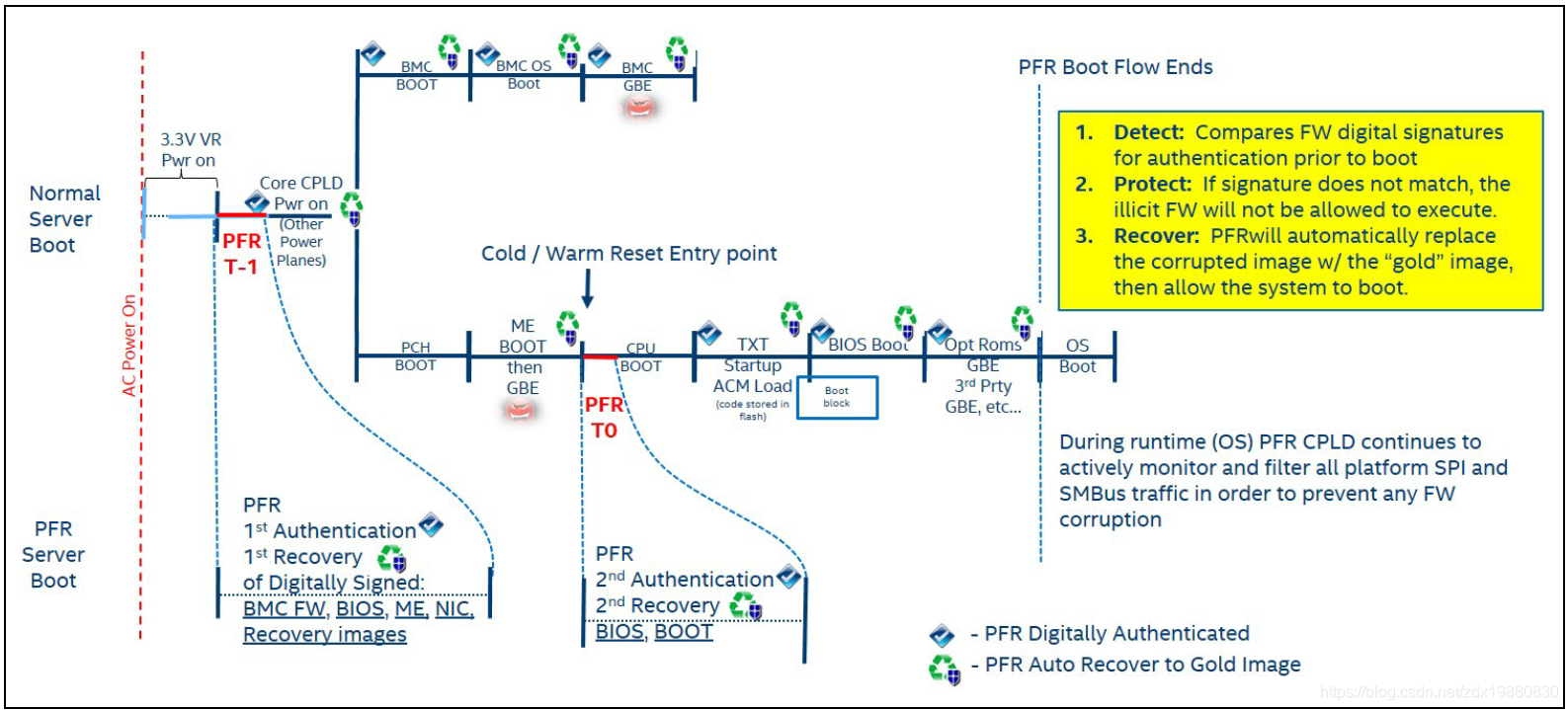

Intel PFR技术使得Intel Xeon处理器按照一种特定的预启动模式(T-1)启动,这种模式下,只有CPU处理激活状态,所有有可能干扰引导路径(或引导操作)的其他设备(比如PCH/ME和BMC)处于复位状态。关键的引导固件(诸如BIOS,ME,BMC等等)在T-1模式下需要数字验证。以固件污染为例,一旦检测到固件污染,PFR触发一个固件恢复事件,然后移除SPI Flash Active区域中受污染的固件,从Gold中拷贝一份固件到SPI Flash Active区域。从Gold恢复拷贝中更新也是在T-1模式下执行的。一旦成功,系统继续按照正常模式引导。

在系统运行时,诸如SPI和SMBus等关键总线,由于它们可以访问NV存储,因而被监控以过滤掉潜在的恶意操作和访问。

Protect In Transit(PIT)

为了防止系统固件在运输途中被篡改,Intel PFR提供了多层的运输保护机制:

- 平台锁定:密码保护平台上电

1.1 板上PFR CPLD和RF部件提供随机密码(PIT密码)

1.2 PFR CPLD在平台上电时比较PIT密码,如果板上RF部件的密码遗失,那么阻止上电时序

1.3 在出货前,从RF部件中移除密码,这样就可以阻止平台在运输中上电 - 封闭平台固件

2.1 在出货前,PFR CPLD计算平台上所有固件的哈希值,然后把这些哈希值存储到一个安全的NVRAM空间

2.2 在交付的时候,PFR CPLD重新计算平台上所有固件的哈希值,如果发现有固件的哈希值与存储在NVRAM中不匹配,发出告警信息

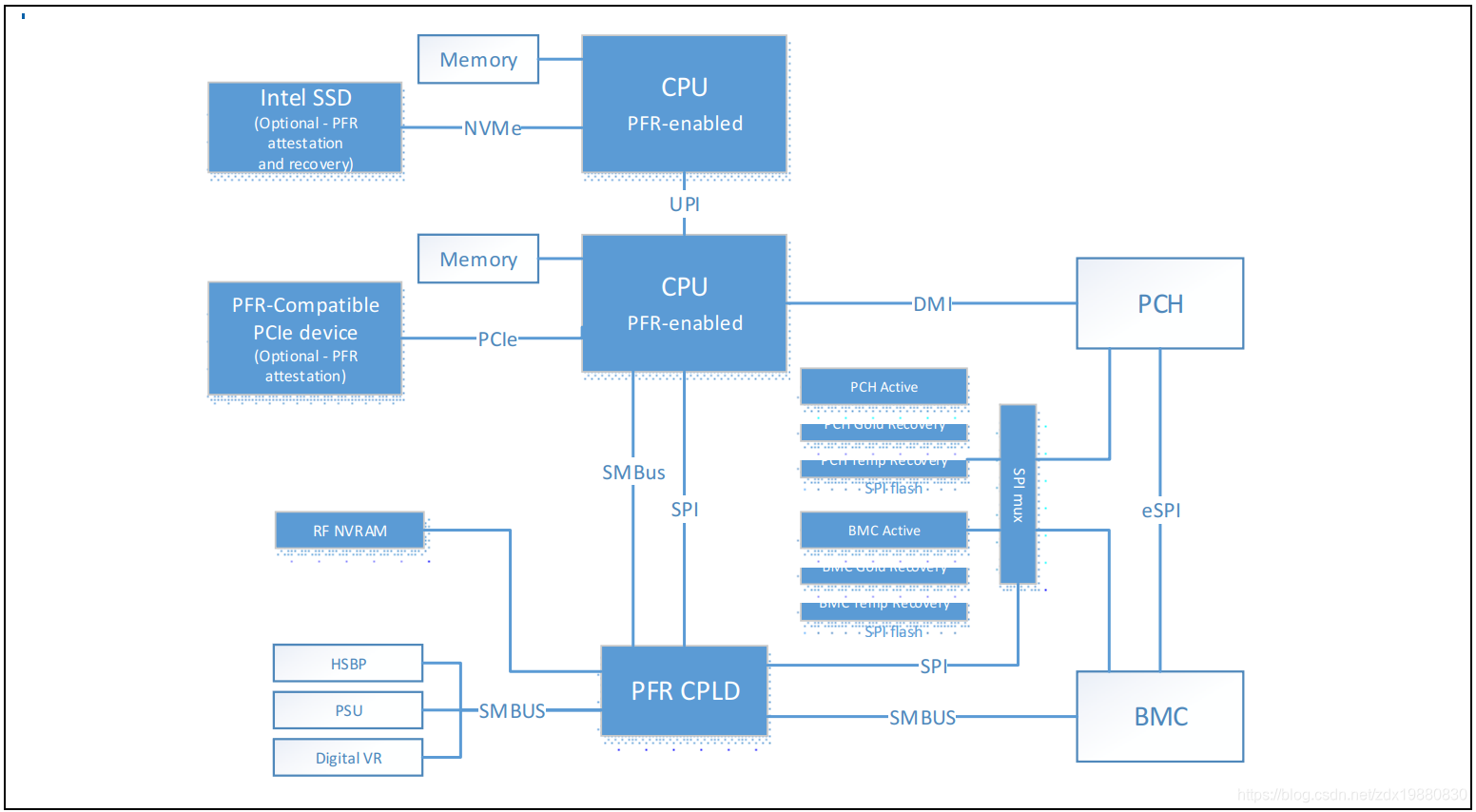

Intel PFR硬件架构

Intel PFR由如下几个关键模组构成:

- PFR CPLD是Intel PFR的核心,它主要用于关键的监测,计算哈希值,硬件保护,通讯接口和平台时序

- BMC固件Flash用于存储BMC固件的镜像。该Flash的特定区域由PFR保护,同时该Flash也会存储BMC的固件恢复镜像

- PCH附带的SPI Flash用于存储BIOS,ME和平台其他的固件镜像。该Flash的特定区域由PFR保护,同时,它也存储平台上关键部件的固件恢复镜像

- SPI总线多路复用逻辑用于选择BMC SPI和PCH SPI的主控。在PFR预启动模式(T-1),PFR充当BMC和PCH SPI的SPI主控。在正常引导模式下(T0),BMC SPI和PCH SPI主控分别控制各自的Flash设备

- CPU Microcode/pcode:在PFR预引导环境下,CPU的Microcode和Pcode能够在PCH和BMC部件处于复位状态时使能CPU的引导过程,并加载厂商代码模组(VCM)。它可以通过SPI接口与PFR CPLD进行最初始得通信

- CPU授权代码模组(也被称为VCM),是一段OEM自有和签名得X86代码,在特殊环境下运行在CPU上。VCM存储在PCH的SPI Flash中,由CPU Microcode通过PFR CPLD的SPI接口加载到CRAM。VCM包含了执行PFR安全引导和恢复操作的大部分代码

- PFR与其他预先存在的部件协助,以确保这些部件按照指定次序工作,保证PFR功能正常工作。

上图显示了PFR平台架构的框图,所有的CPU通过SPI总线接口连接到了PFR CPLD。SPI是CPU和PFR CPLD之间的主要通讯通道,即每颗CPU与PFR CPLD有一条SPI通道。同时在PFR CPLD和CPU还需要额外保留一条SMBus通信接口。

PFR CPLD可以通过板上SPI多路复用器访问PCH SPI Flash和BMC SPI Flash。PFR CPLD控制多路复用器的选通。这获得了预引导(T-1)模式下SPI Flash的访问。在正常引导模式(T0)下,PCH和BMC可以分别访问它们各自的Flash设备。Flash设备的SPI输入信号也应该连接到PFR CPLD,以便允许CPLD在正常引导模式下,监控和过滤PCH和BMC下达的SPI Flash事务。BMC还可以通过SMBus访问数字VR,热交换背板和PSU等板上关键部件的固件,这些总线也应该连接到PFR CPLD,以便允许PFR在正常引导和运行时监控和过滤SMBus上对这些设备通讯事务。

为了实现可选的PIT功能,板上还需要增加RFID模组和天线。

上图中显示的可选的Intel SSD(支持PFR证明和恢复)以及PFR兼容的PCIe设备(支持证明)并不需要任何硬件上的变动,也不需要固件上的变动。关于固件的需求在其他的文档有说明。

带有PFR的服务器平台互连

PFR信号连接

如图786显示了Wilson City参考平台(RP)上PFR实现的整个平台互连。该互连仅仅适用于Wilson City,而对于其他平台,需要系统设计者选择合适各自平台的实现方案。

PFR CPLD是PFR技术的核心,平台互连以PFR CPLD为核心。与PFR交互的主要部件是Core CPLD(Core CPLD和PFR CPLD可以集成在同一个物理部件),CPU,BMC,PCH和存储固件的Flash设备。PFR也提供了对平台上诸如PSU,数字VR和高速背板保护,保护这些部件的NV储存以及提供了一种安全更新这些部件固件的机制。

PFR平台引导流程

在T-1模式下,PFR CPLD可以完全访问所有的SPI设备。在这个阶段的重要操作如下:

- 完成PCH和BMC有效区和恢复区的固件数字签名验证。PFR VCM和PFR CPLD协助计算SHA256哈希值进行验证。它也可以检查任何固件是否需要更新:PCH/BMC恢复gold更新,数字VR/PSU,HSBP固件更新等等。它通过验证更新候选副本的真实性执行更新操作。比如,PCH或者BMC任一有效SPI Flash镜像被检测到受损,这将触发一个恢复操作,即完整删除有效备份,并且从最新Gold恢复区域还原。

- 一旦T-1模式下的这些安全操作成功完成,系统继续正常引导。

带有PFR平台的复位Sequence

下图显示了开启PFR功能的平台复位时序。

PFR平台支持

PFR功能开启和禁止控制

处理器根据PFR_DISABLE Strap Pin配置决定平台是否支持Intel PFR,从而决定处理器的动作。PFR_DISABLE在CPU内部上拉。建议:在不支持PFR功能的平台把PFR_DISABLE Strap Pin在板上上拉。

支持PFR功能的平台在运行时将PFR_DISABLE拉低。建议:在板卡测试前期,将PFR功能禁止掉,这意味着需要有能力把PFR_DISABLE信号拉高。