最近在持续笔试中,今天见的题感觉难度又上升了,因此需要计算一下。首先来看一下题目。

已知:

输入延时:T(in_delay)=1ns

Inverter的延时:T(inv_max)=1ns T(inv_min)=0.5ns

Buffer的延时:T(buf_max)=2ns T(buf_min)=1ns

NAND2的延时:T(nan_max)=1.8ns T(nan_min)=0.9ns

NOR2的延时:T(nor_max)=2ns T(nor_min)=1ns

D 触发器的传输时间:T(cq_max)=4ns T(cq_min)=1ns

建立时间:T(setup)=3ns 保持时间:T(hold)=1ns

求解:

1.电路是否有时钟违例?如果有该如何修改?

2.电路的最高时钟频率是多少

解答:

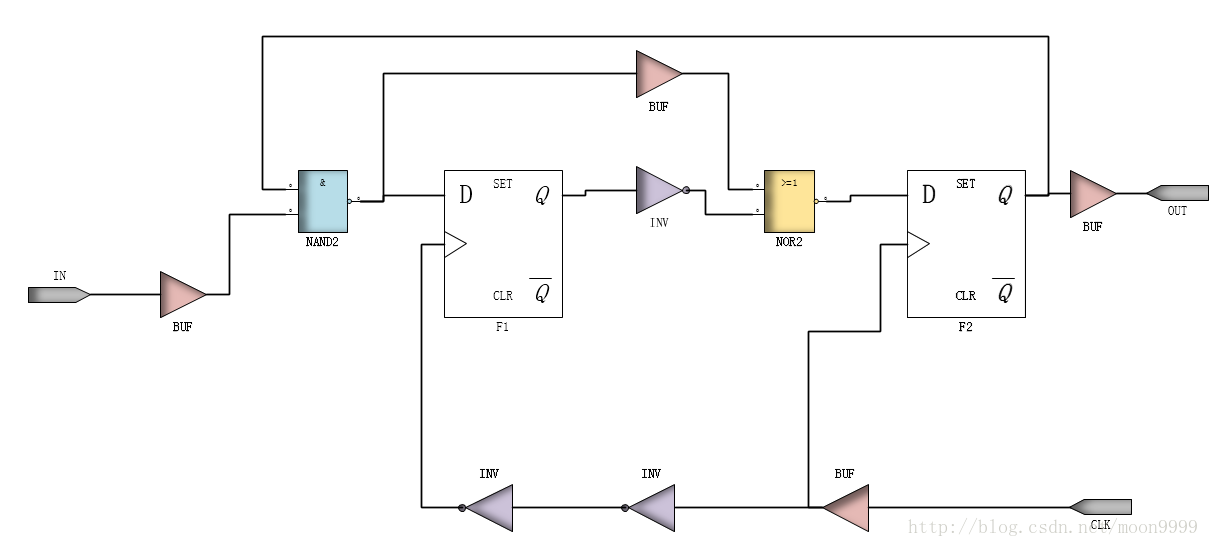

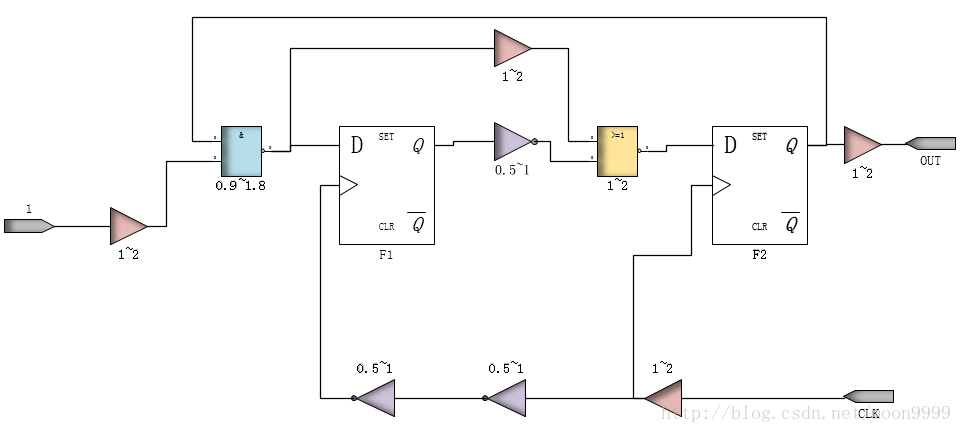

解答这个题啊,我认为我们不需要关注里面都是什么器件,主要关注里面的延时就可以了,因此先标注延时信息在上面。

1.解决第一问先要明确一个问题,可能时钟违例有哪个呢?

在这个时序电路里无非就是建立时间违例和保持时间违例两种,而建立时间裕量中是包含时钟的,因此我们可以断定此时不会是建立时间违例因为时钟周期还不确定。因此如果有违例一定是保持时间违例。

那么两个触发器F1和F2哪个的保持时间违例了呢?此时我们需要用公式进行分析了,保持时间裕量的公式计算如下:

hold time stack = Tcq+Tcom-△T-Thold

如果以F2为计算对象,那么Tcq为F1的,Tcom为F1、F2之间的,△T为F2的时钟偏移减去F1的,Thold为F2的。

那么我们来计算下F1的最小保持时间裕量:

hold time stack(F1) = (Tcq+Tcom)min-(△T)max-Thold=0.9+1-(2)-1=-1.1ns

可以看到F1的保持时间已经违例。

那么再计算下F2的最小保持时间裕量:

hold time stack(F2) = (Tcq+Tcom)min-(△T)max-Thold=0.5+1-(-1)-1=1.5ns

不错在违例情况。

因此可以得出结论:F1的保持时间违例。

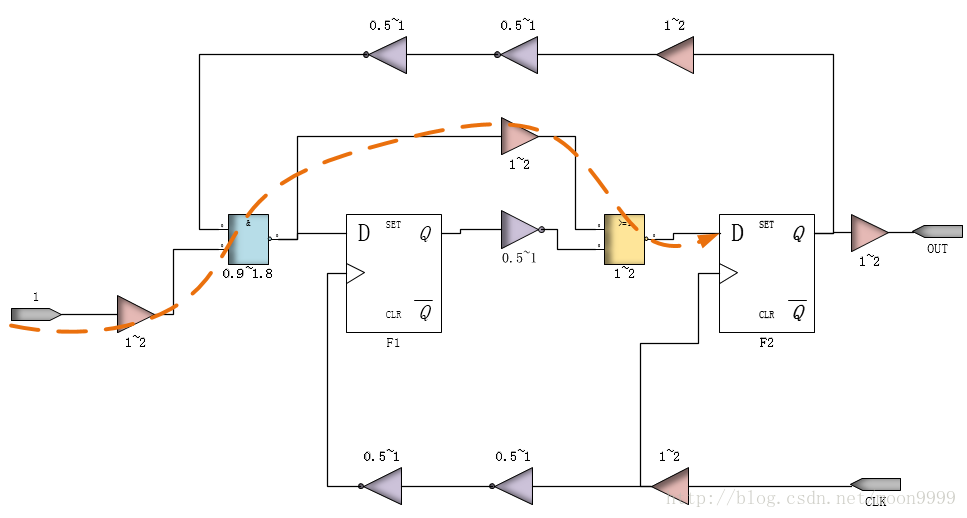

那么如何修改呢?增加F1-NAND2-F2之间的延时就可以了。因此可以在F1-NAND2-F2之间加入两个反相器和一个延时Buffer,使得

hold time stack(F1) = (Tcq+Tcom)min-(△T)max-Thold=(0.9+1+1)+1-(4-2)-1=0.9ns

则不再有F1的保持时间违例问题。那么在解决第二问时候我就默认为已经改了,当然对最后的结果没有影响。

2.要计算最快时钟频率当然要先找关键路径。

首先看下下面这条看上去比较长的路径:

先看下计算时钟周期的公式,当然是需要计算所能达到的最窄的时钟周期,这样才能有最高频率:

T >= Tsetup+(Tcq+Tcom)max-△T

那么在这个题里

(Tcom)max=2+1.8+2+2=7.8ns

(Tcq)max=1ns //由于数据来自于输入端,其实是没有这个值的,不过因为输入数据延时1ns因此就取其为1ns

Tsetup=3ns

(△T)min=1-0=1

因此我们得到:T >= 3+1+7.8-1=10.8ns

不过这也不一定是关键路径,那么我们再看下另外一条比较长的路径:

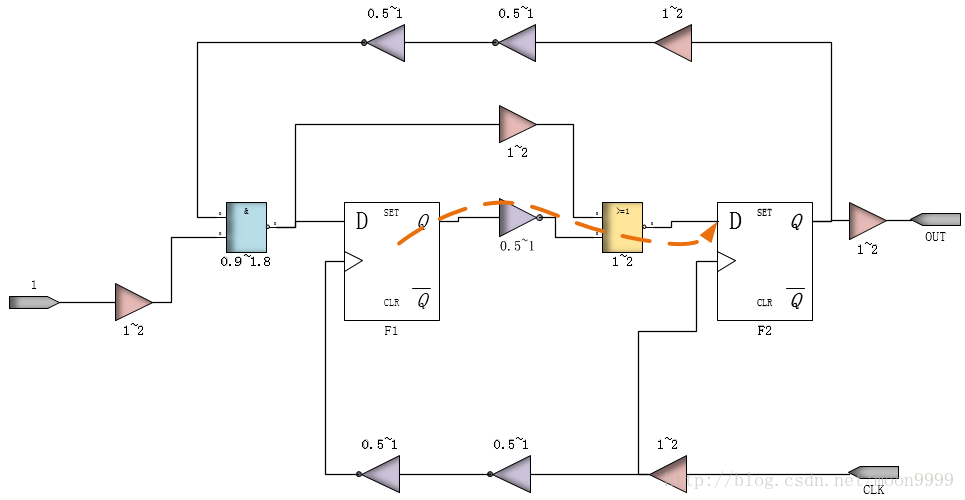

这条路径里的时序信息是怎样的呢?

(Tcom)max=2+1=3ns

(Tcq)max=4ns

Tsetup=3ns

(△T)min=-2ns(注意是用F2的时钟偏移减去F1的)

因此我们得到:T >= 3+4+3-(-2)=12ns

哇塞原来这才是关键路径,果然眼睛是会骗人的,因此我们计算最高频率:

那么意味着fmax=1/Tmin=1/12ns=83.3MHz

版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/moon9999/article/details/78024858