feature_in_reg_matrix中如何解决读取RAM和DDR时数据移位方式不同的位置

简述

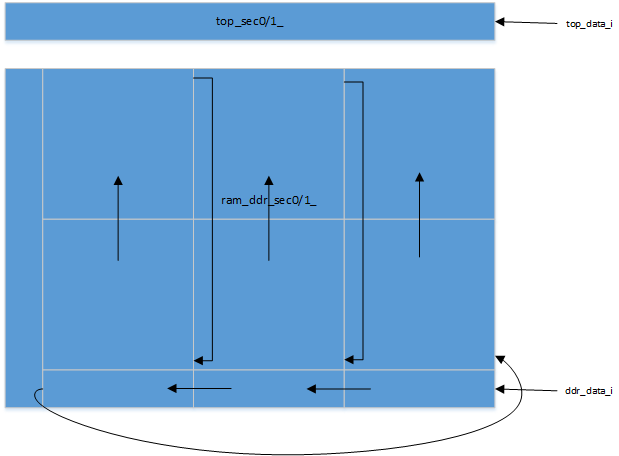

在输入feature map寄存器组中,由于想用移位的方式接受来自RAM或者DDR的数据,这样可以避免使用MUX带来的逻辑电路的复杂性(如果用MUX的话要每个位置都要一个case来判断,情况太多)。但是在读取RAM和DDR数据的时候,对数据移位的方式是不一样的,我们的设计中把寄存器组分成了两个sector:top_sec0/1和ram_ddr_sec0/1,可以看下图:

first shot情况(第一次从DDR读数据填充到寄存器组中)

在第一次从DDR读数据时,ram_ddr_sec_寄存器组整个是一个连续的存储区域,存储器的排列如图1所示,箭头的方向表示移位的方向。non first shot情况(从RAM和DDR同时读取数据)

在同时从RAM和DDR里读取数据的时候,top_ddr_sec_区域就分成两个部分在说数据移位,一个部分是黑色箭头对应的ddr部分,另一个部分是红色箭头对应的ram部分。

从上面可以看出,两种情况下的寄存器的移位和数据排列都是不一样的,下面就具体说一下怎么解决这种情况。

寄存器移位

寄存器移位的问题就是该怎么判定ram区域和ddr区域的边界部分是移位还是接受来自RAM的数据,在first_shot的情况下,不存在边界区域,但是在non_first_shot的情况下,就需要对边界部分进行处理。

在non_first_shot的情况下,ram区域的寄存器不参与ddr数据的移位,即ddr数据的移位终点就是ddr区域的最后一个寄存器。所以实际上,non_first_shot情况下,ram_ddr_sec_又分成了两个部分,每一个部分分别接受来自RAM和DDR的数据,然后各自进行数据移位。

另外我们还需要解决一个情况:由于从DDR出来的数据位宽是512-bit,不论是在first_shot还是non_first_shot情况下,寄存组的数据size都不是512的整数倍,那也就意味着,最后一个512-bit的DDR数据到来时,里面只有部分的数据是我们需要的,这就导致最后一次寄存器移位的步长和前面不一样,因为verilog语言的特性,我们不能把移位步长本身设置成一个变量,而只能用if或者case来实现这种情况。

数据排列顺序

从上面的移位可以看出,在first_shot和non_first_shot两种情况下,数据排列的顺序是不一样的,为了向输出端屏蔽这种数据排列顺序的变化,我们需要向输出端输出一个统一的数据排列的方式,采用的方式和虚拟内存的思想差不多,如下图所示:

这里我们向输出端输出的统一是按行排列的顺序数据,对于将来数据选择来说,我们只需要从“虚拟寄存器组”选择数据即可。