7. 可编程并行接口芯片 8255A

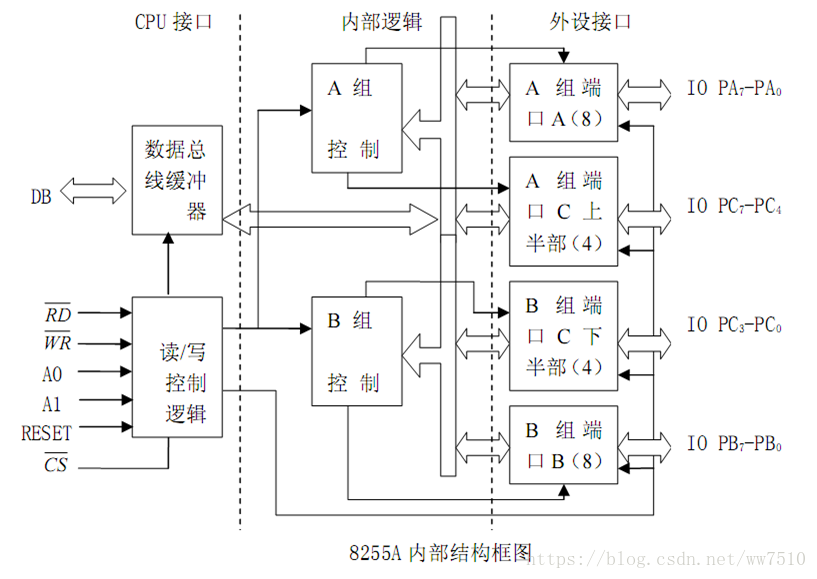

1. 结构,由 4 部分构成:

(1)数据总线缓冲器

(2)3 个 8 位端口 PA、PB 和 PC

通常 PA 口和 PB 口用作输入输出的数据端口,PC 口用作控制和状态信息端口,分为两个 4 位端口

(3)A 组和 B 组的控制电路

(4)读/写控制逻辑

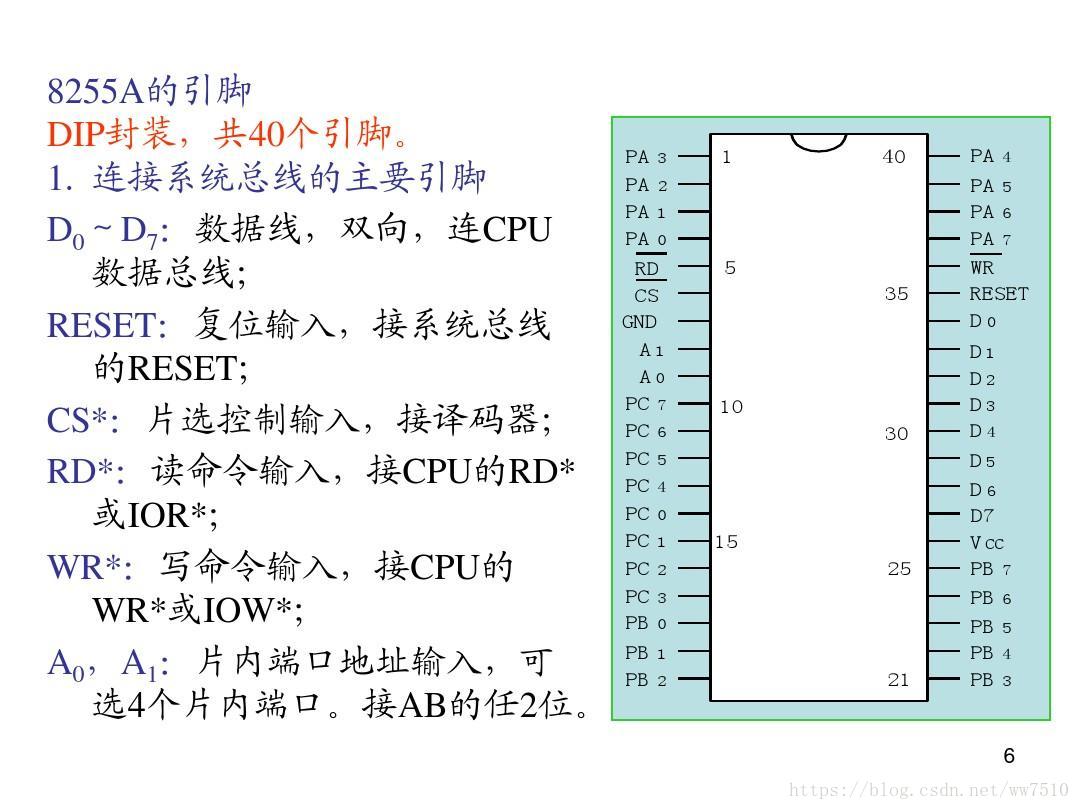

2. 8255A 的引脚

3. 8255A 的工作方式:3种

(1)方式0:基本输入/输出(A,B,C口均有)

(2)方式1:选通输入/输出(A,B口具有)

(3)方式2:双向选通输入/输出(A口具有)

3 种工作方式可用软件编程对控制口设置来指定。三种基本的工作方式为:

- 工作方式 0 (基本输入输出方式)

方式 0 不使用联络信号,也不使用中断,A 口和 B 口可定义为输入或输出口。

C 口分成两个部分(高四位和低四位),C 口的两个部分也可分别定义为输入或输出。

在方式 0,所有口输出均有锁存,输入只有缓冲,无锁存,

C 口还具有按位将其各位清 0 或置 1 的功能。

常用于与外设无条件的数据传送或接收外设的数据。 - 工作方式 1 ( 选通输入输出方式)

A 口借用 C 口的一些信号线用作控制和状态信号,组成 A 组

B 口借用 C 口的一些信号线用作控制和状态信号,组成 B 组

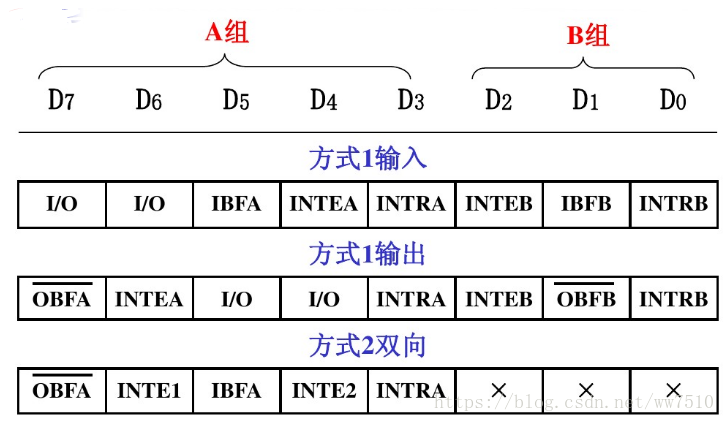

在方式 1 下,C 口的某些位被占用。

A 组:PA 端口,PC7~PC4

B 组:PB 端口,PC3~PC0

方式 1 常用于中断传送和查询传送数据

方式 1 的输出:

当 A 口工作于方式 1 且用作输出口时,

C 口的 PC7 线用作输出缓冲器满 OBF 信号,

PC6 用作外设收到数据后的响应信号 ACK ,

PC3 用作中断请求输出信号线 INTR。

当 B 口工作于方式 1 且用作输出口时,

C 口的 PC1 线用作输出缓冲器满OBF 信号,

PC2 用作外设收到数据后的响应信号 ACK ,

PC0 用作中断请求输出信号线 INTR。 - 工作方式 2 (双向输入输出方式,A 口独有)

方式 2 是 A 组独有的工作方式。外设既能在 A 口的 8 条引线上发送数据,又能接收数据。此方式也是借用 C 口的 5 条信号线作控制和状态线, A 口的输入和输出均带有锁存。

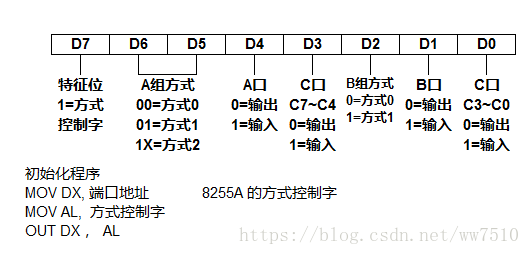

4. 8255A 的控制字 (初始化)

有两种控制字:方式控制字、C 口置位/复位控制字

用户可以通过程序把两个控制字送到 8255A 的控制寄存器,以设定 8255A 的工作方式和 C 口各位的状态

- 方式控制字(用于设定 3 个端口的工作方式,输入或输出)

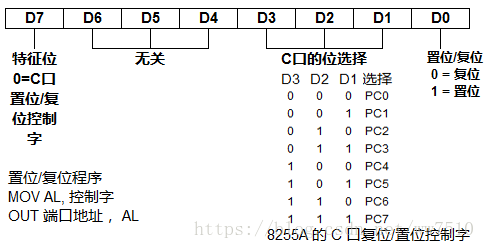

- C 口置位复位控制字

在 8255A 芯片初始化时,C 端口置 1 /置 0 控制字可以单独设置 C 端口的某一位为 0 或某一位为 1。

控制字的 D7 位为 “ 0 ” 时,是 C 端口置 1 /置 0 控制字中的标识位,这个控制字只对 C 口起作用,任何一位都可以通过按位置位/复位控制字来设置。

注意:对 C 口的置位/复位控制不是把控制字送到 C 口,而是由控制口决定各位的状态,是把控制字送到控制口

- C 端口的状态字

当 8255A 的 A 口和 B 口工作在方式 1 或 A 口工作在方式 2 时,通过读取 C 口的数据,可以检测 A 口和 B 口的状态

读信号:

IBF:(Input Buffer Full)输入缓冲器满信号,输出到外设。有效时表示,有一个外设来的数据锁存在 8255A 中,尚未被 CPU 取走,暂时不能接再收外设来的数据

INTR:(Intrrupt Request)中断请求信号,输出到 CPU。向 CPU 发出中断请求

INTE:A 组合 B 组都有中断允许触发器,用来控制是否允许 8255A 的中断请求信号 INTR 发出

STB:(Strobe)选通脉冲信号,外设输入。表示外设已经准备好数据。

写信号:

OBF:(Output Buffer Full)输出缓冲器满信号,输出。

ACK#:(Acknowledge)外设响应信号,外设输入。表示输出端口的数据已被取走,8255A 可以传送下一个数据