1、并行接口:

a、标准51接口

b、x86计算机可编程并行接口

c、STC系列并行接口

d、Cygnal C8051系列并行接口

e、三星S3C44B0 GPIO

f、意法半导体STM32F103XXXX系列 GPIO

2、51并行接口:P0、P1、P2、P3;在CPU看来就是有几个可以访问的地址

3、atmel 2051并行接口:P1、P3

4、地址与位一般表示:寄存器名+‘.’

a、P0:80H,P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1(81H) P0.0(80H)

b、P1:90H

c、P2:A0H

d、P3:B0H

e、即这几位可以用位地址、位名称、或者上述寄存器名+‘.’的三种方法,但只有有位地址的位才可以进行位访问。

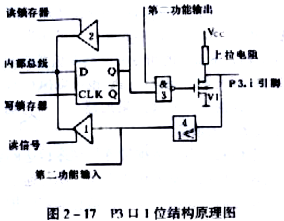

5、51的P3口的并口复用功能(第二功能):

a、P3.7(/RD)外部数据存储器读选通,输出,低电平有效

b、P3.6(/WR)外部数据存储器写选通,输出,低电平有效

c、P3.5(T1)定时器/计数器1外部计数脉冲输入

d、P3.4(T0)定时器/计数器0外部计数脉冲输入

e、P3.3(INT1)外部中断1请求

f、P3.2(INT0)外部中断0请求

g、P3.1(TXD)串行输出口

h、P3.0(RXD)串行输入口

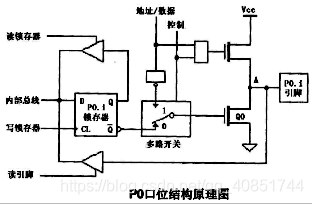

6、P0口结构(其中一位):

P0口是一个漏极开路的准双向口、低8位地址/数据总线口。其中有一个多路开关。

当内部信号置0时,多路开关作为IO口使用,输入缓冲输出缓存,输出为漏极开路,与nmos的电路接口时必须用电阻上拉才能有高电平输出,输入时为悬浮状态,为一个高阻抗的输入口;

当内部信号置1时,作为地址/数据复用总线,为一个准双向口,有两个上拉电阻。

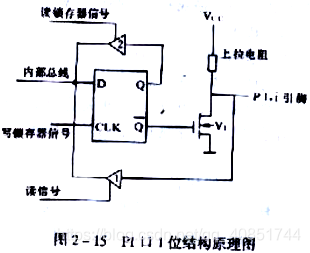

7、P1口结构(其中一位):

P1口只能作为I/O口使用,因而输出控制电路结构同可复用的并口不同。就是一个简单的D触发器。

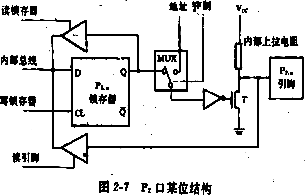

8、P2口结构(其中一位):

P2口既可以作为双向IO口,也可以用作高8位地址总线

9、P3口结构(其中一位):

P3口具有第二功能,但不能与双向IO口混用

10、51的四个并行口均可以作为双向IO口使用,输入时可以缓冲,输出时可以锁存;都是锁存器加引脚的典型结构,注意P0和P1-P3的驱动能力不同:

a、P0:访问片外扩展存储器时,复用为低8位地址线和数据线

b、P1:准双向口结构,需要先向锁存器写‘1’,仅双向IO端口

c、P2:准双向口结构,需要先向锁存器写‘1’,可复用为高8位地址线

d、P3:准双向口结构,需要先向锁存器写‘1’,具有第二功能

11、P0,P1,P2,P3每个口主要由四部分构成:端口锁存器、输入缓冲器、输出驱动器和引至芯片外的端口引脚。他们都是双向通道,都可以独立的作为输入或输出。

12、P0口和P2口内部各有一个2选1的选择器,受内部控制信号的控制(可以理解为P0M和P2M两组寄存器)。四个接口在进行I/O方式时,特性基本相同:

a、作为输出时,内部带有锁存器,故可以直接与外设相连

b、作为输入时,有两种方式,即读端口(寄存器)和读引脚(IO脚):

①、为“读-修改-写”操作。读端口实际上不从外部选入数据,而只是吧端口锁存器中的内容读入到内部总线,经过某种变换后再写回到端口锁存器。

②、为“仅读”操作。读引脚才是真正地把外部的数据读入到内部总线。

CPU可以发出这两种控制信号以完成不同的读操作。

c、在读引脚是,要先通过指令吧端口锁存器置为1,然后再实行读引脚操作,否则可能读入出错。若不先对端口置1,端口锁存器中原来的状态可能为0,加到输出的信号为1,就导通,对外呈现低阻抗。这个时候即便使引脚上输入的是1信号,也会因端口的低阻抗而使信号变低,使得外加的1信号读入不一定是1。

所以,这四个端口在用于输入操作时还必须附加一个准备操作,所以被称为准双向口。也是因为这个原因,为了避免出错,在一开始这四个端口的初始值都已经被设置为了高电平,以免出现对于高电平信号无法准确输入输出的情况。故51的IO引脚用作输入、或第二功能时,必须先置“1”——准双向口。

13、由于P0口没有上拉电阻(内置),所以P0在驱动的时候(作为输出口)需要加上上拉电阻(电阻接VCC),就是说,P2能出20mA电流,P0就不能。

14、X86并行接口——8255可编程并行接口:

a、计算机系统的基本功能子系统要求

b、集成电路=>多功能化、通用性、系列化

①、82XX PC微机接口系列可编程芯片

②、8237:可编程DMA控制器

③、8250/1:可编程串行接口

④、8253/4:可编程定时/计数器

⑤、8259:可编程中断控制器

⑥、8255:可编程并行接口

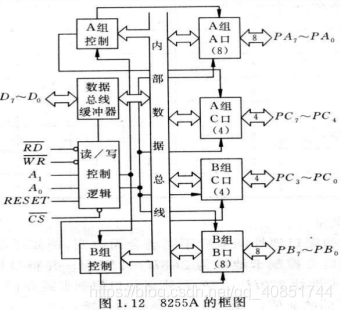

15、8255结构框图:

A组的A口和C口的功能可以通过A组控制进行改变。

B组的B口和C口的功能可以通过B组控制进行改变。

A组控制可以控制C口的高4位,B组控制可以控制C口的低4位,由此可以实现可编程的IO口。

基地址由CS译码电路确定,而偏移地址通过控制字确定,访问哪个端口

16、82XX的接口方法基本相同

a、基地址:由系统译码电路产生CS信号

b、偏移地址:由芯片地址线(A0、A1、…)确定

c、从PC/AT机系统看:功能部件抽象为若干个可以访问的IO寄存器

17、82XX各功能不同

a、工作原理视芯片不同而不同,使用时需要具体理解

b、多功能的编程控制方法:通过寄存器控制

18、STC系列并行接口的四种模式,通过PxM1,PxM0设定:

由于增加了三极管(强,极弱,弱),由于可以选择是否启用(两比特)

a、准双向口(标准51,默认),只用弱的三极管(灌电流大、拉电流小)

b、推挽输出(推挽),三个三极管都用(强上拉,可达20mA)

c、仅输入,四个三极管都不用(用于输出的也不用),仅作为输入(高阻)

d、漏极开路输出(开漏,OD),三个都不用(内部上拉电阻断开)

19、STC有六个IO并口,每个都一样,都有四种模式,仅地址不同。每个IO并口寄存器分别与两个控制寄存器相关,故总共有6x3=18个并口相关寄存器(一组为P0,P0M0,P0M1)

20、Cygnal C8051F0XX并口接口的特点:

a、可以通过XBR0,XBR1,XBR2中国的一些bit将IO端口分配到一定引脚

b、并口电气特性可通过(XBR2中的WEAKPUD位和PRTxCF)设定三种模式:

①、弱上拉,标准51准双向口

②、推挽

③、开漏OD

21、SAMSUNG S3C44B0 GPIO(也就是并口)的特点:

a、port A、B、C、D、E、F、G共71pin,每个可能不止8bit,每个引脚可以很容易的配置成满足各种需要和要求

b、每一引脚分配了多功能(功能复用)

c、通过寄存器(PCONx,PDATx,PUPx)配置功能和电气特性

d、每个端口都不一样

22、意法半导体STM32F10XXX GPIO(即并口)的特点:

a、系列分高、中、低密度,提供不同数量IO pin产品

①、最少26 GPIO pins(36 pins封装)

②、最多可达112 GPIO pins(144 pins 封装)

b、每一引脚分配了多功能、每一功能可分配到多个引脚

c、GPIO电气特性:8种(用2个寄存器,每个引脚用4bit位配置)

①、端口配置高寄存器(GPIOx_CRH) (x=A…E)

②、端口配置低寄存器(GPIOx_CRL)

d、GPIO其它寄存器:

①、端口输入数据寄存器(GPIOx_IDR)

②、端口输出数据寄存器(GPIOx_ODR)

③、端口位设置/清除寄存器(GPIOx_BSRR)

④、还有很多。每组GPIO多达14个寄存器(每个最少16位,可能有32位),A、B、C、D、E共70个(5x14)

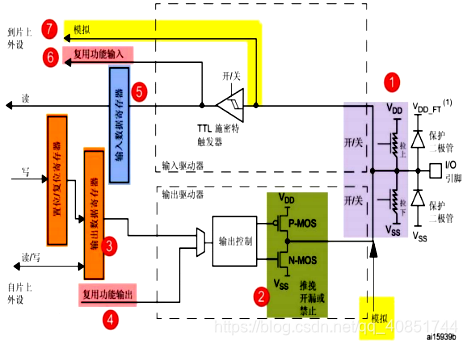

23、STM32F10XXX GPIO的基本结构:

a、上拉下拉电路

b、推挽开漏电路

c、数据输出寄存器

d、复用功能输出

e、数据输入寄存器

f、复用功能开关

g、模拟输入开关

24、 STM32F10XXX GPIO的基本特性:

a、GPIO控制特性:每组受控IO有十六个可控制通道,既可以单独控制,也可以整体控制

b、GPIO驱动特性:所有GPIO的驱动特性均可以配置为推挽或开漏+上拉或下拉模式

c、GPIO输入特性:所有GPIO的输入都可以配置为浮空、上拉、下拉、模拟。

d、GPIO开关特性:所有GPIO的输入和输出的开关特性均可设置为2MHZ\25MHZ\50MHZ\100MHZ

e、GPIO复用特性:当相应的GPIO可以用做他用时就具有了复用特性,可选择GPIO或复用外设

嵌入式(二十):并行接口

猜你喜欢

转载自blog.csdn.net/qq_40851744/article/details/106426654

今日推荐

周排行