一、PLD

1、PLD发展过程

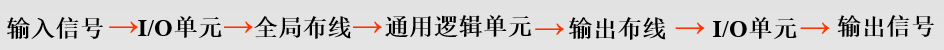

(1)、PROM:与阵列固定,或阵列可编程

(2)、PLA:与阵列、或阵列均可编程

(3)、CPLD:复杂可编程逻辑器件

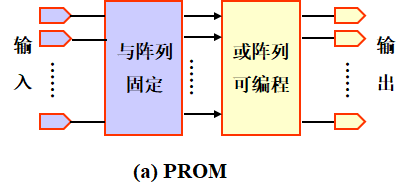

①、PAL:与阵列可编程,或阵列固定

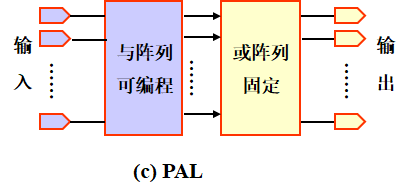

②、GAL:通用逻辑阵列

(4)、FPGA:现场可编程门阵列

2、PLD结构

与阵列

或阵列

PLA

3、PLD类型

按容量分:

①、SPLD:简单可编程逻辑器件,IC管脚:24-28

②、CPLD:复杂可编程逻辑器件,IC管脚:44-160

(1)、SPLD结构

(2)、CPLD结构

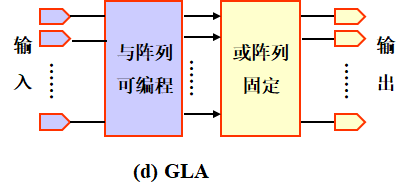

二、现场可编程门阵列FPGA

特点:不在受内部结构的限制,可以设计任何复杂的逻辑电路

1、FPGA结构

①、可组态逻辑模块CLB

②、输入/输出模块I/OB

③、可编程连线PI和由它组成的编程开关阵列PSM

2、CLB

①、可实现组合逻辑电路和时序逻辑电路

②、逻辑函数发生器

XC2064的CLB结构

3、输入/输出模块I/OB

①、提供外部封装引脚和内部信息接口电路

②、通过编程可以分别组态为输入引脚、输出引脚、双向引脚

③、可控制速率、降低功耗

4、可编程连线PI及开关阵列PSM

①、完成CLB之间逻辑连接并将信息传递到IOB

②、开关阵列PSM提供20种转换方式

③、将CLB的输出以接力方式传送到芯片任意位置

三、在系统可编程ISP

ISP:用户在自己设计的目标系统中或线路板上为重构逻辑而对逻辑器件进行编程或反复改写的能力

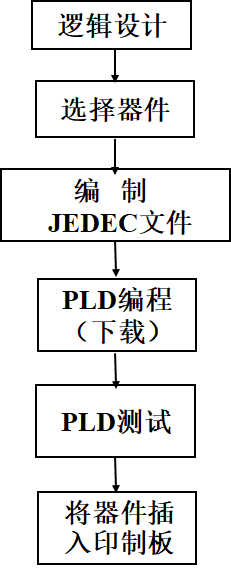

1、PLD开发过程

(1)、常规

(2)、采用ISP技术

2、ispLSI体系结构

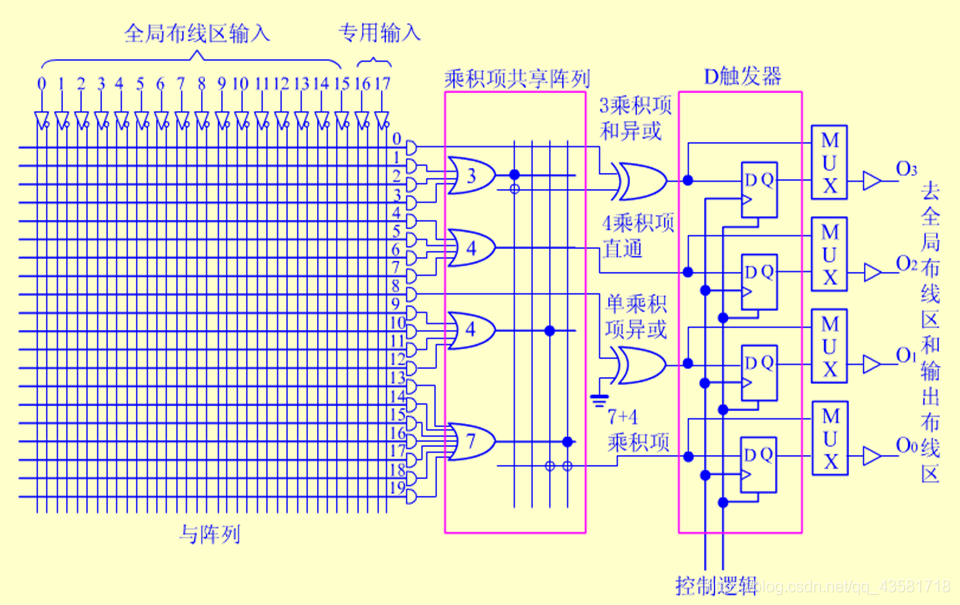

(1)、通用逻辑块GLB

GLB是ispLSI最基本的逻辑单元

GRP:以固定方式将所有内部逻辑联系在一起

GLB五种组态:

①、标准组态

最多可将20个乘积项集中于一个触发器使用

例:实现

②、高速直通组态

4个或门跨过乘积项共享阵列(PTSA)及异或门直接与4个触发器相连,以提高速度支持高速计数器

③、异或逻辑组态

4个异或门的一个输入分别是1、4、8、13,另一个则从4个或门输出中任意组合

④、单乘积项组态

将乘积项0、4、10、13分别跨过或门、PTSA直接输出,速度最快

5、多模式组态

上述4种组态可以在同一个GLB中混合使用

(2)、输出布线区ORP

可编程,介于通用逻辑块GLB和输入输出单元IOC之间

①、对ORP编程使GLB与I/O相连

②、跨过ORP使GLB与I/O直接相连:高速

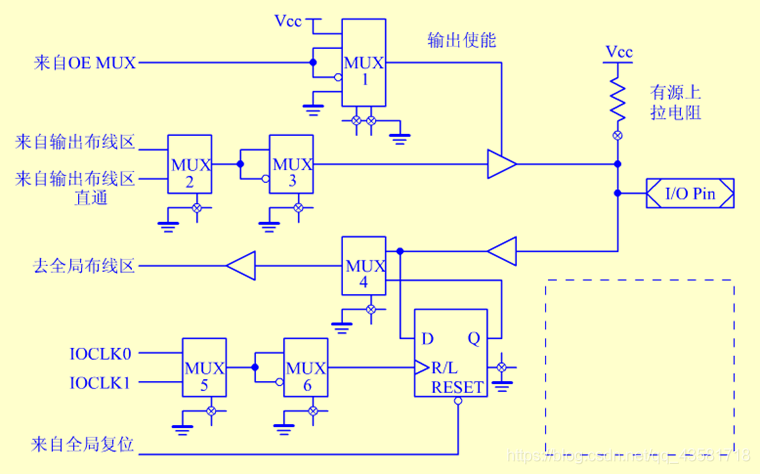

(3)、输入输出单元IOC

MUX1控制IOC处于专用输出组态、专用输入组态、I/O组态

MUX2、MUX3用来选择信号的来源和输出极性

MUX4用来选择寄存器输入还是缓冲器输入

MUX5和MUX6用来选择时钟信号和调整时钟信号的极性

IOC中触发器有两种工作方式,通过R/L端编程来确定

①、锁存方式,在时钟低电平时锁存

②、寄存器方式,在时钟信号上升沿时将信号打入

IOC共有8种组态

(4)、巨块

8个GLB、输出布线区、16个I/O单元、2个直接输入

巨块的输出使能控制

(5)、时钟分配网络CDN

输入为外部时钟信号

输出为CDN产生的内部时钟

3、信号流程