这篇文章讲一下基于JTAG 的可测性设计。

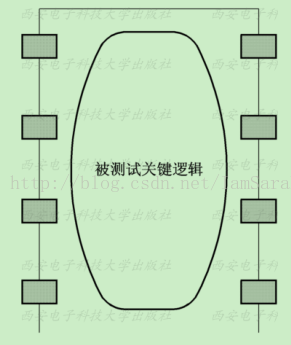

JTAG也称作边界扫描,最初是由欧洲的一些测试工程师提出的标准,该种测试技术指的是在芯片的边界上加上串行移位寄存器,以实现对芯片的测试,这种技术称为边界扫描。下图是边界扫描寄存器的原理,边界扫描单元组成扫描链将被测试设计包围了起来。

采用边界扫描技术进行测试的时候,需要进行如下的操作:

1)将测试向量载入到边界扫描单元,此操作应该串行完成

2)将边界扫描单元中的内容载入到设计中,此操作应该并行完成

3)将设计中响应移入到边界扫描单元,此操作应该并行完成

4)将响应从边界扫描单元移出,此操作应该串行完成

在一个扫描链中包括TDI和TDO接口。通过TDI接口将测试向量串行载入到边界扫描单元。然后通过边界扫描单元的并行端口,可以将边界扫描单元中的内容载入到设计中,并将设计的响应并行移入到边界扫描单元中。最后,响应可以通过边界扫描单元,经过TDO端口输出。除了TDI和TDO口,JTAG标准中还有TCK口,该端口提供边界扫描的时钟,测试向量的移入和移出都应该遵照该时钟的节拍。

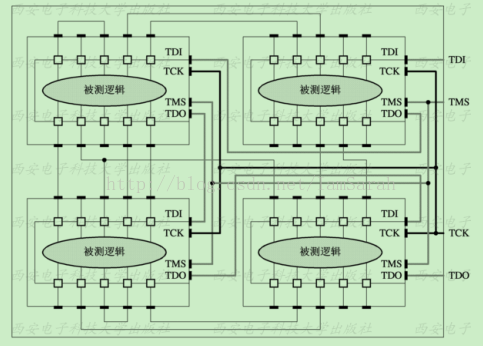

在JTAG中还加入了TMS端口,用于控制测试模式。实际上,不要仅仅将JTAG看作是一个由边界扫描寄存器组成的串行边界扫描链。 JTAG定义了许多非常灵活的功能。如在一个由多个IC组成的板级系统中,JTAG可检查其中某一个芯片的引脚连接性而忽略其他芯片。如图这是一个由4个IC组成的板级系统,各个芯片的边界扫描链依次串接在一起,如果想检查第3个芯片的连接性,通过对TMS端口进行控制就能实现。

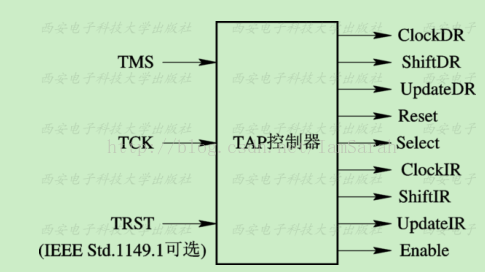

具体地说,由TMS端口输入的控制信号影响JTAG控制状态机,从而影响边界扫描链的功能。这样,在JTAG中, 除了边界扫描链,还需要状态控制器(TAP),用来控制JTAG口的状态。下图给出了一个TAP控制器的接口示意。在TAP控制器中,输入端口为TMS、 TCK和TRST。RST端口用于进行复位,低电平有效。TAP控制器的输出有ClockDR、 ShiftDR和UpdateDR等。其中, ClockIR、 ShiftIR、 UpdateIR、ClockDR、shiftDR、UpdateDR是针对数据寄存器的。此外,还包括Reset、 Select、 Enable这样的通用控制端口。

边界扫描可以通过RTL来实现,也可以由工具来完成。Synopsys的DesignWare中,用IP的形式实现了边界扫描的结构,如TAP控制器、 边界扫描单元等。设计者只需要用BSD Comiler设置边界扫描的要求,工具就会自动综合出所需的边界扫描结构,并生成测试向量。