module toggle(input T,

input clk,

output reg Q

);

always @(posedge clk )

if(T == 1) Q <= ~Q;

else Q <= Q;

endmodule

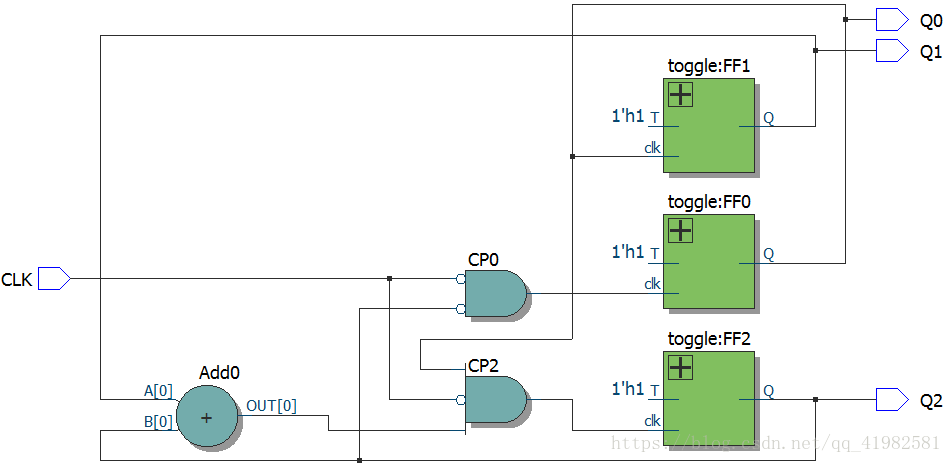

module cy4(input CLK,

output Q0,Q1,Q2

);

wire CP0;

wire CP1;

wire CP2;

assign CP0 = ~(~Q2 & ~CLK);

assign CP1 = ~Q0;

assign CP2 = ~(~CLK&(Q0&Q1+Q2));

toggle FF0(.T(1),.clk(~CP0),.Q(Q0));

toggle FF1(.T(1),.clk(~CP1),.Q(Q1));

toggle FF2(.T(1),.clk(~CP2),.Q(Q2));

endmodule

五个连续二进制编码状态的异步计数器(结构描述法)

猜你喜欢

转载自blog.csdn.net/qq_41982581/article/details/82764336

今日推荐

周排行