版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/cc214042/article/details/60766998

概述

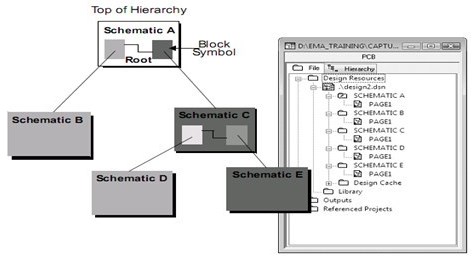

层次式电路设计(Hierarchical Design):通常是在设计比较复杂的电路和系统时采用的一种自上而下的电路设计方法,即首先在一张图纸上设计电路总体框图,然后再在另外层次图纸上设计每个框图代表的子电路结构,下一层次中还可以包括框图,按层次关系将子电路框图逐级细分,直到最低层次上为具体电路图,不再包括子电路框图。

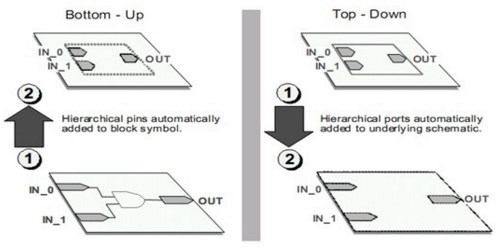

层次式原理图设计的两种方法:自下而上(Bottom-Up)和自上而下(Top-Down)。

创建层次式电路模块

1)新建层次电路图,执行菜单命令Place-->

Hierarchical Block。

2)设置层次电路图参数,Reference栏输入模块名称;在Implementation Type栏选择Schematic View,表示模块与原理图连接;在Implementation name栏输入指定的电路图名。

3)添加层次图端口,执行菜单命令Place-->Hierarchical PIN,设置端口名称,线宽和引脚类型。

4)创建模块对应的电路图页文件夹,选中层次块,单击鼠标右键,选择Descend Hierarchy,系统自动创建新的电路图页。

5)返回上层电路,在编辑好的原理图页单击鼠标右键,选择Ascend Hierarchy,弹出上层电路。

6)添加分页端口连接器,执行菜单命令Place-->Off-Page Connector,使用分页端口连接器的时,这些电路图页必须在同一个电路文件夹中,并且分页端口连接器要有相同的名字,才能保证电路图页的电路连接。

7)添加电路图I/O端口,执行菜单命令Place-->Port。

Off-page Connector与Port的区别

在平坦式电路图中:

同一张Page中只需要使用网络名Net Alias就可以连接;

在不同的Page中需要使用Place Off-page Connector来连接;

用Place Port也可以连接不同Page的网络,但必须把Port属性设置一样,例如都为input或者output,否则肯定出错。

在层次式原理图中:

不同功能的网络间连接需要使用Place Port才能正确连接。若用Off-page Connector,DRC检查会有warning。

平坦式电路图:一种基础的电路图设计方法,结构简单,所用的元件能够在一张电路图上全部表示出来。

层次式电路图:一种先进的原理图设计方法,使用符号代表功能,并且能够重复的调用。(同FPGA的verilog 语言一样)

层次式电路设计的优点

1)分工,将一个复杂的电路设计分为几个部分,分配给几个工程技术人员同时进行设计。

2)模块化,让具有不同特长的设计人员负责不同部分的设计。

3)设备限制,打印输出设备不支持幅面过大的电路图页面。

4)自上而下的设计策略,目前该策略已成为电路和系统设计的主流。

参考文献

《Cadence高速电路板设计与仿真——原理图与PCB设计》

http://old.bjdihao.com.cn/cn/download/technical-topics-allegro/orcad-tutorial/capture-hierarchical-circuit-design.html