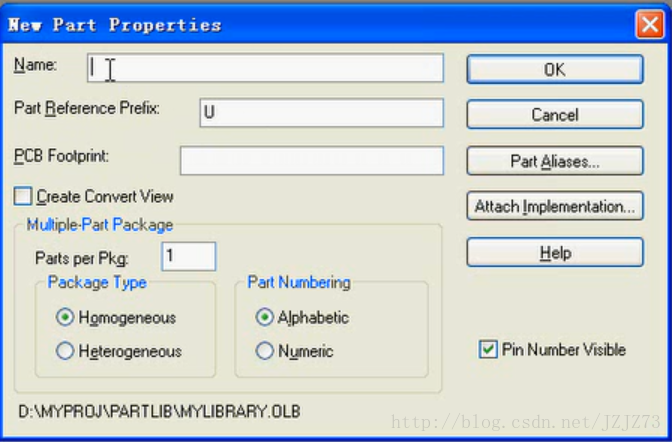

1. Library里点击New part自建元件,

从上到下依次为: 元件名,代替使用称号,封装

2. 勾选掉preference里的pointer snap to grid 可以让线的起点和终点从任意位置开始

3. 地也是一种特殊的电源,故选择pin属性时,连接地的选择power,同时所有的power都应该选择pin visible以便在原理图中可见

4. 当pin口无关输入和输出时,选择passive

5. 对part里的heterogeneous类而言,在原理图中来自于同一个元件需要相同的属性。有三步操作:

- l 在所有的小part里new一个新的property,名字任取(以package为例),但避开group这个名字,会与pcb的属性发生冲突

- l 在原理图中放置part,并调出part的property,将来自于同一个元件的package的值调为相同

- l 在tool->annotate里,找到physicalpackaging->combined property,把最后一个的值改为package

6. 在design cache里会储存之前在原理图中放置过的元件

7. 引脚悬空不接时,place -> place noconnect

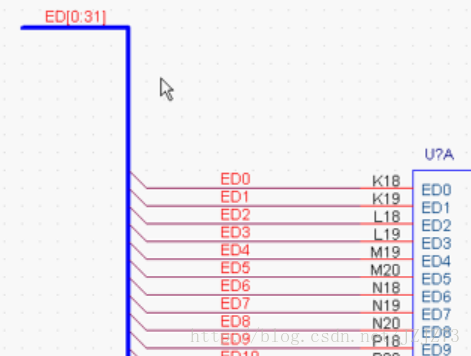

8. Place -> bus 放置总线,按住shift改变总线的方向

9. 总线命名:前为base name,后接[ ],类似于matlab,有多少写多少

10. 放置,连接总线入口,place bus entry,快捷键F4, 不可以直接连接

11. 总线和接口间,放置net alias名字来作为连接

12. 不同页面间连接,使用off-page connector

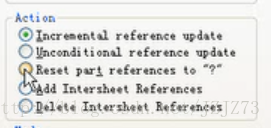

13. 从上到下(1,3),依次为annotate里对元件编号和取消编号

14. 文本编辑,Ctrl+enter 换行

15. 生成网表:

- 先对整个工程文件进行重新的索引编号,先取消,后点击上图第二个unconditional编号

- 对整个工程进行DRC检查

- 最后create netlist -> pcb editor