版权声明:本文为博主原创文章,转载请标明出处 https://blog.csdn.net/C2681595858/article/details/80811571

#5.1引言

-

局部性原理表明了在任何时间内,程序访问的只是它地址空间内相对较小的一部分。以下是两种不同的局部性:

- 时间局部性(temporal locality):如果一个数据被访问,那么在不久的将来,他可能再次被访问。

- 空间局部性(spatial locality):如果一个数据项被访问,那么与他地址相邻的数据项也可能很快被访问。

- 时间局部性(temporal locality):如果一个数据被访问,那么在不久的将来,他可能再次被访问。

-

大部分程序包含循环结构,因此这部分指令和数据将被重复访问,这体现出了很高的时间局部性。程序时顺序执行的,这体现出了很高的空间局部性。

-

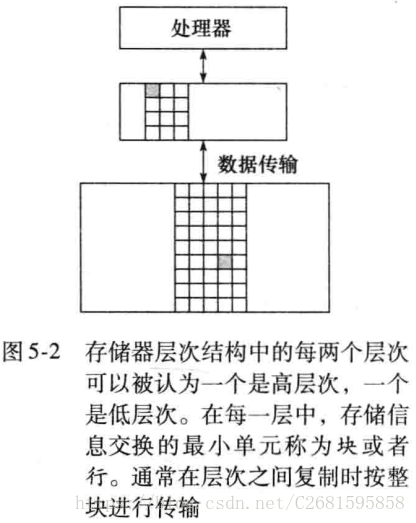

存储器层次结构:一种由多存储器层次组成的结构,存储器的容量和访问时间,随着里处理器距离的增加而增加。

-

存储器层次结构由多层构成,但是数据每次只能在相邻两个层次之间复制,我们将一个两级层次中存储信息交换的最小单元称为块。

-

如果处理器需要的数据存放在高层存储器中的某个块中,则称为一次命中。

-

如果在高层存储器中没有找到所需要的数据,那么这次数据请求称为一次缺失。

-

命中率:在高层存储器中找到数据的存储访问比率。(存储器层次结构性能的衡量标准)

-

缺失率:在高层存储器中没有找到目标数据的存储访问比率。

-

命中时间:访问某存储器层次结构,所需要的时间,包括了判断当前访问是命中还是缺失所需要的时间。

-

缺失代价:将相应的块从底层存储器替换到高层存储器所需要的时间。包括访问块,将数据逐层传输,将数据插入缺失发生的层,将信息块传递给请求者的时间。

-

在很多系统中,存储器是一个真实的层次结构,这意味着除非数据在第i+1层存在,否则绝不可能在第i层存在。

#5.2存储器技术 -

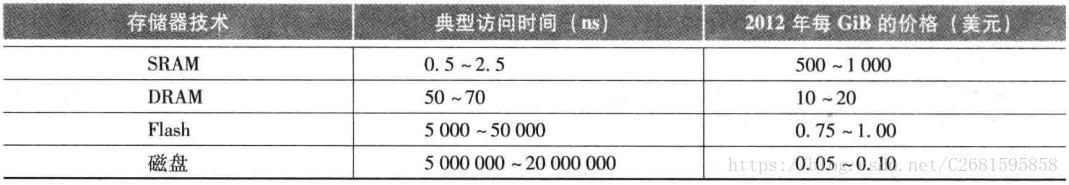

目前构建存储器层次结构有四种技术。

- 主存储器由DRAM(动态随机存取存储器)实现

- 靠近处理器的那层(cache)用SRAM(静态随机存取存储器)实现,DRAM比SRAM低一级。

- 第三种技术是闪存,是非易失性存储器,用作个人移动设备中的二级存储器。

- 第四种技术是磁盘,容量最大,速度最慢。

具体如下表:

5.2.1SRAM技术

- SRAM是一种组织成存储阵列结构的简单集成电路,通常具有一个读写端口。虽然读写访问时间可能不同,但SRAM对任何数据访问时间都是固定的。

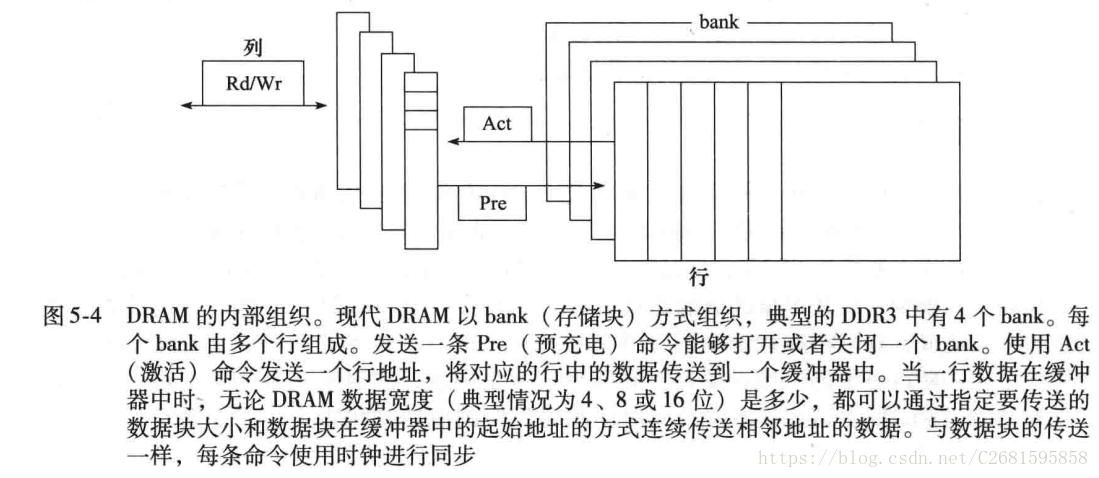

5.2.2DRAM技术

- 只要给SRAM加电,其中的数据就会保持。

- 而在DRAM中,存储器单元使用电容保存电荷的方式来存储数据。由于DRAM在电容上保持电荷,因此不能长久的保持数据,从而必须周期性的刷新。

- 为了对单元进行刷新,只需要读出其内容,然后写回即可。DRAM中的电荷可以保持几微秒。

- 行结构不但有助于刷新,还有助于性能的提高。缓冲器与SRAM相似:在下一行被访问之前,可通过改变地址来访问缓冲器中的任何一个比特位。

- 为了进一步优化与处理器的接口,DRAM增加了时钟,因此称之为同步DRAM,简写为SDRAM。

流基准程序:测试cache之外存储器系统性能的方法。它没有时间局部性,并且他们访问的阵列要比测试的计算机中的cache要大。

5.2.3闪存

- 是一种电可擦除的可编程只读存储器(EEPROM)。

对闪存的写操作可以使存储位损耗。 - 损耗均衡:闪存将写操作从已经写入很多次的块中映射到写入次数较少的块中。

##5.2.4磁盘存储器 - 当今磁盘直径一般是2.5~3.5英寸。

- 磁盘每个面通常有几万条磁道。每条磁道同样被划分成用于存储信息的扇区,每条磁道有几千个扇区,每个扇区的容量通常是512~4096字节。

- 扇区是磁盘上读写的最小单位。

- 平均旋转延时通常是磁盘转动一周时间的一半。

- 磁盘与半导体存储器技术的差别是:访问速度慢。与闪存类似,磁盘是非易失的,缺不存在写损耗问题。

5.3cache的基本原理

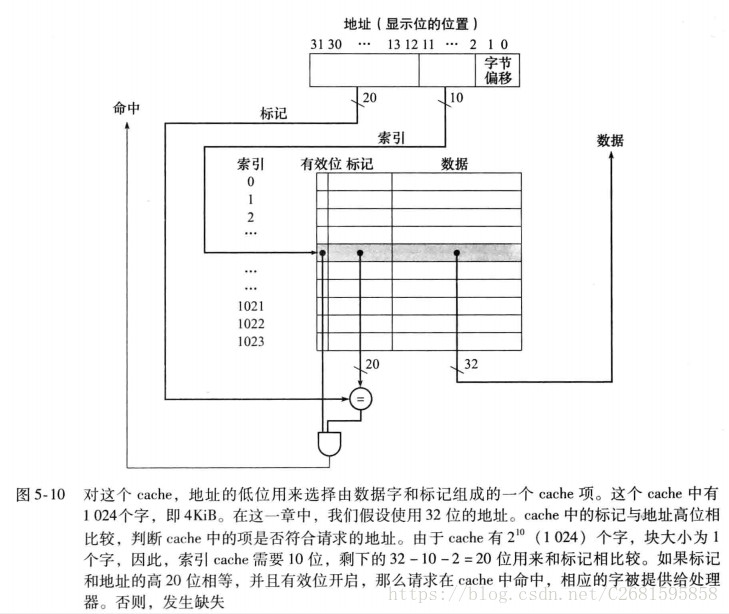

- 直接映射:一种cache结构,其中每个存储器地址仅仅对应到cache中的一个位置。

(块地址)mod(cache中的块数) - 如果cache中的块数是2的幂,取模的计算就很简单,只需要取地址的低 位。

- 由于cache中的一个位置对应主存中的多个位置,所以还要设置标记来表明cache中存储的到底是哪个位置的数据。

- 我们还需要一个办法来确定cache中的数据是否有效,就是说这个标记位是不是我因为需要而从主存中拿进来的数据,所以设置一个有效位来标明这个存储位置是否有效。

- 由于cache不仅存储数据,也存储标记位,cache所需要的位数是cache大小和地址位数的函数。

- 上文提及的一个块中只有一个字,但通常块大小为多个字。如下面这种情况:

- 32位地址。

- 直接映射cache。

- cache映射大小为 个块,因此n位被用来索引。

- 块大小是 个字( 字节),因此m位用来查找块中的字,两位是字节偏移信息。

- 标记域大小为32 - (n+m+2)。

- 直接映射的cache总位数为: 。所以上述这样一个cache的位数为

- 1KiB = 1024KB

- 首先确定在主存中是哪一块,然后在对应到cache中。

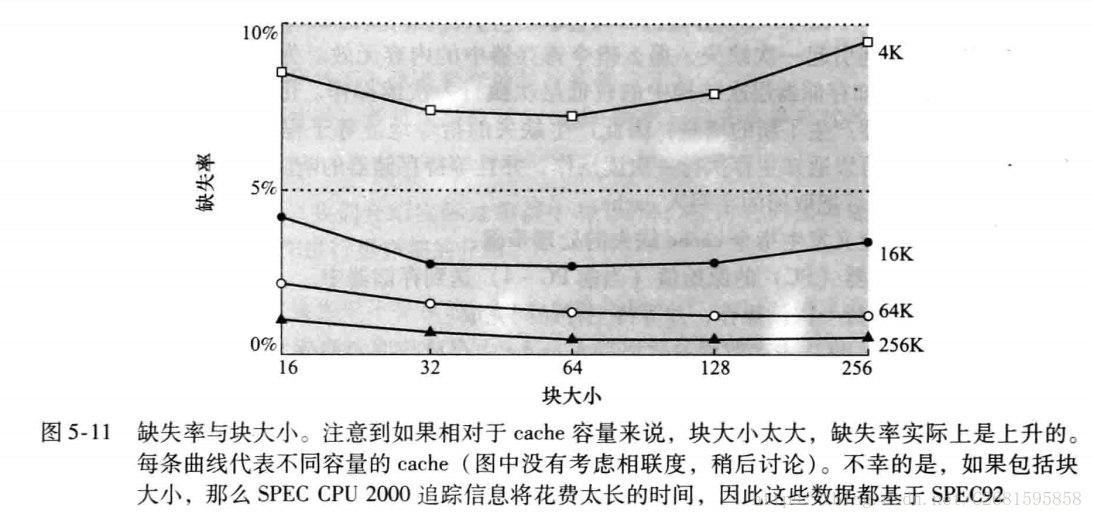

- 较大的cache块能够更好地利用空间局部性,以降低缺失率。增加块大小通常会引起缺失率下降。但当块大小在cache容量中所占比例增加到一定程度时,缺失率也随之增加。这是因为此时cache中块的数量变得很少,对于这些块将会有大量的竞争发生,结果就造成一个块中数据在被多次访问之前就替换出cache。另一方面,对于较大的块,块的各个字之间的空间局部性也会降低,缺失率降低所带来的益处也会减少。

- 仅仅增加块的大小所带来的后果是缺失成本的增加。由较低存储器取出块,放至cache中的时间决定了缺失代价。

5.3.2cache缺失处理

- 发生指令cache缺失的处理步骤:

- 把程序计数器的原始值送到存储器中

- 通知主存执行一次读操作,并等待主存访问完成。

- 写cache项,将主存取回的数据写入cache中存放数据的部分,将地址的高位写入标记域,设置有效位。

- 重启指令执行第一步,重新取指,这次该指令在cache中。

- 数据访问对cache的控制基本相同:发生缺失时,处理器发生阻塞,直到从存储器中取回数据后才响应。

5.3.3写操作处理

- **写直达:**当发生数据修改时,同时修改cache和主存中的数据。

- 另一个需要考虑的方面是,写缺失。我们首先从主存中取出块中的字。数据块被取回并写入cache中后,将发生缺失的字重新写入cache中。同时我们使用全地址将该字写入主存。