5.4 Measuring and Improving Cache Performance

Cache association

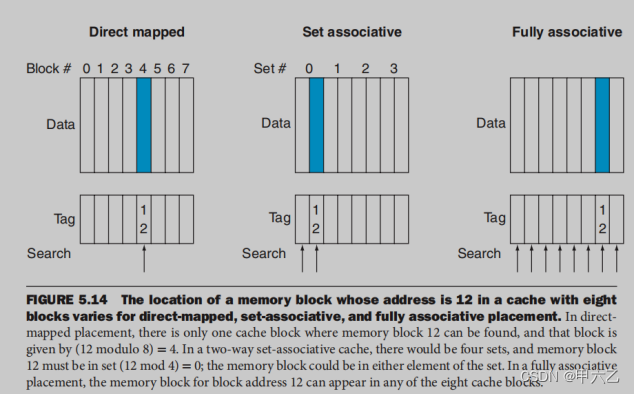

Cache line的映射方式主要有三种:directed mapping、full associative、set associative。

可以通过灵活的映射方式来reducing miss rate。

Directed mapping:

每个memory block只能存在cache中一个cache line。

每次加载一个新的memory block,都要把某个cache line替换掉,miss rate较大。

Full associative:

每个memory block可以存放在cache中的所有的cache line。

在确定cache是否hit的时候,需要较多的硬件资源;一般适用于cache line number较少的cache。

Set-associative 组相连

一般是n-way set associative(n路组相连)。

每个set有n个cache line组成,每个memory block可以放在某个set的任何一个cache line中。

Way代表一个memory block可以放在几个cache line中。

从另一个角度来说,三种mapping方式都是set -associative,只不过way不同

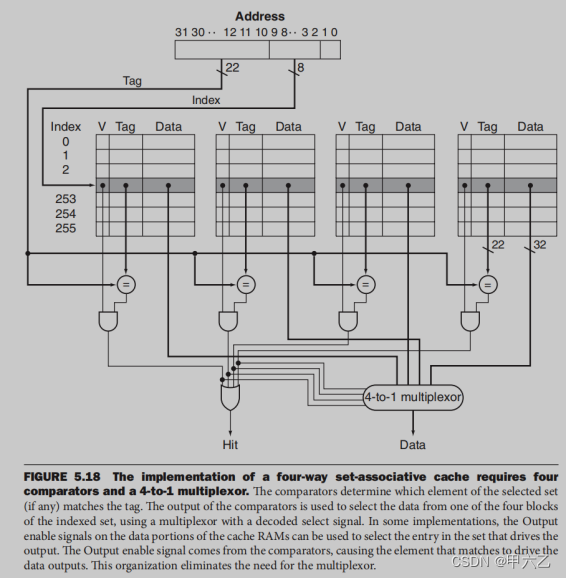

Locating block in set associative cache

在set associative cache中,地址中的index field是用来索引哪个set的,到底是set中的哪个cache line还要通过比对tag来决定。对比tag的过程是同时进行的——如果是4 way,那么需要四个比较器。

下图中是4way cache,共有256个set。

Replacing block strategy

一般是LRU(least recently used)

Reducing the Miss Penalty Using Multilevel Caches

In particular, a two-level cache structure allows the primary cache to focus on minimizing hit time to yield a shorter clock cycle or fewer pipeline stages, while allowing the secondary cache to focus on miss rate to reduce the penalty of long memory access times.

the primary cache of a multilevel cache is often smaller. Furthermore, the primary cache may use a smaller block size, to go with the smaller cache size and also to reduce the miss penalty.

In comparison, the secondary cache will be much larger than in a single-level cache, since the access time of the secondary cache is less critical.With a larger total size, the secondary cache may use a larger block size than appropriate with a single-level cache. It often uses higher associativity than the primary cache given the focus of reducing miss rates.

参考:

1. 计算机组成与设计 第五版 ARM版