https://blog.csdn.net/xuecz1230/article/details/78672662

msm8953支持4路串口,编号uart2、uart4、uart5、uart6

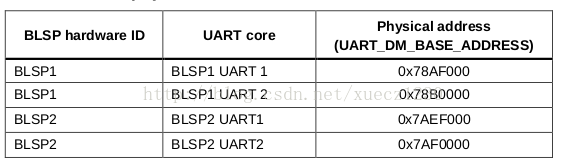

基地址:

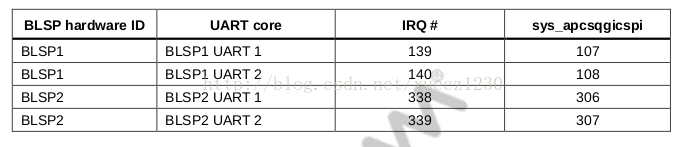

中断号:

dts配置如下;

xxx .dtsi

-

&blsp1_uart0 {//uart2 -

status = "ok"; -

pinctrl-names = "default"; -

pinctrl-0 = <&uart_console_active>; -

}; -

&blsp1_uart4 {//uart4 -

status = "ok"; -

pinctrl-names = "default"; -

pinctrl-0 = <&uart4_console_active>; -

}; -

&blsp2_uart5 {//uart5 -

status = "ok"; -

pinctrl-names = "default"; -

pinctrl-0 = <&uart5_console_active>; -

}; -

&blsp2_uart6 {//uart6 -

status = "ok"; -

pinctrl-names = "default"; -

pinctrl-0 = <&uart6_console_active>; -

};

xxx-msm8953.dtsi

-

blsp1_uart0: serial@78af000 {//uart2 -

compatible = "qcom,msm-lsuart-v14"; -

reg = <0x78af000 0x200>; -

interrupts = <0 107 0>; -

status = "disabled"; -

clocks = <&clock_gcc clk_gcc_blsp1_uart1_apps_clk>, -

<&clock_gcc clk_gcc_blsp1_ahb_clk>; -

clock-names = "core_clk", "iface_clk"; -

}; -

blsp1_uart4:serial@78b0000 {//uart4 -

compatible = "qcom,msm-lsuart-v14"; -

reg = <0x78b0000 0x200>; -

interrupts = <0 108 0>; -

status = "disabled"; -

clocks = <&clock_gcc clk_gcc_blsp1_uart2_apps_clk>, -

<&clock_gcc clk_gcc_blsp1_ahb_clk>; -

clock-names = "core_clk", "iface_clk"; -

}; -

blsp2_uart5:serial@7aef000 {//uart5 -

compatible = "qcom,msm-lsuart-v14"; -

reg = <0x7aef000 0x200>; -

interrupts = <0 306 0>; -

status = "disabled"; -

clocks = <&clock_gcc clk_gcc_blsp2_uart1_apps_clk>, -

<&clock_gcc clk_gcc_blsp2_ahb_clk>; -

clock-names = "core_clk","iface_clk"; -

}; -

blsp2_uart6:serial@7af0000 {//uart6 -

compatible = "qcom,msm-lsuart-v14"; -

reg = <0x7af0000 0x200>; -

interrupts = <0 307 0>; -

status = "disabled"; -

clocks = <&clock_gcc clk_gcc_blsp2_uart2_apps_clk>, -

<&clock_gcc clk_gcc_blsp2_ahb_clk>; -

clock-names = "core_clk","iface_clk"; -

};

xxx-msm8953-pinctrl.dtsi

-

pmx-uartconsole {//uart2 -

uart_console_active: uart_console_active { -

mux { -

pins = "gpio4", "gpio5"; -

function = "blsp_uart2"; -

}; -

config { -

pins = "gpio4", "gpio5"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

uart_console_sleep: uart_console_sleep { -

mux { -

pins = "gpio4", "gpio5"; -

function = "blsp_uart2"; -

}; -

config { -

pins = "gpio4", "gpio5"; -

drive-strength = <2>; -

bias-pull-down; -

}; -

}; -

}; -

pmx-uart4console {//uart4 -

uart4_console_active: uart4_console_active { -

mux { -

pins = "gpio12","gpio13"; -

function = "blsp_uart4"; -

}; -

config { -

pins = "gpio12","gpio13"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

uart4_console_sleep: uart4_console_sleep { -

mux { -

pins = "gpio12","gpio13"; -

function = "blsp_uart4"; -

}; -

config { -

pins = "gpio12","gpio13"; -

drive-strength = <2>; -

bias-pull-down; -

}; -

}; -

}; -

pmx-uart5console {//uart5 -

uart5_console_active: uart_console_active { -

mux { -

pins = "gpio16","gpio17"; -

function = "blsp_uart5"; -

}; -

config { -

pins = "gpio16","gpio17"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

uart5_console_sleep: uart5_console_sleep { -

mux { -

pins = "gpio16","gpio17"; -

function = "blsp_uart5"; -

}; -

config { -

pins = "gpio16","gpio17"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

}; -

pmx-uart6console {//uart6 -

uart6_console_active: uart_console_active { -

mux { -

pins = "gpio20","gpio21"; -

function = "blsp_uart6"; -

}; -

config { -

pins = "gpio20","gpio21"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

uart6_console_sleep: uart6_console_sleep { -

mux { -

pins = "gpio20","gpio21"; -

function = "blsp_uart6"; -

}; -

config { -

pins = "gpio20","gpio21"; -

drive-strength = <2>; -

bias-disable; -

}; -

}; -

};