目录

2.1 处理器系统

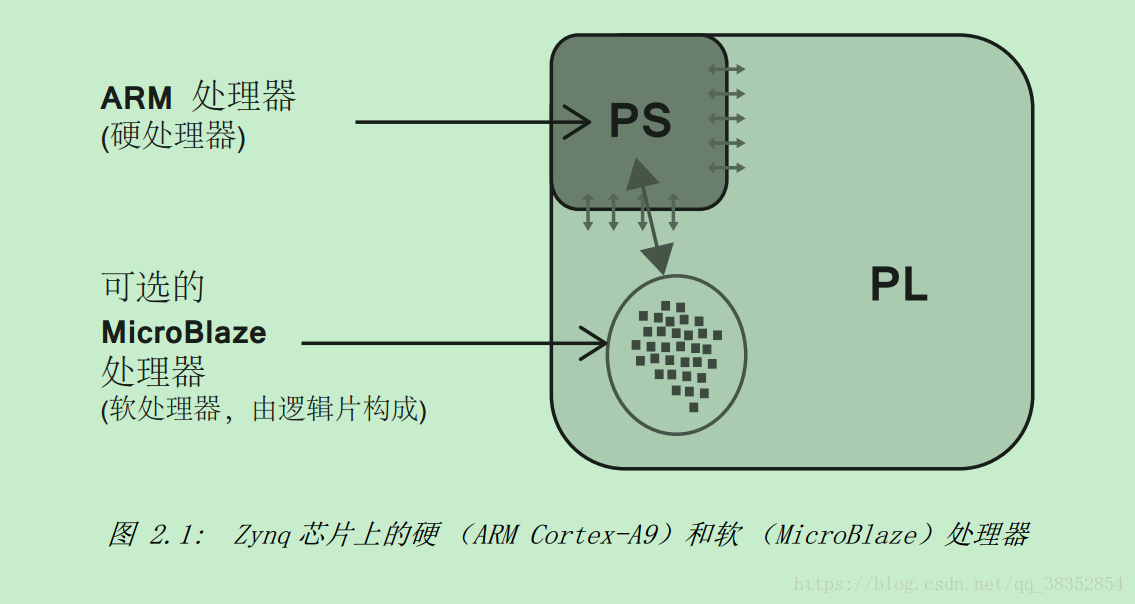

这里的处理器系统通常指的是PS部分的“硬”处理器,与之相似的有PL部分的软处理器——例如Microblaze,二者最大的区别在于,“硬”处理器是芯片上专用且优化过的硅片元件,而软处理器是由可编程逻辑单元组成的,实质上与IP核是等价的,其最大的特点就是灵活。“硬”处理器是固定的,它有固定的架构和指令集,具有很好的性能,可以更好的实现控制和应用程序的功能。zynq中有时也使用Microblaze和ARM协同工作。

ARM处理器以及相关的处理单元

2.1.1 应用处理器单元(APU的基本结构)

NEON引擎实现单指令多数据(Single Instruction Mutiple Data,SIMD)来实现媒体和DSP类算法的加速战略。

2.1.2 关于ARM模式

zynq7000中使用的是ARM Cotex A9 中的r3p0版本, 是基于ARM V7-A架构的, 所以在参考ARM的资料时需要注意这一点

2.1.3 处理器系统外部

PS部分和外部的通信主通过两种接口来实现:一、MIO 直接与外部相连接 二、EMIO通过与PL部分相连接然后再与外部相连接。

2.2 可编程逻辑

2.2.1 逻辑部分

逻辑部分:CLB、开关矩阵

CLB: 包含两个逻辑片(Slice)

Slice: 查找表(LUT)、触发器(FF)

2.2.2 特殊资源:DSP48E1和块RAM

满足密集存储的块RAM和用于高速算术的DSP48E1片,DSP48E1片实现对长字长的高速算术运算。

2.2.3 通用输入/输出

zynq上的通用输入/输出功能(IOB)合起来被称作SelectIO资源,它们被组织成50个IOB一组。

2.2.4 通信接口

Zynq芯片里含有嵌入在逻辑部分里的GTX收发器和高速通道块,这些都是专用的硅片块(“硬IP”块)

,能支持一些标准接口,包括PCI Express、串行RapidIO、SCSI和SATA。

2.2.5 其他可编程逻辑扩展接口

模拟--数字转换:12位,采样率为1M

时钟--PL接收来自PS的四个独立的时钟输入,另外还能产生和分发它自己的与PS无关的时钟信号。

编程与调试—在PL部分实现了一组JTAG端口来实现对PL的配置和调试。

2.3 处理器系统与可编程逻辑的接口

zynq中通过一组高度定制的AXI互联和接口用来在两个部分之间的桥梁,另外,在PS和PL之间还有一些其他类型的连接,特别是EMIO。

2.3.1 AXI标准

AXI是高级可扩展接口(Advanced eXtensible Interface),当前的版本是AXI4, 它是ARM AMBA3.0开放标准的一部分。

实际上有三类AXI4,每一类代表了一种不同的总线协议,对于特定的连接选择哪个AXI总线协议是基于那个连接所需的特性的。

AXI4[2]--用于存储映射链接,支持的最高性能是:通过一簇高达256个数据字(或“数据拍(data beats)”)的数据传输来给定一个地址。

AXI-Lite[2]--一种简化了的链接,只支持每次连接传输一个数据(非批量)。AXI4-Lite也是存储映射的,这种协议下每次传输一个地址和单个数据。

AXI4-Stream[1]--用于高速流数据,支持批量传输无限大小的数据。没有地址机制,这种总线类型最适合源和目的地之间的直接数据流(非存储器映射)。

2.3.2 AXI互联和接口

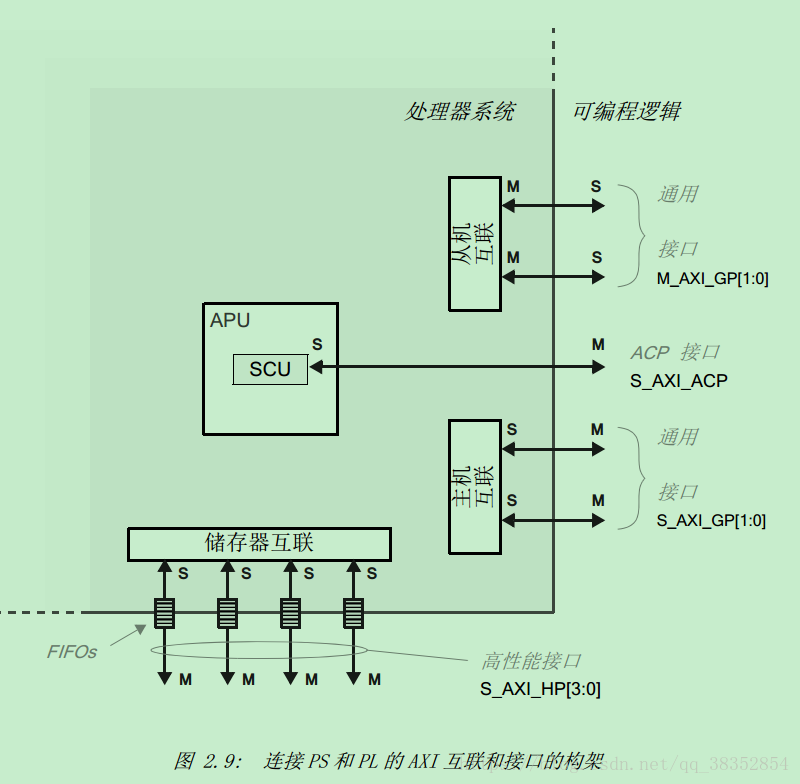

互联(Interconnect)—互联实际上是一个开关,管理并直接传递所连接的AXI接口之间的通信。用于PS内部的连接以及PS和PL内部的互联。

接口(Interface)—用于系统内的主机和从机之间传递数据、地址和握手信号的点对点连接。

通用AXI(General Purpose AXI)--一条32位数据总线,适合PL和PS之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个PL做主机,另两个PL做主机。

加速器一致性端口(Accelerator Coherency Port)---在PL和APU内的SCU之间的单个异步连接,总线宽度为64位。这个端口用来实现APU cache和PL的单元之间的一致性。PL是做主机的。

高性能端口(High Performance Ports)--四个高性能AXI接口,带有FIFO缓冲来提供“批量”读写操作,并支持PL和PS中的存储器单元的高速率通信。数据宽度是32位或64位,在所有四个接口中PL都是做主机的。

2.3.3 EMIO接口

从PS出来,有几种连接可以经由PL到外部接口上,这被称作扩展的MIO(Extended MIO),即EMIO.

2.3.4 其他PL-PS信号

跨越PS-PL边界的其他信号包括看门狗定时器、重启信号、中断信号和DMA接口信号。

2.4 安全

2.4.1 安全引导

处理器在启动的时候,从存储器核中配置PL,通过限制引导为单一来源,就确保了不可能在PL已经配置之后再有人工的方法来装在恶意的软件,同时在处理器已经初始化之后也没有办法再装在恶意的映像到PL中去。

2.4.2 硬件支持

zynq-7000芯片都受益于内置的硬件安全IP,这个安全IP既可以是PS内的硬IP包,也可以是PL内的软IP。