-

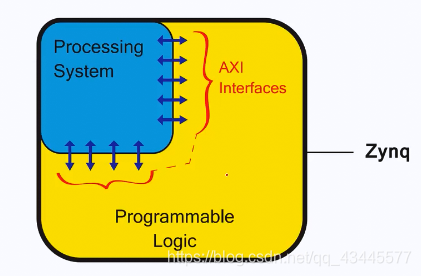

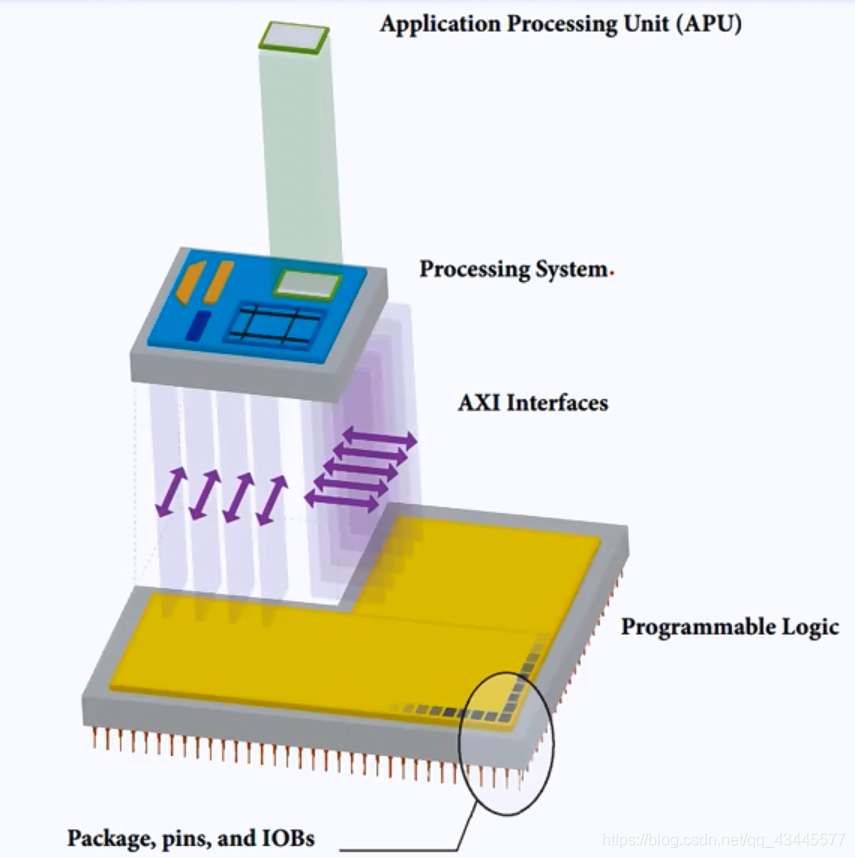

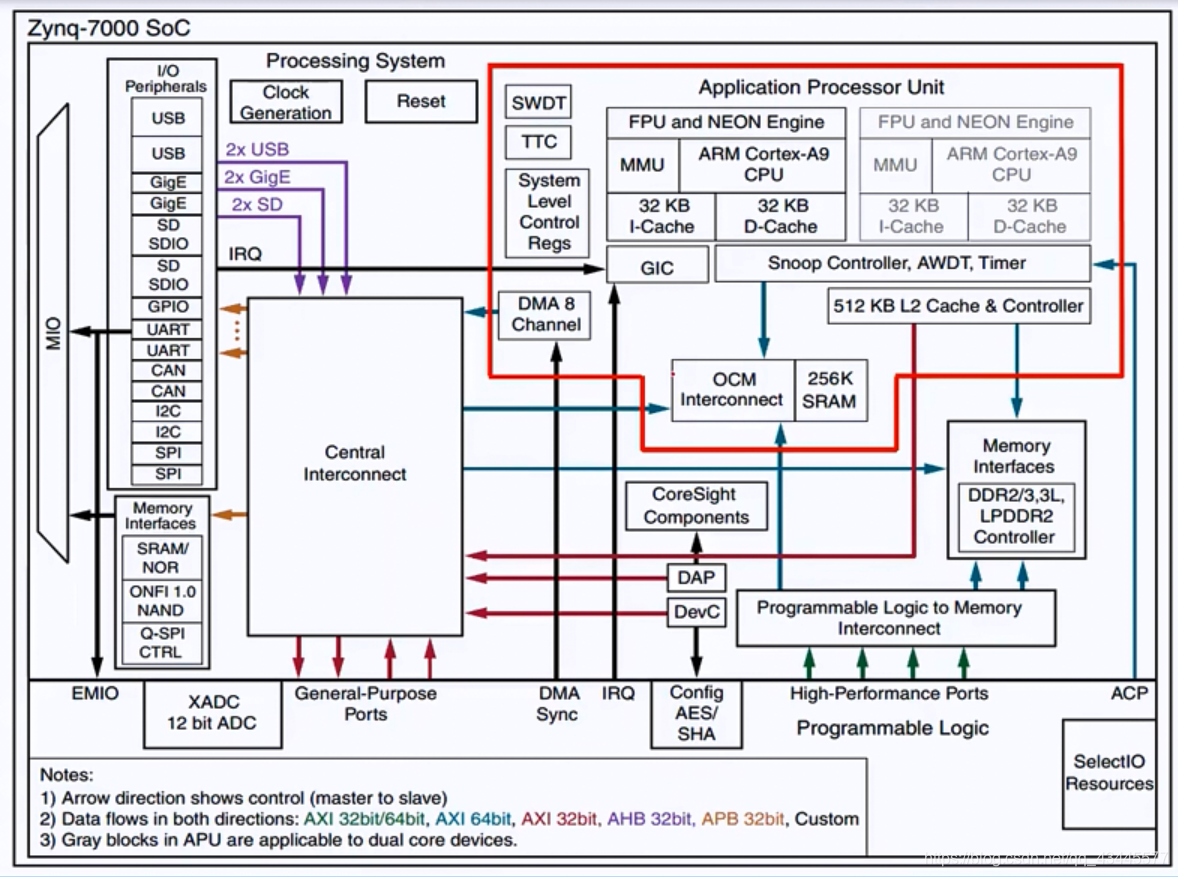

ZYNQ的本质特征就是组合了一个双核ARM Cortex A9处理器和一个FPGA

-

ALTERA的NIOS SOPC,可编程片上系统,使用FPGA内部逻辑资源实现的处理器,比较灵活,可以灵活配置处理器以及外围设备。但是使用FPGA资源搭建的处理器性能不高。

-

XILINX的ZYNQ是All-Programmable SOC,全可编程片上系统。在芯片内部集成了一个硬核处理器,实实在在存在一个ARM处理器,性能大大提升(可以运行Linux操作系统)。对于高速运算可以用FPGA运算。

-

-

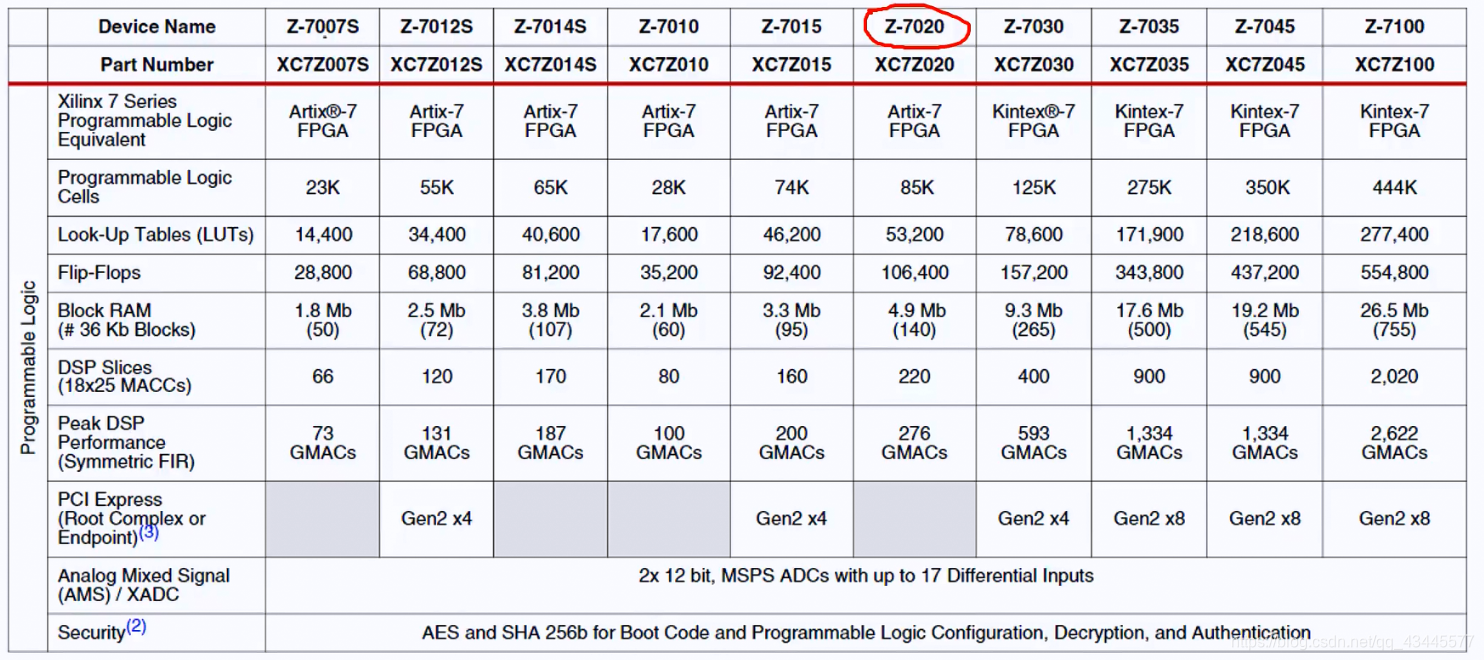

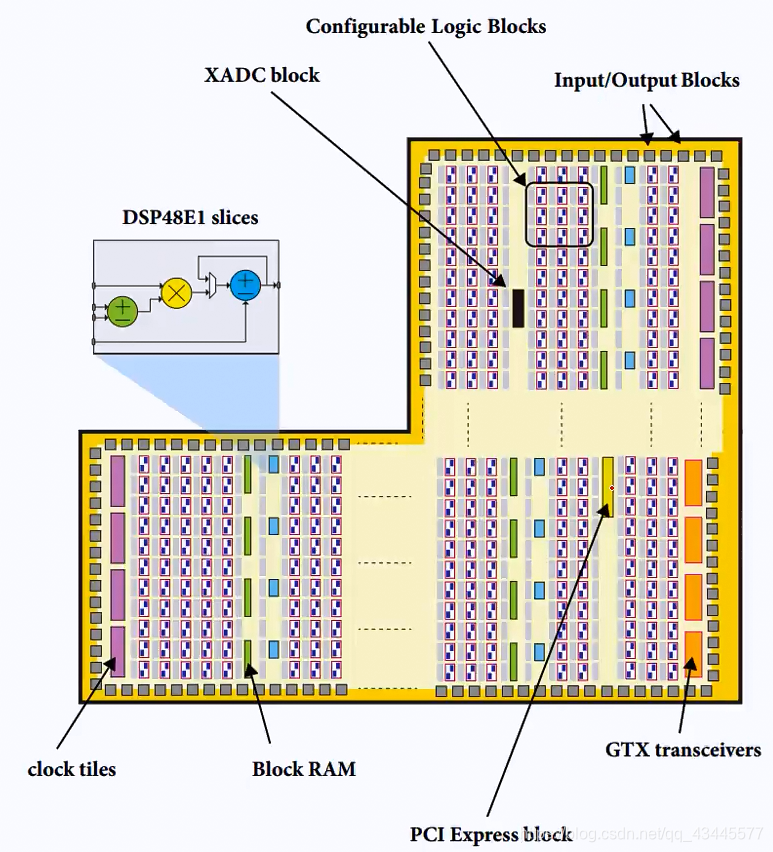

ZYNQ的PL部分

- 等价于FPGA

- 等价于FPGA

-

PS部分

-

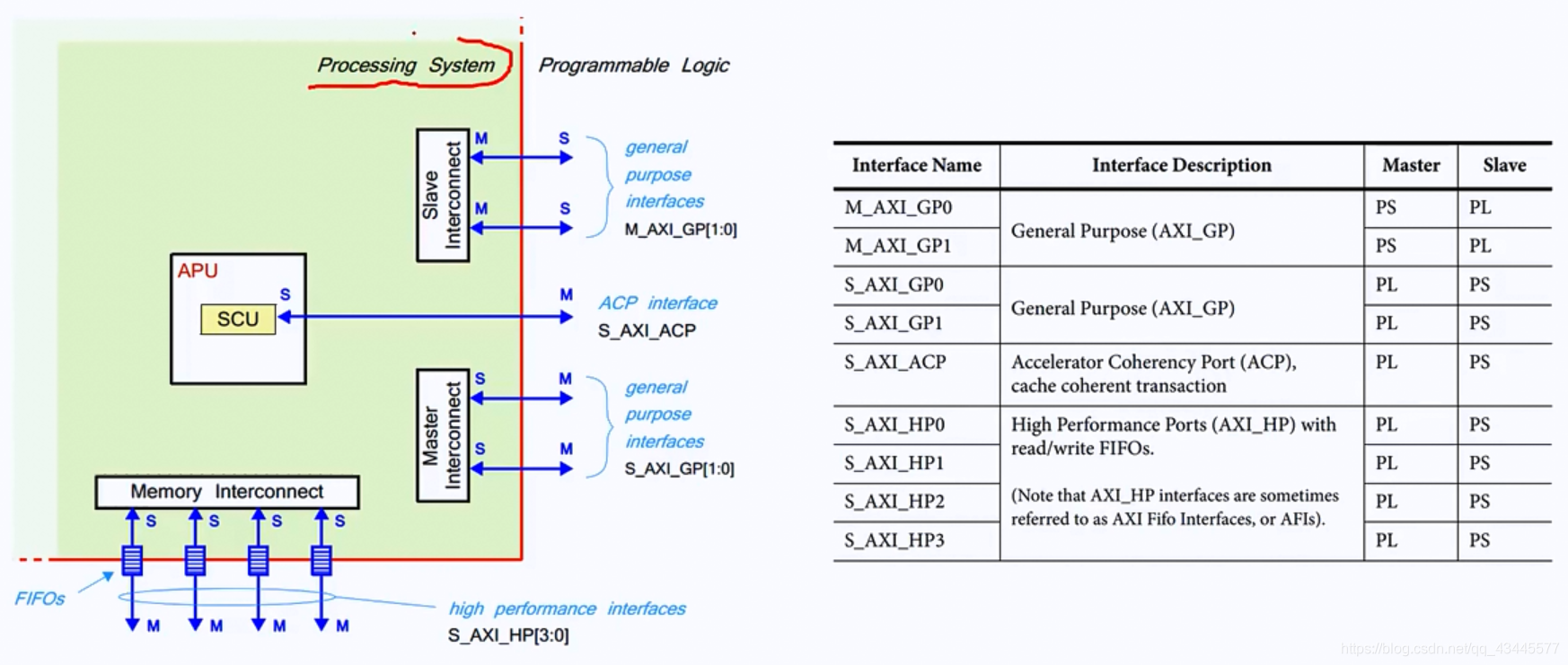

双核ARM Cortex A9处理器+外围资源(外设,存储器接口,AXI接口)

-

xilinx zynq7 使用 sdk(arm端) 无串口uart 在线调试 输出

前提:板子上没有其他模块占用uart口

使用sdk,程序中使用 xil_print

打开项目bsp setting 页面

打开 configuration for OS standalone 设置页面

选择std_in 和 std_out,设置value为ps7_coresight_comp0(非uart的选项)。保存后bsp文件会重新生成。

run/debug 项目

选择控制台输出窗口为TCF-Debug Virtual Terminal - ARM cortex-A9 MPcore#0(自己使用的core) -

-

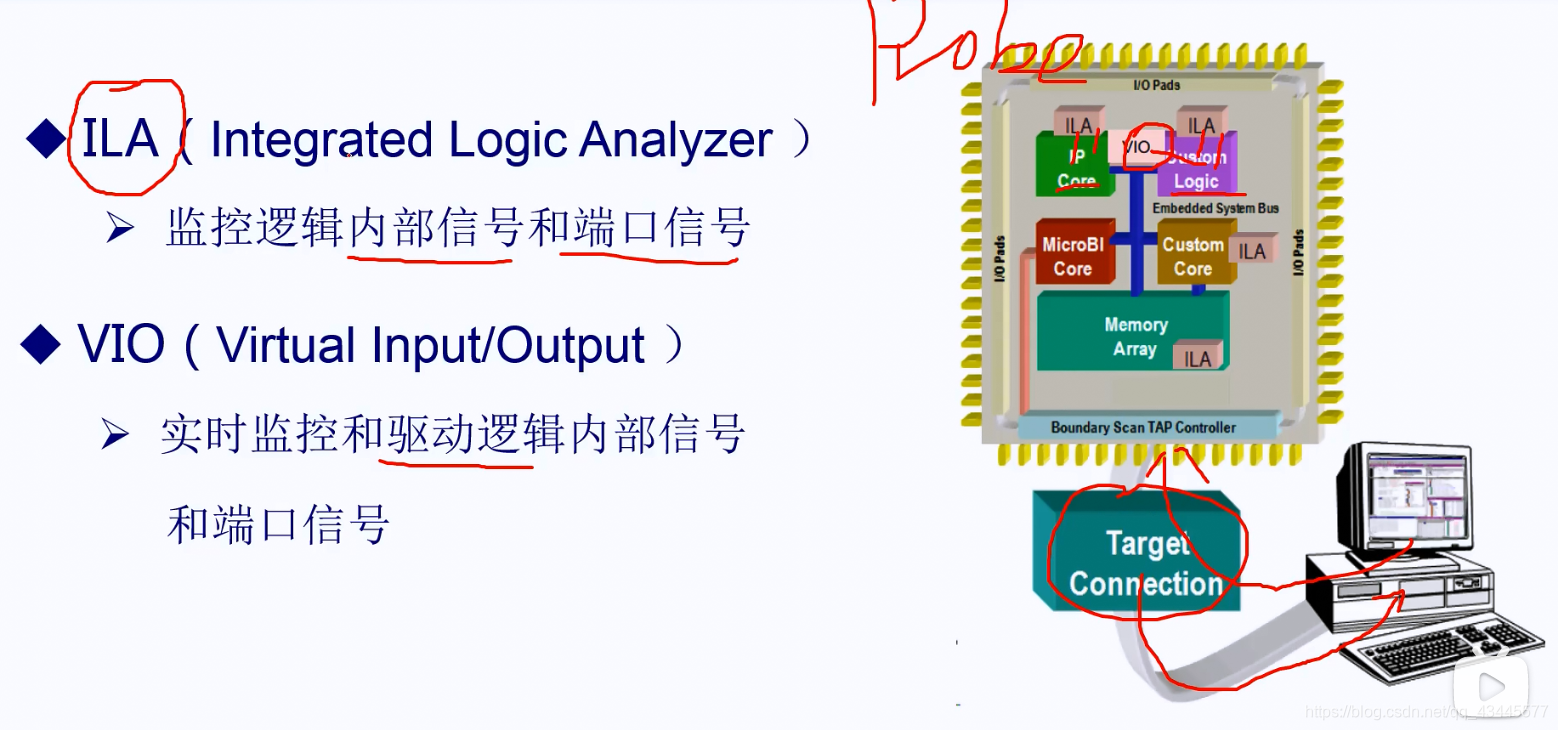

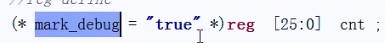

若reg信号会被优化掉一部分,那么可以通过如下方式进行设置,为其添加debug的属性,防止被优化。但是这个只有在debug时候有用,正常生成bit流不会受到影响。

-

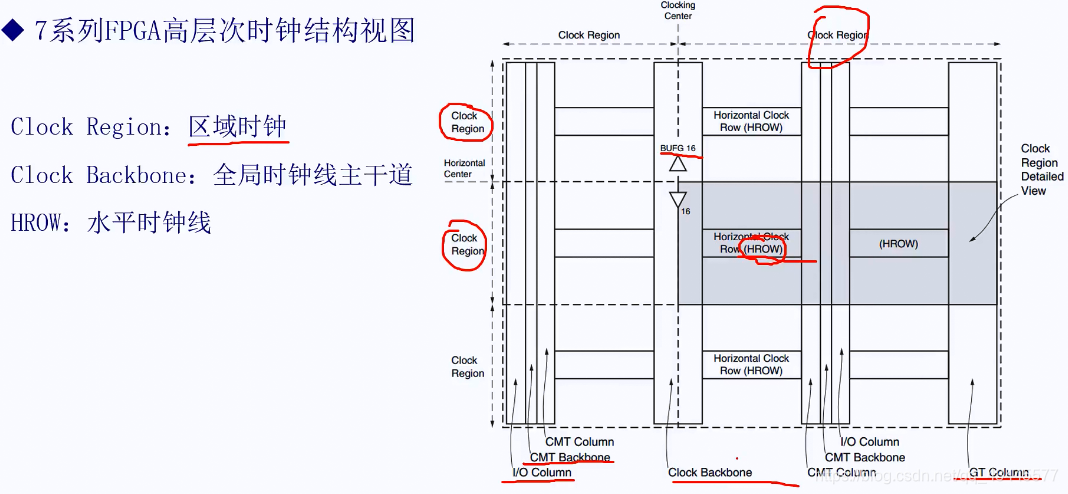

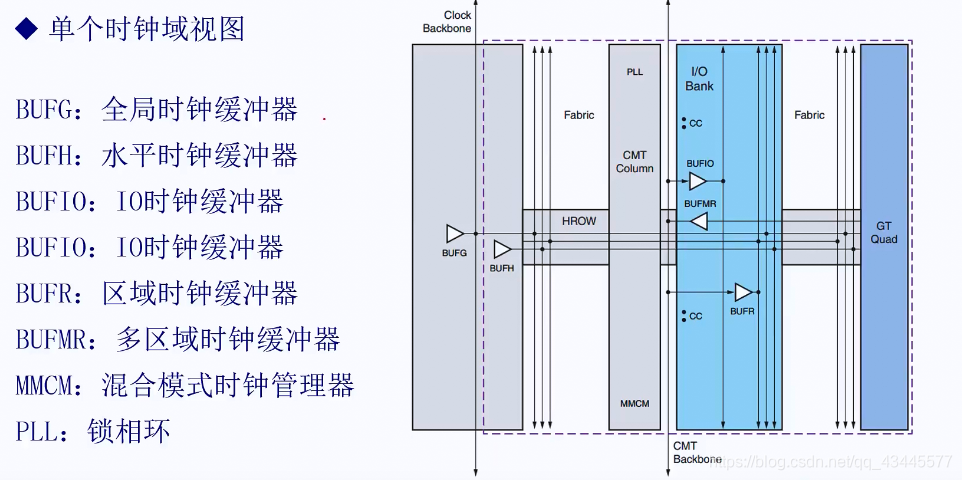

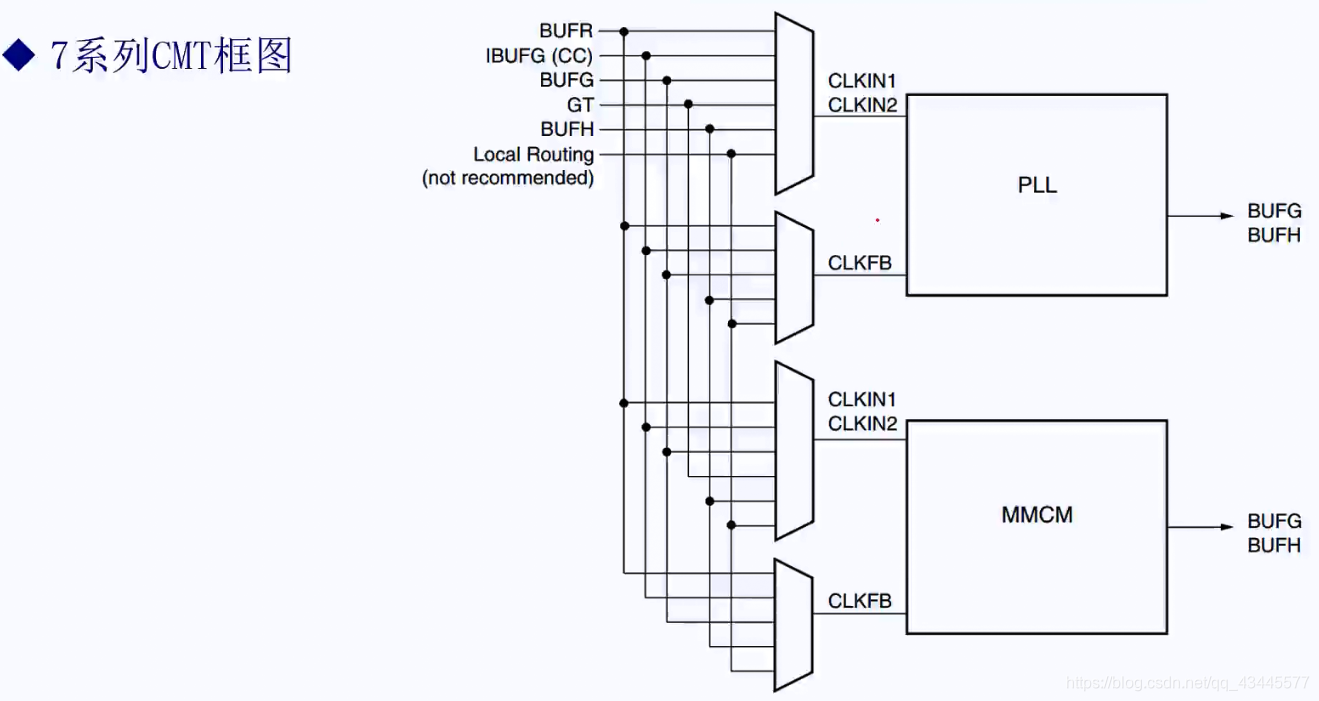

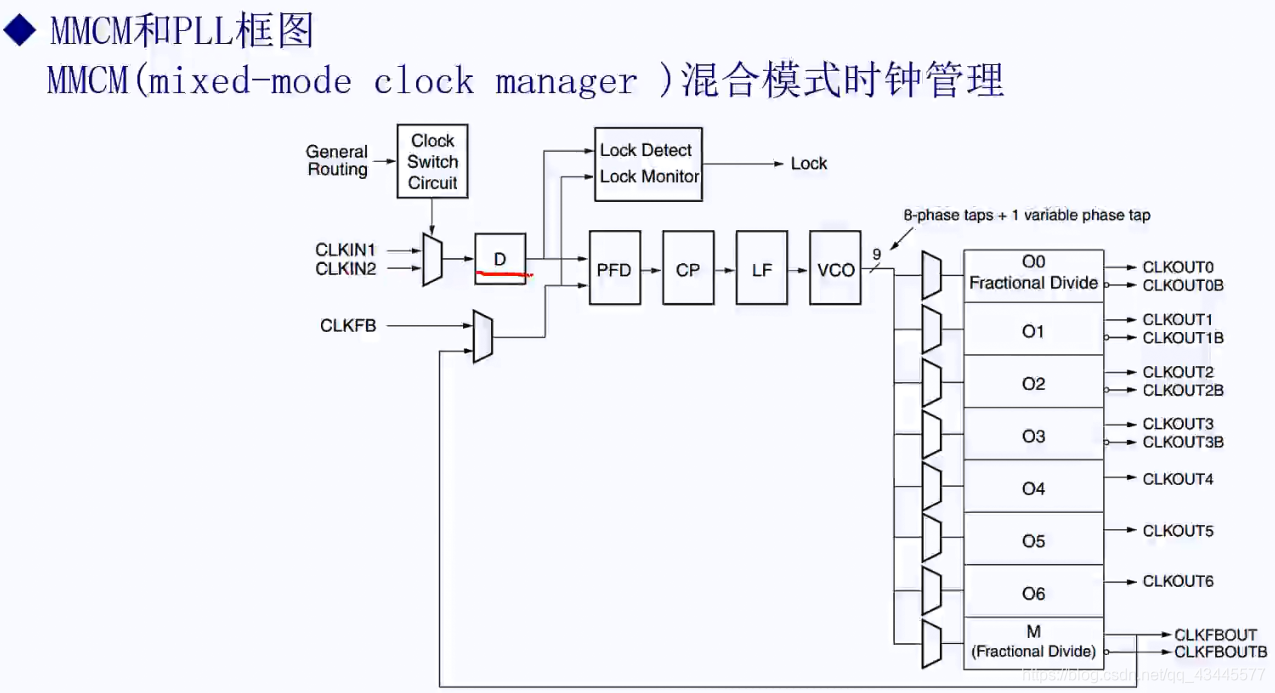

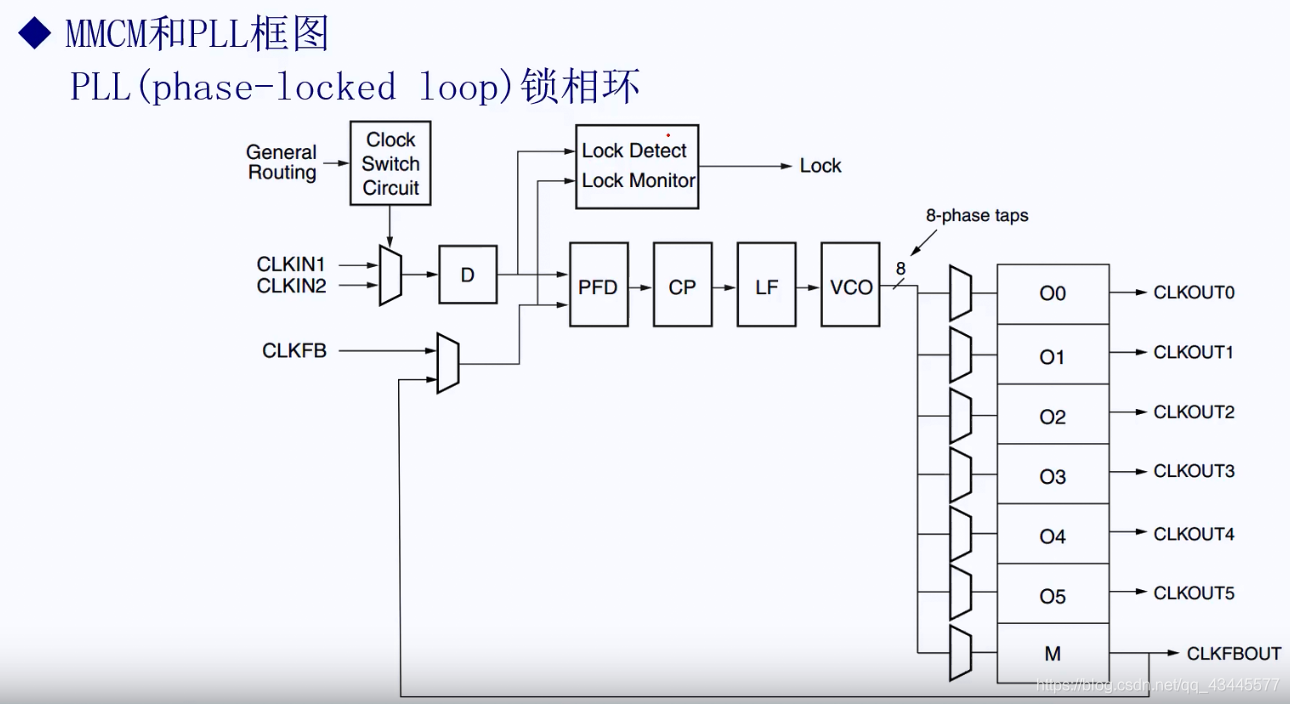

7系列包括有全局时钟和区域时钟,一个CMT包括一个MMCM和一个PLL。CMT提供时钟合成,时钟偏斜校正、过滤抖动功能。因此将本地的时钟输入其中后输出会得到质量的提升。7020包括4个CMT。

-

- MMCM相比PLL做了功能升级,MMCM可以做分数被的频率综合,反相时钟输出,动态频率调整等高级功能。