花了好几个小时,上一节的问题解决了,但具体原因任然不详!

改动点很小,就是把进入lowlevel_init,和退出lowlevel_init用的寄存器r11改为了r10(测试改为r9也可以),不知道是编译器的问题,还是什么问题。暂时先保留,继续把移植进行下去。

一、上一节中lowlevel_init中有clock的初始化代码,但没加进去。首先我们加进去。

/* Pending Interrupt Clear */

str r5, [r0, #0xf00] @ INTADDRESS

str r5, [r1, #0xf00] @ INTADDRESS

str r5, [r2, #0xf00] @ INTADDRESS

str r5, [r4, #0xf00] @ INTADDRESS to_run_away add

bl led1_on @ to_run_away add

bl system_clock_init @ to_run_away add

/* for UART */

bl uart_asm_init

bl internal_ram_init

加到uart的初始化前面

测试后,发现打印出来的字符是乱码,看来时钟不正确。

修改时钟,后发现可以打印了。

# ldr r1, =0x14131330 @ 1:1:4:4, 1:4:5

ldr r1, =0x14131440 @ 1:1:4:4, 1:4:5

str r1, [r0, #0x300]

# ldr r1, =0x11110112 @ UART[3210]: MMC[3210]

# str r1, [r0, #0x310]

/* Set Lock Time */

# ldr r1, =0x2cf @ Locktime : 30us

ldr r1, =0xfff @ Locktime : 30us

str r1, [r0, #0x000] @ S5PC110_APLL_LOCK

# ldr r1, =0xe10 @ Locktime : 0xe10 = 3600

ldr r1, =0xfff @ Locktime : 0xe10 = 3600

str r1, [r0, #0x008] @ S5PC110_MPLL_LOCK

str r1, [r0, #0x010] @ S5PC110_EPLL_LOCK

str r1, [r0, #0x020] @ S5PC110_VPLL_LOCK

/* S5PC110_APLL_CON */

# ldr r1, =0x80C80601 @ 800MHz

ldr r1, =0x807d0301 @ 1000MHz

str r1, [r0, #0x100]

/* S5PC110_MPLL_CON */

ldr r1, =0x829B0C01 @ 667MHz

str r1, [r0, #0x108]

/* S5PC110_EPLL_CON */

# ldr r1, =0x80600602 @ 96MHz VSEL 0 P 6 M 96 S 2

ldr r1, =0x80300302 @ 96MHz VSEL 0 P 6 M 96 S 2

str r1, [r0, #0x110]

二、添加ddr的初始化

直接拷贝三星的dome板的代码,要说明的是我们为了使用方便,两块DDR的地址链接在了一块,即0x30000000~0x4fffffff

#define ELFIN_GPIO_BASE 0xE0200000

#define MP1_0DRV_SR_OFFSET 0x3CC

#define MP1_1DRV_SR_OFFSET 0x3EC

#define MP1_2DRV_SR_OFFSET 0x40C

#define MP1_3DRV_SR_OFFSET 0x42C

#define MP1_4DRV_SR_OFFSET 0x44C

#define MP1_5DRV_SR_OFFSET 0x46C

#define MP1_6DRV_SR_OFFSET 0x48C

#define MP1_7DRV_SR_OFFSET 0x4AC

#define MP1_8DRV_SR_OFFSET 0x4CC

#define MP2_0DRV_SR_OFFSET 0x4EC

#define MP2_1DRV_SR_OFFSET 0x50C

#define MP2_2DRV_SR_OFFSET 0x52C

#define MP2_3DRV_SR_OFFSET 0x54C

#define MP2_4DRV_SR_OFFSET 0x56C

#define MP2_5DRV_SR_OFFSET 0x58C

#define MP2_6DRV_SR_OFFSET 0x5AC

#define MP2_7DRV_SR_OFFSET 0x5CC

#define MP2_8DRV_SR_OFFSET 0x5EC

/*

* SDRAM Controller

*/

#define APB_DMC_0_BASE 0xF0000000

#define APB_DMC_1_BASE 0xF1400000

#define ASYNC_MSYS_DMC0_BASE 0xF1E00000

#define DMC_CONCONTROL 0x00

#define DMC_MEMCONTROL 0x04

#define DMC_MEMCONFIG0 0x08

#define DMC_MEMCONFIG1 0x0C

#define DMC_DIRECTCMD 0x10

#define DMC_PRECHCONFIG 0x14

#define DMC_PHYCONTROL0 0x18

#define DMC_PHYCONTROL1 0x1C

#define DMC_RESERVED 0x20

#define DMC_PWRDNCONFIG 0x28

#define DMC_TIMINGAREF 0x30

#define DMC_TIMINGROW 0x34

#define DMC_TIMINGDATA 0x38

#define DMC_TIMINGPOWER 0x3C

#define DMC_PHYSTATUS 0x40

#define DMC_CHIP0STATUS 0x48

#define DMC_CHIP1STATUS 0x4C

#define DMC_AREFSTATUS 0x50

#define DMC_MRSTATUS 0x54

#define DMC_PHYTEST0 0x58

#define DMC_PHYTEST1 0x5C

#define DMC_QOSCONTROL0 0x60

#define DMC_QOSCONFIG0 0x64

#define DMC_QOSCONTROL1 0x68

#define DMC_QOSCONFIG1 0x6C

#define DMC_QOSCONTROL2 0x70

#define DMC_QOSCONFIG2 0x74

#define DMC_QOSCONTROL3 0x78

#define DMC_QOSCONFIG3 0x7C

#define DMC_QOSCONTROL4 0x80

#define DMC_QOSCONFIG4 0x84

#define DMC_QOSCONTROL5 0x88

#define DMC_QOSCONFIG5 0x8C

#define DMC_QOSCONTROL6 0x90

#define DMC_QOSCONFIG6 0x94

#define DMC_QOSCONTROL7 0x98

#define DMC_QOSCONFIG7 0x9C

#define DMC_QOSCONTROL8 0xA0

#define DMC_QOSCONFIG8 0xA4

#define DMC_QOSCONTROL9 0xA8

#define DMC_QOSCONFIG9 0xAC

#define DMC_QOSCONTROL10 0xB0

#define DMC_QOSCONFIG10 0xB4

#define DMC_QOSCONTROL11 0xB8

#define DMC_QOSCONFIG11 0xBC

#define DMC_QOSCONTROL12 0xC0

#define DMC_QOSCONFIG12 0xC4

#define DMC_QOSCONTROL13 0xC8

#define DMC_QOSCONFIG13 0xCC

#define DMC_QOSCONTROL14 0xD0

#define DMC_QOSCONFIG14 0xD4

#define DMC_QOSCONTROL15 0xD8

#define DMC_QOSCONFIG15 0xDC

#define DMC0_MEMCONTROL 0x00212400 // MemControl BL=4, 1Chip, DDR2 Type, dynamic self refresh, force precharge, dynamic power down off

/* 下面的0x30F01313的 最高位的3代表第一块DMC0的地址是从0x30000000开始的 */

#define DMC0_MEMCONFIG_0 0x30F01313 // MemConfig0 256MB config, 8 banks,Mapping Method[12:15]0:linear, 1:linterleaved, 2:Mixed

#define DMC0_MEMCONFIG_1 0x40F01313 // MemConfig1

#define DMC0_TIMINGA_REF 0x00000618 // TimingAref 7.8us*133MHz=1038(0x40E), 100MHz=780(0x30C), 20MHz=156(0x9C), 10MHz=78(0x4E)

#define DMC0_TIMING_ROW 0x28233287 // TimingRow for @200MHz

#define DMC0_TIMING_DATA 0x23240304 // TimingData CL=3

#define DMC0_TIMING_PWR 0x09C80232 // TimingPower

#define DMC1_MEMCONTROL 0x00202400 // MemControl BL=4, 2 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

#define DMC1_MEMCONFIG_0 0x40F01313 // MemConfig0 512MB config, 8 banks,Mapping Method[12:15]0:linear, 1:linterleaved, 2:Mixed

#define DMC1_MEMCONFIG_1 0x00F01313 // MemConfig1

#define DMC1_TIMINGA_REF 0x00000618 // TimingAref 7.8us*133MHz=1038(0x40E), 100MHz=780(0x30C), 20MHz=156(0x9C), 10MHz=78(0x4E)

#define DMC1_TIMING_ROW 0x28233289 // TimingRow for @200MHz

#define DMC1_TIMING_DATA 0x23240304 // TimingData CL=3

#define DMC1_TIMING_PWR 0x08280232 // TimingPower

.globl mem_ctrl_asm_init

mem_ctrl_asm_init:

/* DMC0 Drive Strength (Setting 2X) */

ldr r0, =ELFIN_GPIO_BASE

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_0DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_1DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_2DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_3DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_4DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_5DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_6DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_7DRV_SR_OFFSET]

ldr r1, =0x00002AAA

str r1, [r0, #MP1_8DRV_SR_OFFSET]

/* DMC1 Drive Strength (Setting 2X) */

ldr r0, =ELFIN_GPIO_BASE

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_0DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_1DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_2DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_3DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_4DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_5DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_6DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP2_7DRV_SR_OFFSET]

ldr r1, =0x00002AAA

str r1, [r0, #MP2_8DRV_SR_OFFSET]

/* DMC0 initialization at single Type*/

ldr r0, =APB_DMC_0_BASE

ldr r1, =0x00101000 @PhyControl0 DLL parameter setting, manual 0x00101000

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x00000086 @PhyControl1 DLL parameter setting, LPDDR/LPDDR2 Case

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0x00101002 @PhyControl0 DLL on

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x00101003 @PhyControl0 DLL start

str r1, [r0, #DMC_PHYCONTROL0]

find_lock_val:

ldr r1, [r0, #DMC_PHYSTATUS] @Load Phystatus register value

and r2, r1, #0x7

cmp r2, #0x7 @Loop until DLL is locked

bne find_lock_val

and r1, #0x3fc0

mov r2, r1, LSL #18

orr r2, r2, #0x100000

orr r2 ,r2, #0x1000

orr r1, r2, #0x3 @Force Value locking

str r1, [r0, #DMC_PHYCONTROL0]

#if 0 /* Memory margin test 10.01.05 */

orr r1, r2, #0x1 @DLL off

str r1, [r0, #DMC_PHYCONTROL0]

#endif

/* setting DDR2 */

ldr r1, =0x0FFF2010 @ConControl auto refresh off

str r1, [r0, #DMC_CONCONTROL]

ldr r1, =DMC0_MEMCONTROL @MemControl BL=4, 1 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL]

ldr r1, =DMC0_MEMCONFIG_0 @MemConfig0 256MB config, 8 banks,Mapping Method[12:15]0:linear, 1:linterleaved, 2:Mixed

str r1, [r0, #DMC_MEMCONFIG0]

ldr r1, =DMC0_MEMCONFIG_1 @MemConfig1

str r1, [r0, #DMC_MEMCONFIG1]

ldr r1, =0xFF000000 @PrechConfig

str r1, [r0, #DMC_PRECHCONFIG]

ldr r1, =DMC0_TIMINGA_REF @TimingAref 7.8us*133MHz=1038(0x40E), 100MHz=780(0x30C), 20MHz=156(0x9C), 10MHz=78(0x4E)

str r1, [r0, #DMC_TIMINGAREF]

ldr r1, =DMC0_TIMING_ROW @TimingRow for @200MHz

str r1, [r0, #DMC_TIMINGROW]

ldr r1, =DMC0_TIMING_DATA @TimingData CL=3

str r1, [r0, #DMC_TIMINGDATA]

ldr r1, =DMC0_TIMING_PWR @TimingPower

str r1, [r0, #DMC_TIMINGPOWER]

ldr r1, =0x07000000 @DirectCmd chip0 Deselect

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00020000 @DirectCmd chip0 EMRS2

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00030000 @DirectCmd chip0 EMRS3

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000542 @DirectCmd chip0 MRS (MEM DLL reset) CL=4, BL=4

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000442 @DirectCmd chip0 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010780 @DirectCmd chip0 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x07100000 @DirectCmd chip1 Deselect

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00120000 @DirectCmd chip1 EMRS2

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00130000 @DirectCmd chip1 EMRS3

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100542 @DirectCmd chip1 MRS (MEM DLL reset) CL=4, BL=4

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100442 @DirectCmd chip1 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110780 @DirectCmd chip1 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x0FF02030 @ConControl auto refresh on

str r1, [r0, #DMC_CONCONTROL]

ldr r1, =0xFFFF00FF @PwrdnConfig

str r1, [r0, #DMC_PWRDNCONFIG]

ldr r1, =0x00202400 @MemControl BL=4, 2 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL]

/* DMC1 initialization */

ldr r0, =APB_DMC_1_BASE

ldr r1, =0x00101000 @Phycontrol0 DLL parameter setting

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x00000086 @Phycontrol1 DLL parameter setting

str r1, [r0, #DMC_PHYCONTROL1]

ldr r1, =0x00101002 @PhyControl0 DLL on

str r1, [r0, #DMC_PHYCONTROL0]

ldr r1, =0x00101003 @PhyControl0 DLL start

str r1, [r0, #DMC_PHYCONTROL0]

find_lock_val1:

ldr r1, [r0, #DMC_PHYSTATUS] @Load Phystatus register value

and r2, r1, #0x7

cmp r2, #0x7 @Loop until DLL is locked

bne find_lock_val1

and r1, #0x3fc0

mov r2, r1, LSL #18

orr r2, r2, #0x100000

orr r2, r2, #0x1000

orr r1, r2, #0x3 @Force Value locking

str r1, [r0, #DMC_PHYCONTROL0]

#if 0 /* Memory margin test 10.01.05 */

orr r1, r2, #0x1 @DLL off

str r1, [r0, #DMC_PHYCONTROL0]

#endif

/* settinf fot DDR2 */

ldr r0, =APB_DMC_1_BASE

ldr r1, =0x0FFF2010 @auto refresh off

str r1, [r0, #DMC_CONCONTROL]

ldr r1, =DMC1_MEMCONTROL @MemControl BL=4, 2 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL]

ldr r1, =DMC1_MEMCONFIG_0 @MemConfig0 512MB config, 8 banks,Mapping Method[12:15]0:linear, 1:linterleaved, 2:Mixed

str r1, [r0, #DMC_MEMCONFIG0]

ldr r1, =DMC1_MEMCONFIG_1 @MemConfig1

str r1, [r0, #DMC_MEMCONFIG1]

ldr r1, =0xFF000000

str r1, [r0, #DMC_PRECHCONFIG]

ldr r1, =DMC1_TIMINGA_REF @TimingAref 7.8us*133MHz=1038(0x40E), 100MHz=780(0x30C), 20MHz=156(0x9C), 10MHz=78(0x4

str r1, [r0, #DMC_TIMINGAREF]

ldr r1, =DMC1_TIMING_ROW @TimingRow for @200MHz

str r1, [r0, #DMC_TIMINGROW]

ldr r1, =DMC1_TIMING_DATA @TimingData CL=3

str r1, [r0, #DMC_TIMINGDATA]

ldr r1, =DMC1_TIMING_PWR @TimingPower

str r1, [r0, #DMC_TIMINGPOWER]

ldr r1, =0x07000000 @DirectCmd chip0 Deselect

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00020000 @DirectCmd chip0 EMRS2

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00030000 @DirectCmd chip0 EMRS3

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000542 @DirectCmd chip0 MRS (MEM DLL reset) CL=4, BL=4

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00000442 @DirectCmd chip0 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010780 @DirectCmd chip0 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x07100000 @DirectCmd chip1 Deselect

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00120000 @DirectCmd chip1 EMRS2

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00130000 @DirectCmd chip1 EMRS3

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110440 @DirectCmd chip1 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100542 @DirectCmd chip1 MRS (MEM DLL reset) CL=4, BL=4

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00100442 @DirectCmd chip1 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110780 @DirectCmd chip1 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD]

ldr r1, =0x0FF02030 @ConControl auto refresh on

str r1, [r0, #DMC_CONCONTROL]

ldr r1, =0xFFFF00FF @PwrdnConfig

str r1, [r0, #DMC_PWRDNCONFIG]

ldr r1, =DMC1_MEMCONTROL @MemControl BL=4, 2 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL]

mov pc, lr

对应目录 board/samsung/smdkv210/的Makefile也增加进去(cpu_init.o)

obj-y := smdkv210.o onenand.o

obj-y += lowlevel_init.o cpu_init.o

顺便在lowlevel_init随便找个位置初始化一下。

为了确定ddr是否初始化成功,我们要添加一些调试代码,通过uart打印

关于上一节的uart没初始就可以打印是因为三星在IROM中就已经初始化了uart2,所以可以直接用。

这里我们主动再初始化一遍。

ldr r0, =0xe2900800 @uart2 base

ldr r1, =3 @8 1 0

str r1, [r0, #0]

ldr r1, =0x305

str r1, [r0, #0x4]

ldr r1, =0x75 @我不想每次都判断前一个字节是否发送完毕,所以开启fifo

str r1, [r0, #0x8]

ldr r1, =0

str r1, [r0, #0x0c]

ldr r1, =34

str r1, [r0, #0x28]

ldr r1, =0xDFDD

str r1, [r0, #0x2c]

顺便写一个打印函数,用来打印ascii码

.globl uart_print_hex

uart_print_hex:

ldr r0, [r0]

ldr r1, =0xe2900820

ldr r2, = 0x30

str r2, [r1] @UTH2='0'

ldr r2, = 0x78

str r2, [r1] @UTH2='x'

ldr r3, = 28

print_hex_loop:

lsr r2, r0, r3

and r2, r2, #0xf

cmp r2, #10

addmi r2, r2, #0x30 @ 0~10

addpl r2, r2, #0x37 @ A~F

str r2, [r1]

sub r3, r3, #4

cmp r3, #0

bpl print_hex_loop

ldr r2, =0xa @回车+换行

str r2, [r1]

ldr r2, =0xd

str r2, [r1]

mov pc, lr

尝试打印,0xe0000000(我们的cpu信息),和我们在ddr写的东西,然后读出来打印

ldr r0,= 0xe0000000

bl uart_print_hex

bl mem_ctrl_asm_init

ldr r0, =0xddddaaaa

ldr r1, =0x31000000

str r0, [r1]

ldr r0, =0x31000000

bl uart_print_hex

发现第一个的0x没有打印出来,ddd后面的daaa也没打印出来。

找了三四个小时,终于找到答案了。如下:

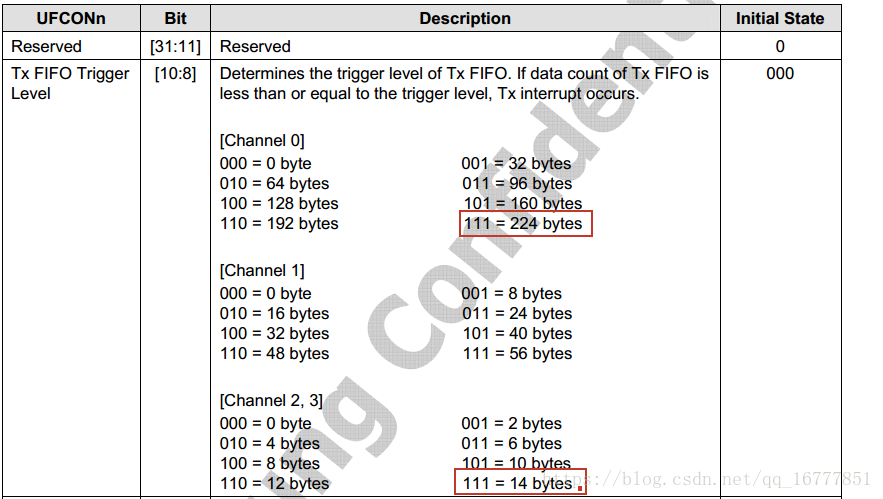

串口2的fifo最大只能存14个字节。改用串口0的,可以存224个字节。

OK,以及另外两个32位地址的值都打印出来了,同时也说明ddr初始化成功了。接下来就调试基本和硬件无关的代码了。

顺便把配置里面的DDR错误信息也改掉

/* goni板子有三块,我只有两块ddr,修改 */

/* Goni has 3 banks of DRAM, but swap the bank */

#define CONFIG_NR_DRAM_BANKS 3

#define PHYS_SDRAM_1 CONFIG_SYS_SDRAM_BASE /* OneDRAM Bank #0 */

#define PHYS_SDRAM_1_SIZE (80 << 20) /* 80 MB in Bank #0 */

#define PHYS_SDRAM_2 0x40000000 /* mDDR DMC1 Bank #1 */

#define PHYS_SDRAM_2_SIZE (256 << 20) /* 256 MB in Bank #1 */

#define PHYS_SDRAM_3 0x50000000 /* mDDR DMC2 Bank #2 */

#define PHYS_SDRAM_3_SIZE (128 << 20) /* 128 MB in Bank #2 */

/* 修改后的 */

#define CONFIG_NR_DRAM_BANKS 2

#define PHYS_SDRAM_1 CONFIG_SYS_SDRAM_BASE /* ddr2 Bank #0 */

#define PHYS_SDRAM_1_SIZE (256 << 20) /* 80 MB in Bank #0 */

#define PHYS_SDRAM_2 0x40000000 /* mDDR DMC1 Bank #1 */

#define PHYS_SDRAM_2_SIZE (256 << 20) /* 256 MB in Bank #1 */

编译后说有错误,继续修改。

board/samsung/smdkv210/smdkv210.c

/* 错误的 */

int dram_init(void)

{

gd->ram_size = PHYS_SDRAM_1_SIZE + PHYS_SDRAM_2_SIZE +

PHYS_SDRAM_3_SIZE;

return 0;

}

void dram_init_banksize(void)

{

gd->bd->bi_dram[0].start = PHYS_SDRAM_1;

gd->bd->bi_dram[0].size = PHYS_SDRAM_1_SIZE;

gd->bd->bi_dram[1].start = PHYS_SDRAM_2;

gd->bd->bi_dram[1].size = PHYS_SDRAM_2_SIZE;

gd->bd->bi_dram[2].start = PHYS_SDRAM_3;

gd->bd->bi_dram[2].size = PHYS_SDRAM_3_SIZE;

}

/* 修改后的 */

int dram_init(void)

{

gd->ram_size = PHYS_SDRAM_1_SIZE + PHYS_SDRAM_2_SIZE E;

return 0;

}

void dram_init_banksize(void)

{

gd->bd->bi_dram[0].start = PHYS_SDRAM_1;

gd->bd->bi_dram[0].size = PHYS_SDRAM_1_SIZE;

gd->bd->bi_dram[1].start = PHYS_SDRAM_2;

gd->bd->bi_dram[1].size = PHYS_SDRAM_2_SIZE;

}