《Low Power Methodology Manual For System-on-Chip Design 》读书笔记

4 电源门控概述

4.1 动态和泄漏功耗曲线

电源门控最基本的思想是为电路提供两种电源模式,分别为低功耗模式和活动模式;其目的是在合适的时间通过恰当的方式在两种模式间切换,带来最大程度上的功耗节省,同时最大限度的降低对系统中其他模块性能方面的影响。

在第2章中提到的几种低功耗技术不会影响到设计的功能,也不会改变RTL;电源门控技术则会对设计有较大的影响,因为他会影响到模块间通信的接口,并且增加了明显的时序延迟,以实现带电源门控模块安全的进入/退出低功耗模式。

对逻辑块进行掉电的操作可以由软件控制,也可以由定时器或系统级电源管理控制器在硬件中实现。在电源门控中我们会面临着很多类似这样的权衡取舍,除了上述的提到控制的实现外,还包括但不限于以下方面:

- l电源门控设计的投入和泄漏功耗上的收益

- 进入和退出低功耗模式所需的时间消耗

- 在低功耗模式期间节省的功耗和从低功耗模式退出来时消耗的功耗比例

- 带电源门控模块的活动曲线(睡眠模式与活动模式的时间比例和切换频率)

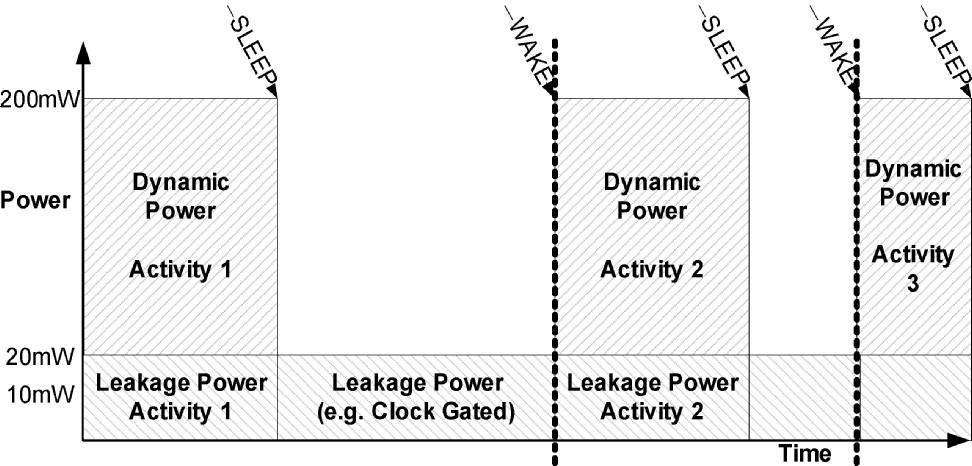

图 1显示了使用时钟门控降低子系统功耗时该子系统的功耗变化曲线。从图 1中可以看到,在子模块休眠期间,由于时钟门控的作用,子模块基本没有动态功耗,这时功耗主要有泄漏功耗产生。

图 1使用时钟门控的功耗变化曲线

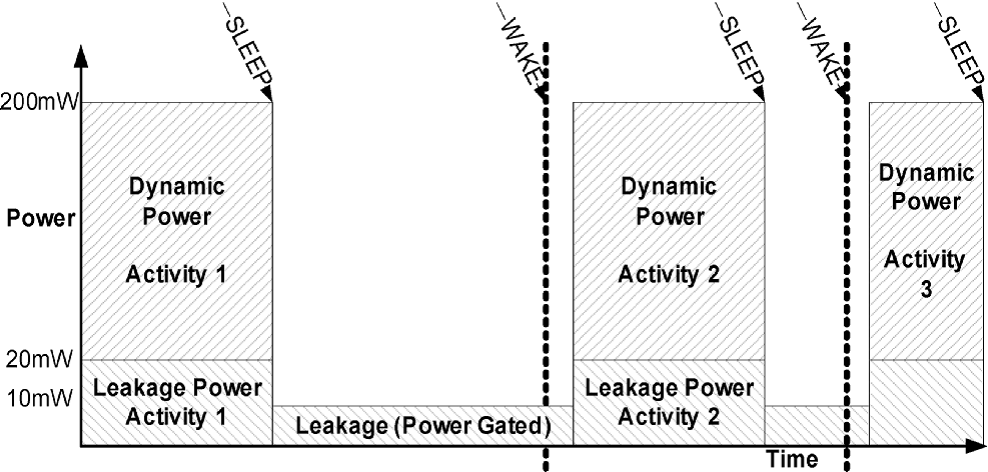

图 2显示了使用时钟门控和电源门控子系统中,该子系统的功耗变化曲线。从图 1和图 2的对比可以看出使用电源门控可以在子系统休眠期间节省一部分漏电功耗;另外,从图 2 还可以看出唤醒模块所需的时间可能很长,在系统级设计时不应忽略这部分时间:

图 2使用电源门控的功耗变化曲线

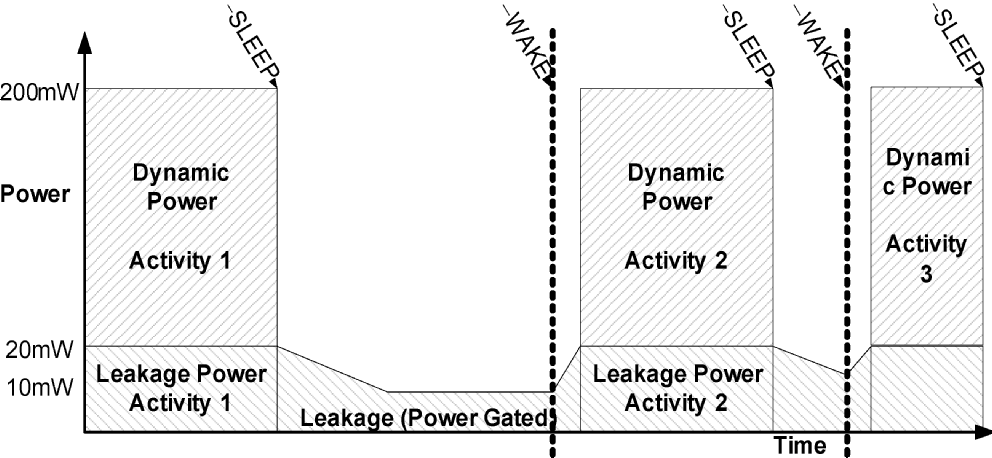

图 3显示了子系统中使用电源门控时,该子系统的实际功耗变化曲线。因为电源门控的开和关两种状态间的转换不是理想情况下的瞬间完成的,而是需要一个的转换时间(上电->下电或者下电->上电)。所以电源门控实际节省的泄漏功耗可能比预计的要少一些。

图 3使用电源门控实际的功耗变化曲线

4.2 电源门控对各类子系统的影响:

带有高速缓存的CPU子系统通常可以长时间处于休眠模式,很适合使用电源门控技术。当CPU不活动时,对整个CPU进行掉电可以节省大量的泄漏功耗,但CPU的唤醒一般由中断触发,所以在系统设计时应考虑到中断的处理和CPU唤醒时所需的时间间隙;此外,如果每次CPU下电,cache里的内容也丢失的话,CPU在下次上电的时候可能需要先从总线上读取相关信息将cache填满,这个过程可能需要花费较长的时间和消耗更多的功耗,所以,CPU净节省的功耗应该是休眠期间节省的功耗减去唤醒期间所消耗的能量。

相比CPU而言外设系统有更加规律的活动时间,它可以由软件驱动或系统中的电源管理模块来实现上/下电操作,这样的情况下,软件需要在外设上/下电的时候对一些信息进行存储/重载,会给软件驱动带来很大的负担。比这个更好的方法是外设在睡眠模式下,在其内部存储关键状态信息,但这需要一些额外的控制电路。

对于一个更复杂的多处理器CPU集群而言,其中一个或多个处理器在完成任务并且处于空闲状态时可以完全关闭电源等待分配另一个任务,由于CPU之前的任务已完成,因此,可以不用关注在掉电期间本地缓存的内容是否丢失的问题,CPU被唤醒后可直接执行重新分配的任务,对于这样的系统可能需要相应的自适应算法,这些算法可以根据负载情况动态的调整电源门控的开关情况,从而控制活动的CPU数。

4.3 电源门控设计原理

关断模块的电源有两种方式,最基本的方式是片外控制,假设某个子模块在片外有一个独立的电源供电,那么当该模块休眠时,可以直接在外部将该模块的电源关掉,使模块中的泄漏功耗减少到基本为零。但是,这种方法需要很长的时间来完成上/下电过程,并且需要消耗很多的能量来恢复模块上电。另一种方法是内部电源门控,内部开关用于控制所选块的电源,在短时间内就可以关闭模块的电源。

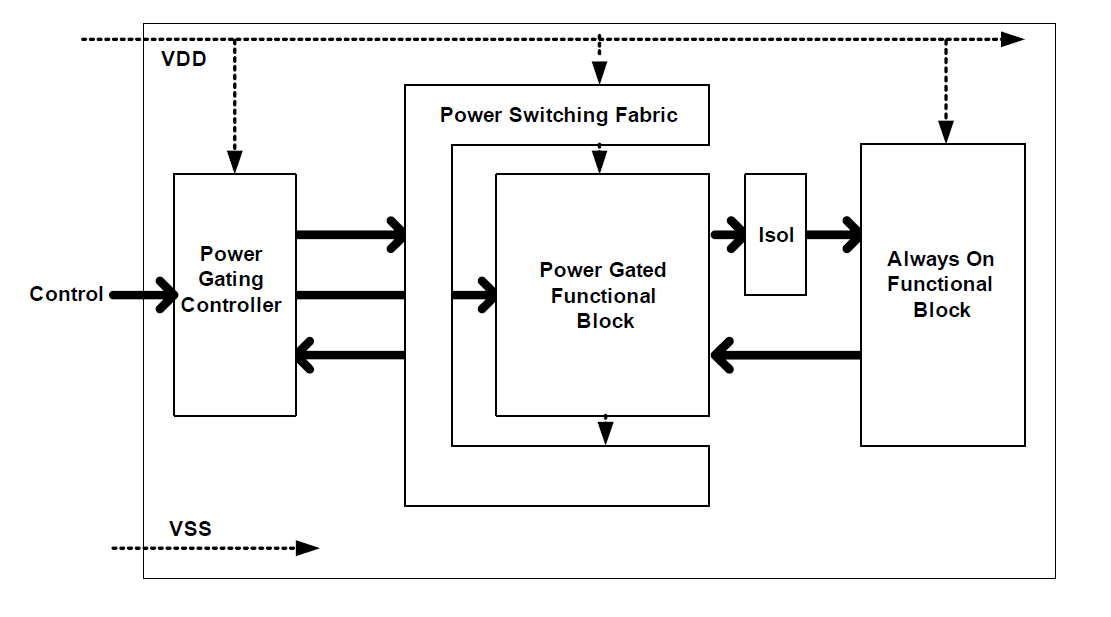

图 4所示为使用内部电源门控的SoC的简化图。与始终上电的模块不同,带电源门控的模块通过电源开关网络对VDD或VSS进行控制,图 4中控制的是VDD,整个芯片使用的是同一个VSS,电源开关是由很多个CMOS开关组成的阵列,电源开关由电源门控控制器控制。

图 4使用内部电源门控的SoC简图

电源门控带来的挑战是当一个子系统需要掉电时,门控整列从全部导通到全部关断的变化过程非常缓慢,这将导致该模块的输出信号很长一段时间内输出为一个中间电平,从而造成与之相连的模块/子系统CMOS管的上下两个管子同时导通,产生大量的直通电流。为了避免上述现象,可在带有电源门控模块的输出信号上增加一个隔离单元,使带有门控的模块,在掉电期间,输出到其他电源域的信号为一个确定的状态。

有的模块可能非常的希望在其掉电期间能够保持一些内部的状态信息,并能够在模块重新上电的时候将这些状态恢复,这种策略可以使模块在上电时节省大量的时间和功耗,实现这种掉电保持信息可以采用带有保持功能的寄存器(retention register),带有保持功能的寄存器有一个主寄存器和一个影子寄存器,影子寄存器比主寄存器要慢,但它的漏电流比主寄存器小,影子寄存器是始终上电的,在模块电源被门控期间,影子寄存器用于保存主寄存器的内容,该寄存器需要我们通过控制端口告诉它,何时将主寄存器的内容保存到影子寄存器中,何时从影子寄存器中恢复保存的信息到主寄存器中,其控制信号来源电源门控控制器。

4.3.1 电源门控的粒度——粗粒度Vs细粒度

实现电源门控的方式有细粒度电源门控和粗粒度电源门控两种方式。

细粒度电源门控是将电源开关放在库里的每个标准单元内,这个开关需要能够提供该单元所需的最大工作电流,所以为了不影响性能,会将开关设计的很大,导致每个cell的面积开销很大(通常是其原来的2~4倍)。细粒度电源门控的优势在于开关上的压降和钳位行为对时序的影响很容易分析,因为开关在cell的内部,这意味着我们仍然可以使用传统的设计流程来实现电源门控的部署。

粗粒度电源门控是用一组开关阵列控制一个模块的电源,如图 4所示,这一组开关的数量很难估计,因为你很难准确的知道电路所需的最大工作电流,只能进行估算,但粗粒度电源门控相对于细粒度电源门控会极大的减少面积上的损失。

近几年,粗粒度电源门控几乎被作为电源门控方案的首选项,因为细粒度门控方案带来的面积上的损失是难以让人接受的,所以后续章节将主要介绍粗粒度电源门控方案。

4.3.2 电源门控带来的挑战

电源门控的实现并不像我们想象的那样只要给对应的模块加一个电源开关,需要的开,不需要的时候关那么简单,它会给设计人员带来如下这些方面的挑战:

- 电源门控阵列的设计(包括开关的数量、大小、布局等)

- 电源门控控制器的设计(包含软件和硬件)

- 隔离单元和带保持寄存器的选择和使用

- 需要尽可能的降低电源门控对时序和面积的影响

- 上/下电过程中时钟和复位的控制

- 电源域间接口的隔离处理

- 电源状态验证

- 电源状态转换的验证

这一章对于电源门控的介绍主要还是在概念上,下一章将会详细的介绍如何实现,也是全书的重电章节。

============正文结束===========

扫描下面的二维码,阅读其他章节。