最近,有好几个师弟说不知道怎么写乘法器,在这里就个人的一点理解做一下讲解,主要分为乘法器的设计原理和代码设计,在这里以4bit和4bit的乘积为例进行编写。

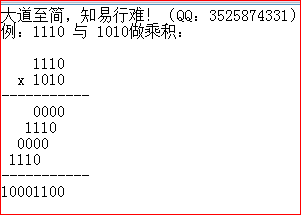

首先,乘法器中最少需要两个因数,一个乘数一个被乘数,而且需要明白的是乘积的位数是两个因数的位数和;其次,需要了解乘法就是多个加法的集合。比如,乘数的最后一位乘以被乘数之后,得出一个4bit的结果;之后乘数的次低位与被乘数的乘积也是一个4bit的结果;如果只考虑4bit与2bit数据的乘积的话,那么将次低位向左移一位与最低位乘积相加即可得出结果,这里会有不少网友说这么算下来是5bit的结果呀,为什么说是两个因数的位数和呢?这是因为要考虑到进位的原因。下面会给出一张图进行说明。

具体的讲解就到此结束,接下来进行代码编写:

module MUL4_4

(

input wire clk,

input wire rst_n,

input wire [3:0] a,

input wire [3:0] b,

output reg [7:0] dout

);

reg [7:0] mul0;

reg [7:0] mul1;

reg [7:0] mul2;

reg [7:0] mul3;

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)begin

mul0 <= 8'b0;

mul1 <= 8'b0;

mul2 <= 8'b0;

mul3 <= 8'b0;

doout <= 8'b0;

end

else begin

mul0 <= a[0]?{4'b0,b}:8'b0;

mul1 <= a[1]?{3'b0,b,1'b0}:8'b0;

mul2 <= a[2]?{2'b0,b,2'b0}:8'b0;

mul3 <= a[3]?{1'b0,b,3'b0}:8'b0;

dout <= mul0 + mul1 + mul2 + mul3;

end

end

endmodule