80x86系统寄存器和系统指令

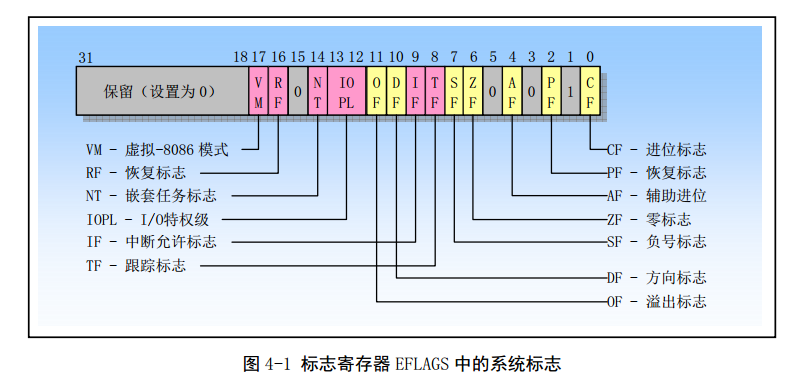

1、标志寄存器(EFLAGS)

标志寄存器EFLAGS的标志位含义如下图:

TF 位8是跟踪标志(Trace flag),当设置该位时可为调试操作启动单步执行方式。复位时则禁止单步执行。在单步执行方式下,处理器会在每个指令执行后产生一个调试异常,这样我们可以观察执行程序在每条指令执行后的状态。

IOPL 位13-12时I/O特权级(I/O Privilege Level)字段。该字段指明当前运行程序或任务的I/O特权级别IOPL。当前任务或程序的CPL必须小于这个IOPL才能访问I/O地址空间。只有当CPL位特权级0时,程序才可以使用POPF或IRET指令修改这个字段,IOPL也是控制对IF标志修改的机制之一

NT 位14是嵌套任务标志(Nested Task)。它控制着被中断任务和调用任务之间的链接关系。在使用CALL指令、中断或异常执行任务调用时,处理器会设置该标志,在通过IRET指令从一个任务返回时,处理器会检查并修改这个NT标志。使用POPF/POPFD指令也可以修改这个标志,但是在应用程序中改变这个标志的状态会产生不可意料的异常

RF 位16时恢复标志(Resume Flag)。该标志用于控制处理器对断点指令的响应。当设置时,这个标志会临时禁止断点指令产生调试异常;当标志复位时,则断点指令将会产生异常。RF的主要功能是允许调试异常后重行执行一条指令。当调试软件使用IRETD指令返回被中断程序之前,需要设置堆栈上EFLAGS内容中的RF标志,以防止指令断点造成另一个异常,处理器会在指令返回之后自动清除该标志,从而再次允许指令断点异常。

VM位17是虚拟-8086方式标志,当设置该标志时,新开启虚拟-8086方式,当复位该标志时,则回到保护模式

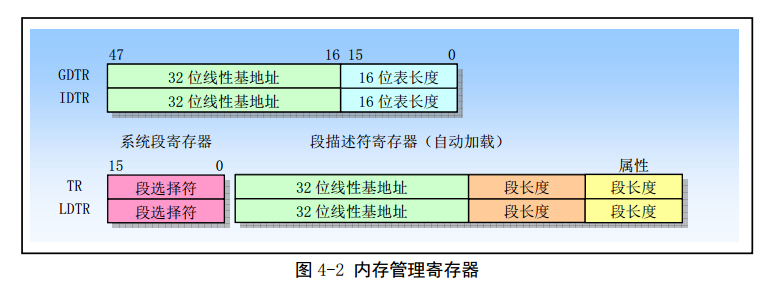

内存管理寄存器

处理器提供了4个内存管理寄存器(GDTR、LDTR、IDTR和TR),用于指定分段内存管理所使用的系统表的基地址,其中包含有分段机制的重要信息。GDTR、IDTR和LDTR用于寻址存放描述符表的段,TR用于寻址一个特殊任务状态段TSS(Task State Segment),TSS段中包含着当前执行任务的重要信息。见下图,处理器为这些寄存器的加载和保存提供了特定的指令。

1、全局描述符表寄存器(GDTR)

GDTR寄存器用于存放全局符号描述表(GDT)的线性基地址(32位)和表长度值(16位)。基地址指定GDT表中的字节0在线性地址空间中的地址,表长度指明GDT表的字节长度值,指令LGDT和SGDT分别用于加载和保存GDTR寄存器的内容。在机器刚上电或处理器复位后,基地址被默认设置为0,而表长度被设置成0xFFFF。在保护模式初始化过程中国必须给GDTR加载一个新值。

2、中断描述符表寄存器IDTR

与GDTR的作用类似,IDTR寄存器用于存放中断描述符表的32位线性基地址和16位表长度值。指令LIDT与SIDT分别用于加载和保存中断描述符表的内容。在机器刚刚上电或处理器复位后,基地址默认设置为0,长度值被设置为0xFFFF

3、局部描述符表寄存器LDTR

LDTR用于存放局部描述符表LDT的32位线性基地址、16位段限长和描述符属性值。指令LLDT和SLDT用于加载和保存LDTR寄存器的段描述符部分,包含LDT表的段必须在GDT表中有一个段描述符项

4、TR任务寄存器

TR寄存器用于存放当前任务TSS段的16位段选择符,32位基地址、和16位段长度和描述符属性值。它引用GDT表中的一个TSS类型放入描述符,指令LTR和STR分别用于加载和保存TR寄存器的段选择符部分。

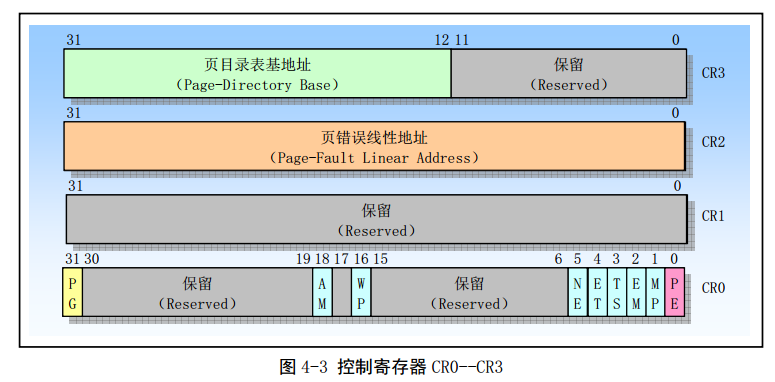

控制寄存器

控制寄存器(CR0、CR1、CR2、CR3)用于控制和确定处理器的操作模式以及当前执行任务的特性,见下图,CR0中含有控制处理器操作模式和状态的系统控制标志;CR1保留不用,CR2含有导致也错误的线性地址;CR3中含有页目录表物理内存基地址,因此该寄存器也被称为页目录基地址寄存器(PDBR)

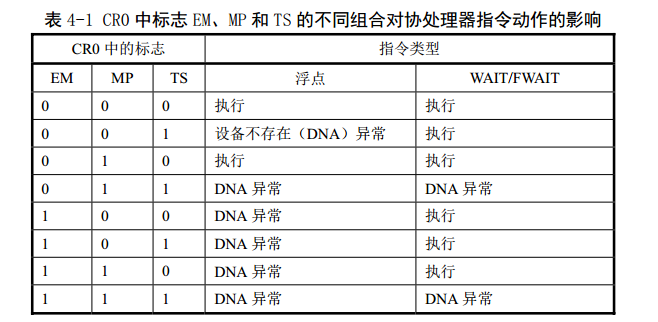

1、CR0中协处理器控制位

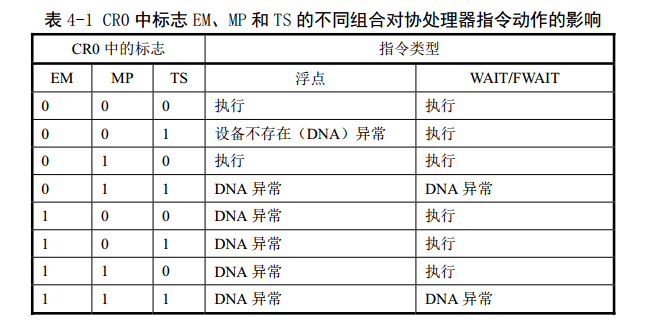

CR0中的4个bit位:扩展类型位ET、任务切换位TS、仿真位EM和数学存在位MP用于控制80x86浮点(数学)协处理器的操作。

ET是CR0的位4是扩展类型标志,当该标志为1时,表示指明系统有80387协处理器存在,并使用32位协处理器协议。当ET=0指明使用80287协处理器。如果仿真位EM=1,则该位将被忽略。在处理器复位操作时,ET会被初始化指明系统中使用的协处理器类型。如果系统中有80387,则被设置为1,否则若有一个80287或没有协处理器,则ET被设置为0

TS是CR0的第3位,是任务已切换(Task switched)标志,该标志用于推迟保存任务切换时的协处理器内容,直到新任务开始实际执行协处理器指令。处理器在每次任务切换时都会设置该标志,并且执行协处理器指令时测试该标志。

如果设置了TS标志并且CR0的EM标志为0,那么在执行任何协处理器指令之前会产生一个设备不存在(DNA)异常。如果设置了TS标志,但没有设置CR0的MP和EM标志,那么执行协处理器指令WAIT/FWAIT之前不会产生设备不存在异常。如果任务从没有使用过协处理器,那么相应协处理器上下文就不用保存了。

EM是CR0第2位,仿真标志,当该位置设置时,表示处理器没有内部或外部协处理器,执行协处理器指令时会引起设备不存在异常;当清除时,表示协同有协处理器,设置这个标志可以迫使所有浮点指令使用软件来模拟。

MP是CR0的位1是监控协处理器标志(Monitor coprocessor或math present)标志,用于控制wait/fwait指令与TS的交互作用。如果MP=1、TS=1,那么WAIT指令将产生一个设备不存在异常。如果MP=0,则TS标志不会影响WAIT的执行

2、CR0中保护控制位

PE CR0的位0是启用保护标志,当设置该位时,即开启了保护模式;当复位时即进入实地址模式。这个标志仅开启段级保护,而并没有启用分页机制。若要启用分页机制,那么PE和PG标志都要置位

PG CR0的位31时分页标志位,当设置该位时即开启了分页机制;当复位时则禁止分页机制,此时所有线性地址等于物理地址。在开启此标志之前必须已经或同时开启PE标志;即若要分页机制,则PE与PG标志都要设置

WP对于Intel 80486或以上的cpu,CR0的16位是写保护标志,当设置该标志时,处理器会禁止超级用户程序(例如特权等级0的程序)向用户级只读页面执行写操作;当该位复位时,则反之。该标识有利于unix类操作系统在创建进程时实现写时复制技术。

NE对于Intel 80486或以上的CPU,CR0的位5是协处理器错误(Numberic Error)标志。当设置该标志时,就启用了X87协处理器错误的内部报告机制;若复位该位,那么就使用PC形式的X87协处理器错误报告机制。当NE为复位状态并且CPU的IGNNE输入引脚有信号时,那么数学协同处理器X87错误将被忽略

启用保护模式PE位和开启分页PG位分别用于控制分段和分页机制

CR2和CR3

CR2和CR3用于分页机制,CR3含有存放页目录表页面的物理地址