实验1:

实验内容:设计4-16译码器

实验步骤:

(1)熟悉译码器结构,预先估计仿真波形;

(2)新建工程,编写verilog代码,并进行编译;

(3)观察RTL视图,设置管脚;

(4)新建vwf文件,进行仿真。

实验结果:

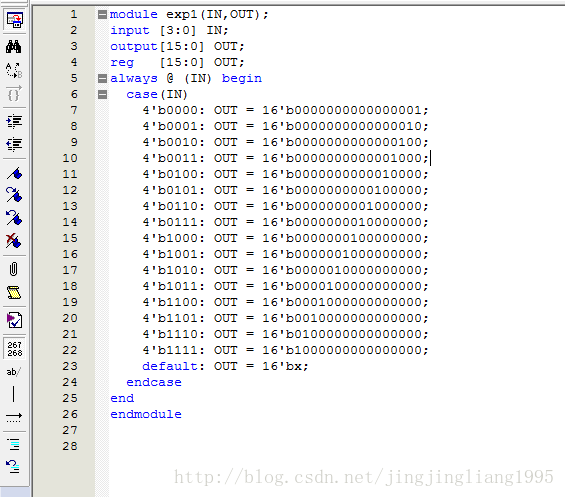

代码截图:

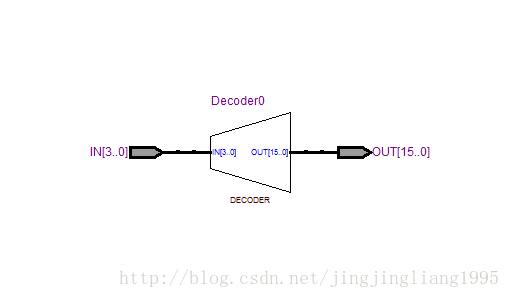

RTL视图:

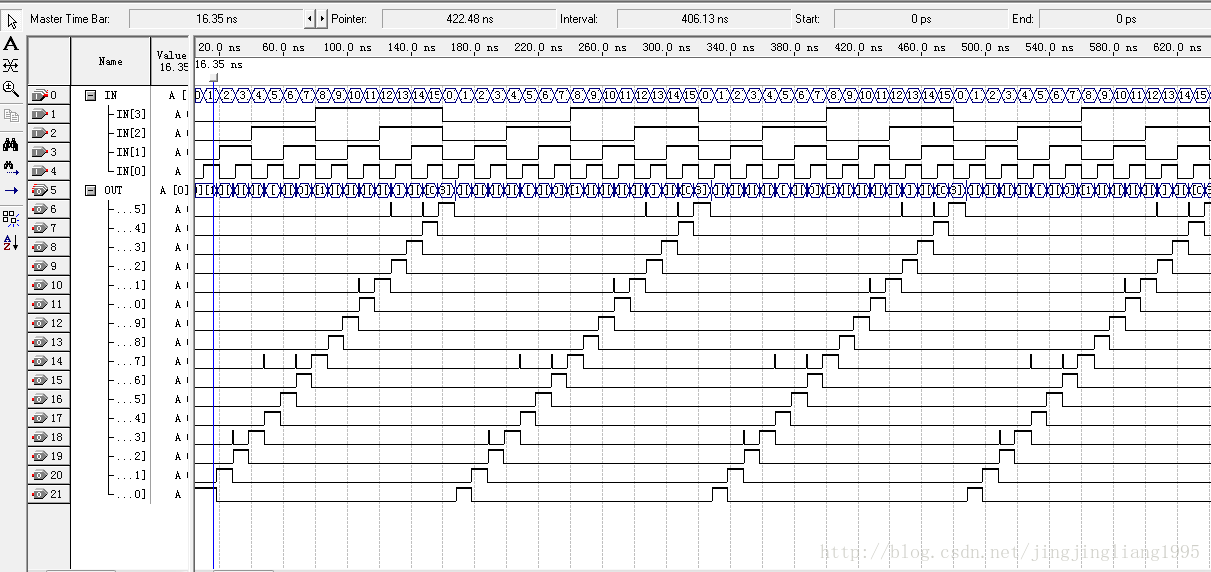

仿真结果:

实验2a:

实验内容:设计M=12计数器

实验步骤:

(1)熟悉计数器结构,预先估计仿真波形;

(2)新建工程,编写verilog代码,并进行编译;

(3)观察RTL视图,设置管脚;

(4)新建vwf文件,进行仿真。

实验结果:

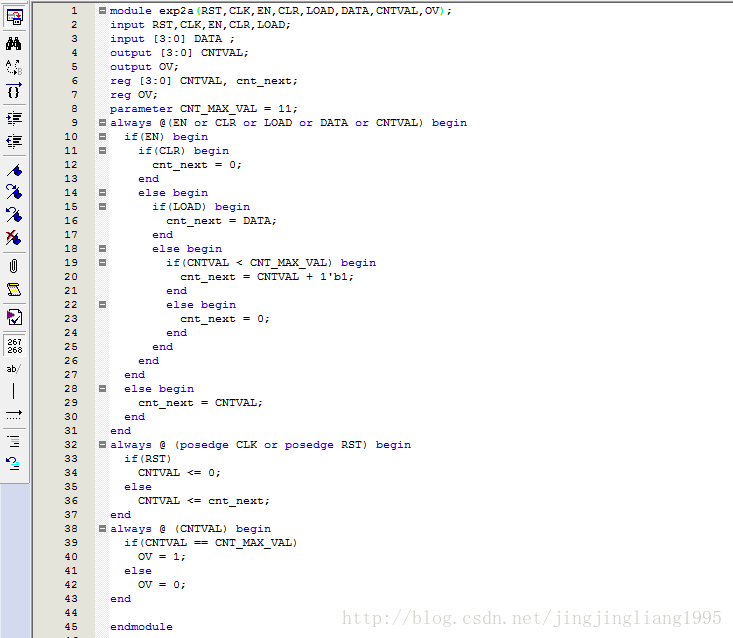

代码截图:

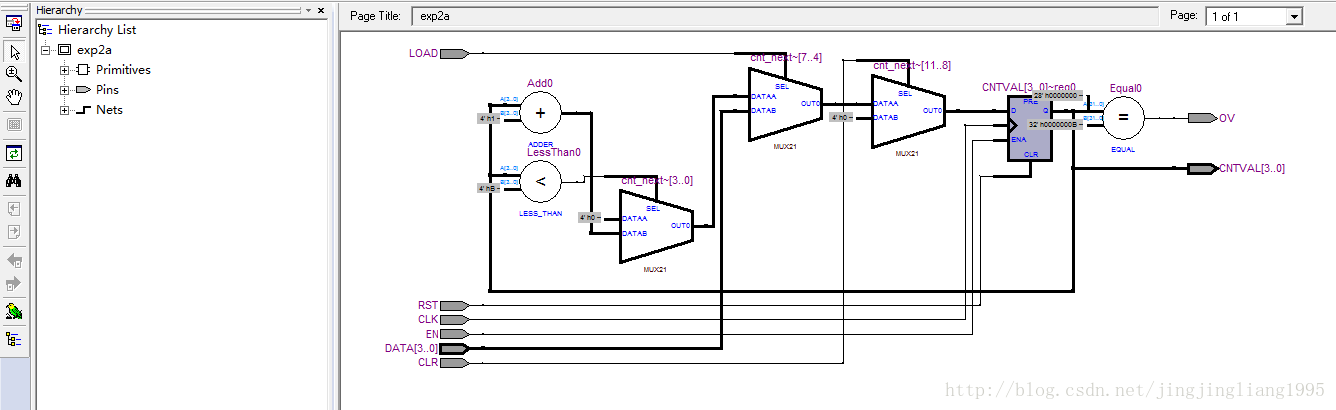

RTL视图:

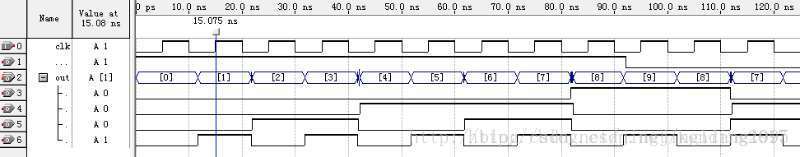

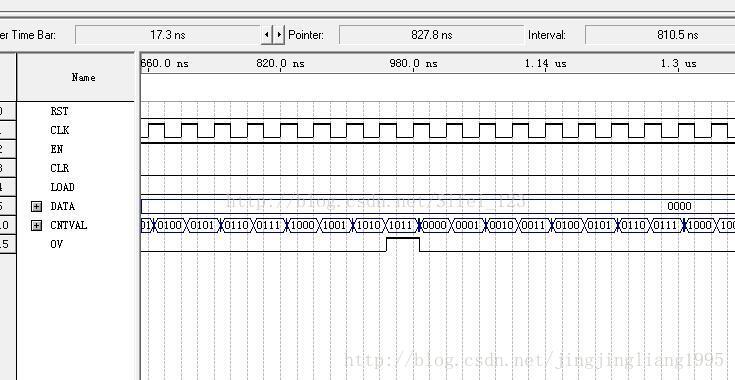

仿真结果:

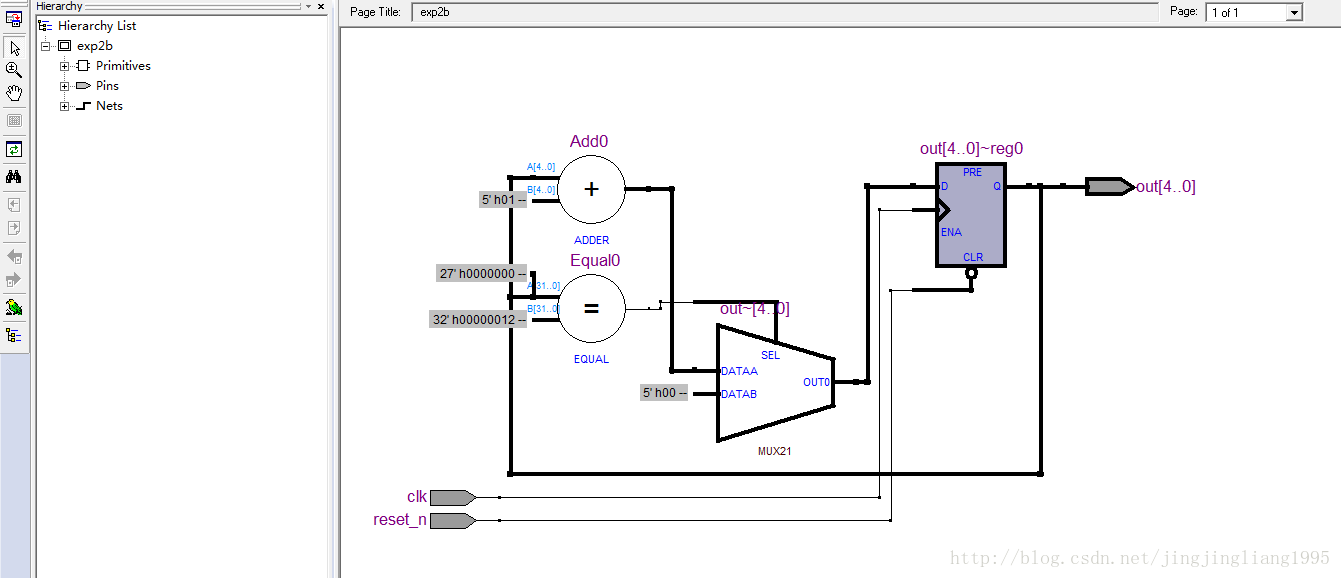

实验2b:

实验内容:设计M=20计数器

实验步骤:

(1)熟悉计数器结构,预先估计仿真波形;

(2)新建工程,编写verilog代码,并进行编译;

(3)观察RTL视图,设置管脚;

(4)新建vwf文件,进行仿真。

实验结果:

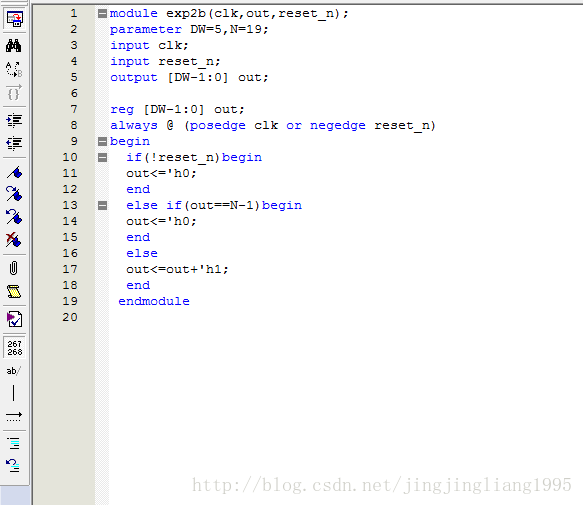

代码截图:

RTL视图:

仿真结果:

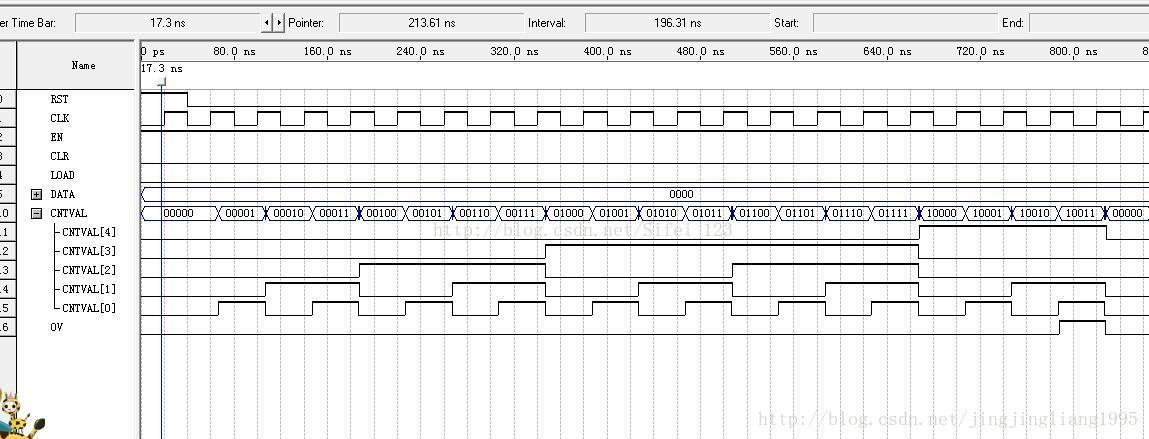

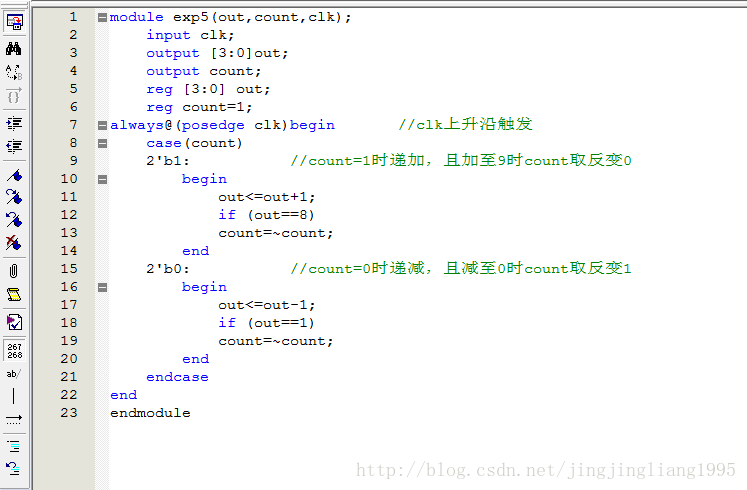

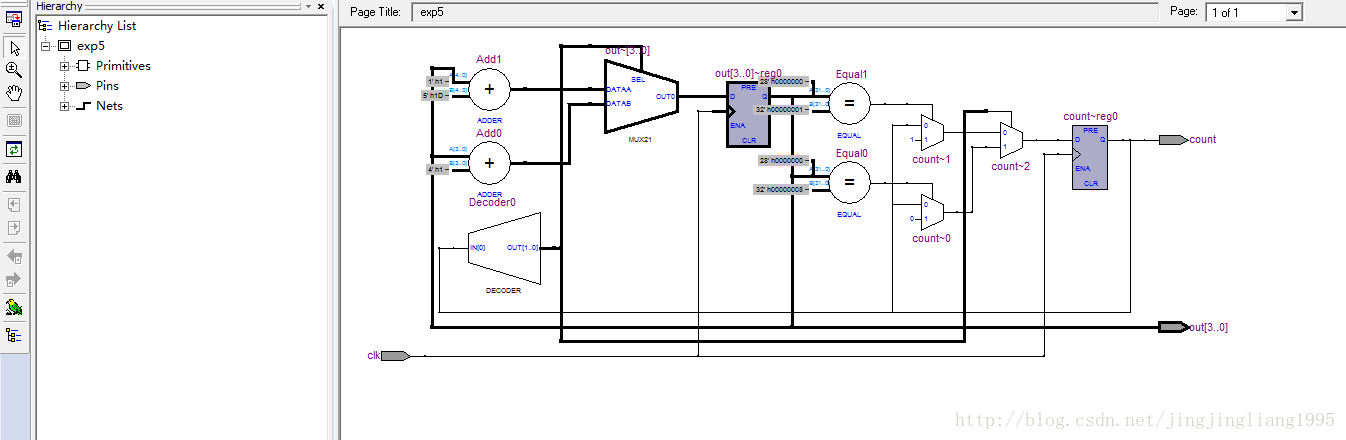

实验3:

实验内容:设计循环计数器

实验步骤:

(1)熟悉计数器结构,预先估计仿真波形;

(2)新建工程,编写verilog代码,并进行编译;

(3)观察RTL视图,设置管脚;

(4)新建vwf文件,进行仿真。

实验结果:

代码截图:

RTL视图:

仿真结果:

EDA第二次作业

猜你喜欢

转载自blog.csdn.net/jingjingliang1995/article/details/78446027

今日推荐

周排行