在mobilenet中,广泛使用片状的卷积

卷积核的代码为

module conv_2d_kernel_(

x0,x1,x2,x3,x4,x5,x6,x7,x8,

y0,y1,y2,y3,y4,y5,y6,y7,y8,

rst

);

input[15:0] x0;

input[15:0] x1;

input[15:0] x2;

input[15:0] x3;

input[15:0] x4;

input[15:0] x5;

input[15:0] x6;

input[15:0] x7;

input[15:0] x8;

input[15:0] y0;

input[15:0] y1;

input[15:0] y2;

input[15:0] y3;

input[15:0] y4;

input[15:0] y5;

input[15:0] y6;

input[15:0] y7;

input[15:0] y8;

output[15:0] rst;

assign rst = x0*y0+x1*y1+x2*y2+x3*y3+x4*y4+x5*y5+x6*y6+x7*y7;

endmodule

testbench可以自动生成模板:首先(open)打开需要仿真的模块 ,Source -> Show Language Templates,在显示的 Language Templates栏目中选择“Create Testbench”,软件自动弹出的"Create Testbench Wizzard”窗口中,在"work"下选择待仿真模块,按照提示走完,即自动生成。增加值,代码如下:

module conv_2d_kernel__tb ;

reg [15:0] x8 ;

wire [15:0] rst ;

reg [15:0] y0 ;

reg [15:0] y1 ;

reg [15:0] y2 ;

reg [15:0] y3 ;

reg [15:0] y4 ;

reg [15:0] y5 ;

reg [15:0] y6 ;

reg [15:0] y7 ;

reg [15:0] x0 ;

reg [15:0] y8 ;

reg [15:0] x1 ;

reg [15:0] x2 ;

reg [15:0] x3 ;

reg [15:0] x4 ;

reg [15:0] x5 ;

reg [15:0] x6 ;

reg [15:0] x7 ;

initial

begin

x0=1;

x1=1;

x2=1;

x3=1;

x4=1;

x5=1;

x6=1;

x7=1;

x7=1;

y0=1;

y1=1;

y2=1;

y3=1;

y4=1;

y5=1;

y6=1;

y7=1;

y8=1;

end

conv_2d_kernel_

DUT (

.x8 (x8 ) ,

.rst (rst ) ,

.y0 (y0 ) ,

.y1 (y1 ) ,

.y2 (y2 ) ,

.y3 (y3 ) ,

.y4 (y4 ) ,

.y5 (y5 ) ,

.y6 (y6 ) ,

.y7 (y7 ) ,

.x0 (x0 ) ,

.y8 (y8 ) ,

.x1 (x1 ) ,

.x2 (x2 ) ,

.x3 (x3 ) ,

.x4 (x4 ) ,

.x5 (x5 ) ,

.x6 (x6 ) ,

.x7 (x7 ) );

endmodule

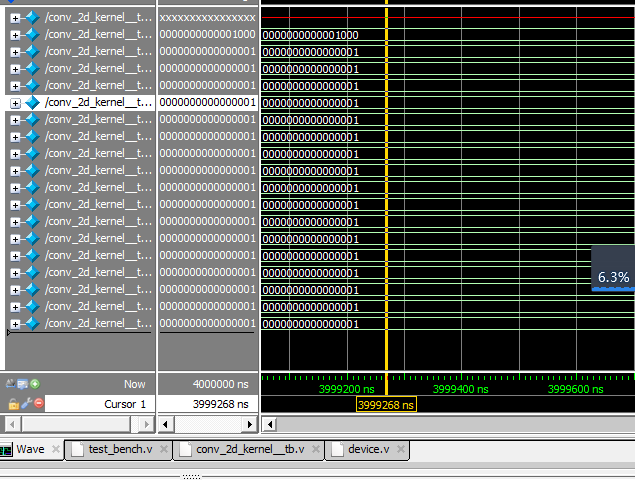

仿真的结果为

右键library中的worker中选择simulate相当于给某个器件上电,run相当于打开了开关。