GIC(通用中断控制器,

Generic Interrupt Controller)是一种用于处理中断的硬件组件,它的主要功能是协调和管理系统中的中断请求,确保它们被正确地传递给相应的处理器核心。

1 Cortex-A核中断

1.1 处理器模式

这里以Cortex-A9为例,先来看一下处理器的几种模式:

| 操作模式 | 描述 |

|---|---|

| User | 是应用程序运行的基本模式。这是一个非特权模式,对系统资源有限制的访问。 |

| System | 提供对系统资源的完全访问权限。只能从下面列出的某个异常模式转入。 |

| Supervisor | 在处理器执行监控SVC时进入,也会在复位或上电时进入。 |

| Abort | 试图访问非法内存位置时进入 |

| Undefined | 试图执行未实现的指令时进入 |

| IRQ | 响应中断请求 |

| FIQ | 响应快速中断请求 |

处理器首次上电或复位时,处于Supervisor模式。该模式是特权模式,允许使用所有处理器指令和操作。从Supervisor模式可以切换到User模式。User模式是唯一的非特权模式,某些类型的处理器操作和指令是被禁止的。在实际应用中,Supervisor模式通常在处理器执行操作系统等代码时使用,而正常的软件代码可能在User模式下运行,从而为系统地关键资源提供一定程度的保护。

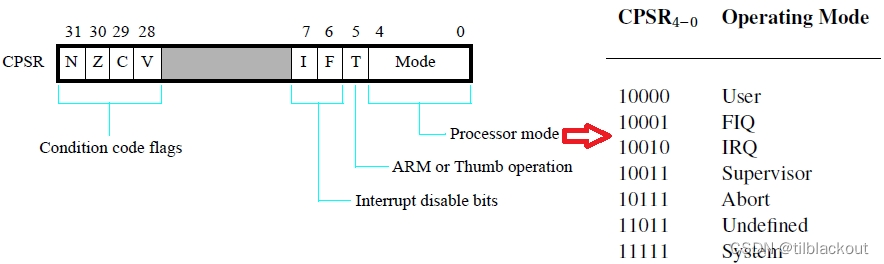

处理器的操作模式由处理器状态寄存器CPSR指示和更改,如下图所示:

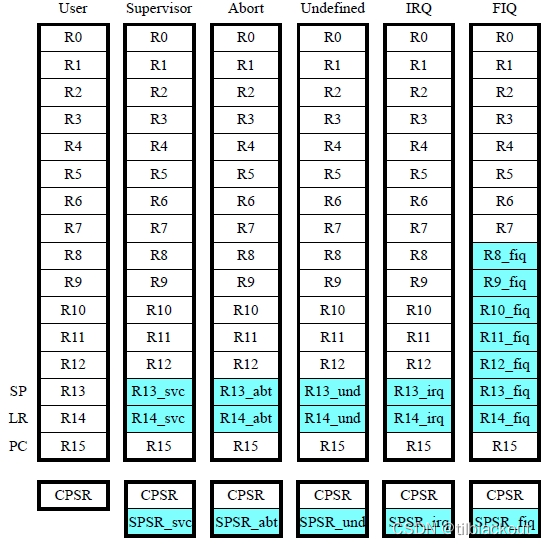

要修改CPSR的内容,处理器必须处于特权模式。如下图所示,为Cortex-A9处理器中的通用寄存器。

-

在

User模式中,有16个寄存器:R0到R15,以及CPSR。 -

图中没有

System模式,但这些寄存器在System模式中也可用 -

除

FIQ模式外的所有模式中,R0到R12,以及R15都是通用的。而对于R13和R14来说,不同的模式都有自己独有的R13和R14。 -

CPSR寄存器对所有模式都是通用的,但从一种模式切换到另一种模式时,CPSR的当前内容会被复制到新模式的保存处理器状态寄存器(SPSR)中

注意,本文不对FIQ模式进行深入讨论,它有独有的R8到R12寄存器。

1.2 IRQ模式

Cortex-A9处理器在接收到来自GIC的IRQ信号时,会进入上面所说的IRQ模式。软件上配置中断的步骤如下:

- 禁用

IRQ中断:将CPSR中的IRQ禁用位置为1。 - 配置GIC:与

GIC连接的每个I/O外设的中断都由唯一的中断ID标识。 - 配置每个I/O外设:以便它们可以向

GIC发送IRQ中断请求。 - 启用

IRQ中断:将CPSR中的IRQ禁用位设置为0。

2 GIC的操作

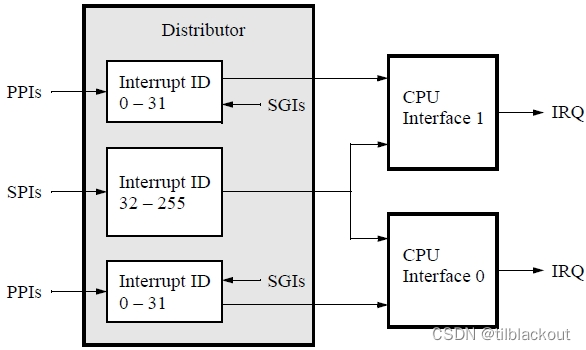

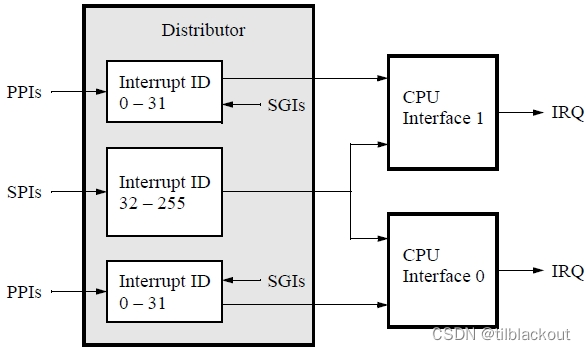

GIC架构分为两个主要部分,称为CPU接口(CPU Interface)和分发器(Distributor)。CPU接口负责将Distributor接收到的IRQ请求发送到Cortex-A处理器(若有双核则可以发给两个)。而Distributor从I/O外设接收IRQ中断信号。

2.1 CPU Interface

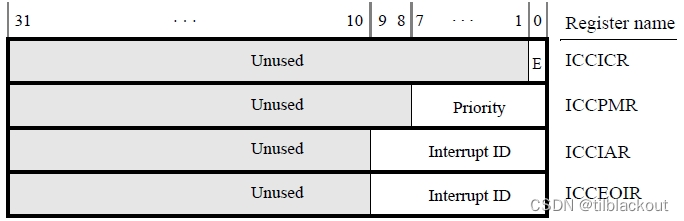

CPU接口用于向Cortex-A核发送中断请求(IRQ)信号。如果有多核的话,每个核都有一个CPU接口。每个CPU接口中的相关寄存器如下所示:

ICCICR(CPU Interface Control Register):用于使能/禁用从CPU接口到相应Cortex-A核的中断转发ICCPMR(Interrupt Priority Mask Register):设置由CPU接口发送到Cortex-A核的中断的优先级阈值,优先级低于这个值的中断将被屏蔽ICCIAR(The Interrupt Acknowledge Register):包含引起中断的I/O外设的中断ID。当处理器从GIC接收到IRQ信号时,程序员可通过在中断处理程序中读取ICCIAR以确定哪个I/O外设引起了中断。ICCEOIR(End of Interrupt Register):在完成IRQ中断处理后,处理器必须清除此中断的标志位。我们只要将对应的中断ID写入这个寄存器即可清除中断标志位。

2.2 Distributor

GIC中的分配器可以处理255个中断源。再来回看一下这个图:

SPIs(共享外设中断,shared peripheral interrupts):中断ID范围为32到255,最多连接到224个I/O外设的IRQ信号,这些中断源是两个CPU接口共享的。PPIs(私有外设中断,private peripherals interrupts):中断ID范围为0到31。SGI(软件生成中断,software generated interrupts):是一种特殊的私有中断,通过写入GIC特定寄存器来生成;0到15的中断ID用于SGI。这里不对SGI做详细讨论。

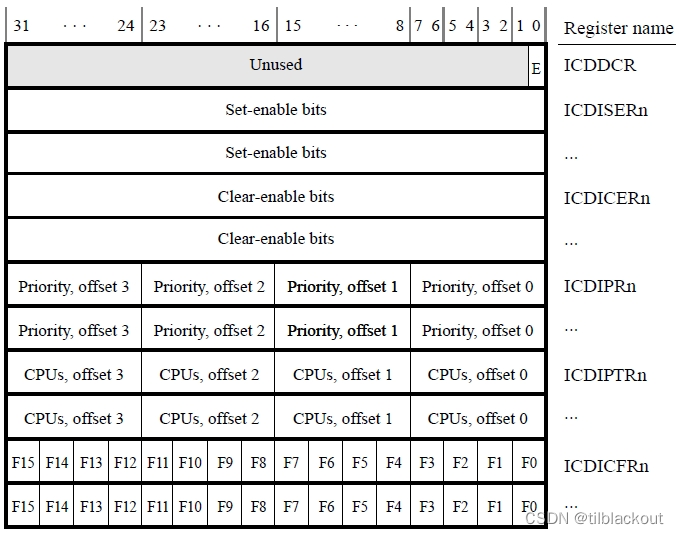

分配器的相关寄存器如下图所示:

-

ICDDCR(分配器控制寄存器,Distributor Control Register):用于使能/禁用分配器 -

ICDISERn(中断集使能寄存器,Interrupt Set Enable Registers):用于使能从分配器到CPU接口的每个中断的转发。由于中断不止32个,所以这里有多个ICDISER寄存器,每个寄存器包括32个中断ID -

ICDISERn(中断清除使能寄存器,Interrupt Clear Enable Registers):用于禁用每个中断,写入1将禁用将相应中断转发到CPU接口 -

ICDIPRn(中断优先级寄存器,Interrupt Priority Registers):设置中断的优先级。每个中断ID的优先级字段占据1字节 -

ICDIPTRn(中断处理器目标寄存器,Interrupt Processor Targets Registers):指定每个中断应转发到哪个CPU接口。每个中断ID占1字节(有的版本最多有8个Cortex-A核),设置为1表示选择该CPU。- 假设系统中有两个内核(1和2),若将图中的

CPUs,offset0设置为11,表示中断ID为0的中断将发送到内核1和内核2中。

- 假设系统中有两个内核(1和2),若将图中的

-

ICDICFRn(中断配置寄存器,Interrupt Configuration Registers):用于指定每个中断在GIC中是应作为电平触发还是边沿触发。- 电平触发:中断信号在保持为高或低电平时触发,电平翻转时,如从1变为0,表示中断结束

- 边沿触发:当中断信号产生一个上升或下降沿时触发

- 每个中断ID有两位用来配置电平或边沿触发,其中LSB没用到,当MSB为1时表示边沿触发,0表示电平触发

- 当I/O外设产生电平触发的

IRQ信号时,如果中断尚未从分配器转发到CPU接口,则可以取消这个信号;然而,一旦在分配器中采样了边沿触发的IRQ信号,就不能取消这个信号。