前面的文章我们介绍了关于FFT的硬件实现。关于FFT的逆运算IFFT,其实就是将实现FFT的过程反过来执行就可以了。

在实现过程中要注意很多问题。

同 FFT一样,效率问题。以2048点为例,根据理论值计算,计算一次2048点的IFFT的时间应为130us。在采用流水线的方式下,实部计算和虚部计算均采用两块RAM实现流水线。

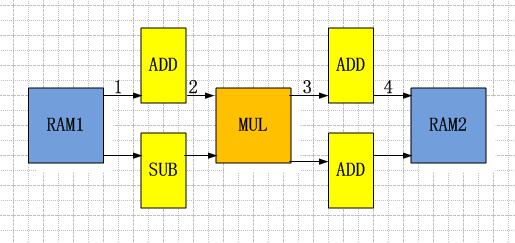

结构如上图。在这种方式下,FPGA的片上RAM会消耗很多。

为了节省RAM,可以采用一块RAM的流水线方式。在实现过程中要注意对RAM操作的reading-during-write,之前的文章介绍过了。这种方式速度会降低一半。

最节省的方式是使用控制器方式,但速度更低。这里不再介绍。

上图所示的IFFT流程,存在大量的组合逻辑,时序远远不够,所以应当在组合逻辑中加入寄存器提高速度。但是,寄存器流水线的级数又影响到了读写两块RAM的切换,从而影响计算效率,所以这里值得商榷。

由于设计中RAM输出端没有使用REG,所以1处应该加入REG,提高速度,否则1处会出现时序违规,1处的组合逻辑延迟很大。

2处和3处也是值得深入考虑的地方,加法器的输出到乘法器的输入,以及乘法器的输出再到加法器的输入,均是大量的组合逻辑,设计中一定要注意,不能仅仅完成功能仿真就可以了,一定要在综合工具下综合一下,看看时序是否满足。实践中,这两处均加入REG。

4处是否再加REG需要看综合后的结果。根据实际分析,4处加REG会降低计算效率,读RAM和写RAM来不及切换,这是根据自己的设计得出的结果。

由于FFT计算过程用到乘法器,所以在IFFT中需要用到除法器。如何减少除法器使用的资源或者将除法器更改为其他逻辑实现,需要深入探讨。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间