使用功率MOSFET常见的一些问题(一)

刚开始用功率MOS管的时候经常会遇到炸管子的事情,过来人都说不炸几个管子就永远不会用MOS管,我想学习学习,这到底是怎么回事,是MOS管的原理就是这样脆弱呢还是我们应用的不对呢,查了一些资料和一些案例,学习学习。

1.MOS管简介

功率 MOSFET 于 20 世纪 70 年代首次推出,并成为世界上应用最广泛的功率晶体管。与双极功率晶体管等老技术相比,它们在线性和开关应用中具有许多优势。这些优势包括极大改进的开关特性、易于并联、没有二次击穿效应以及更宽的安全工作区 (SOA)。MOSFET 属于电压驱动型跨导器件。

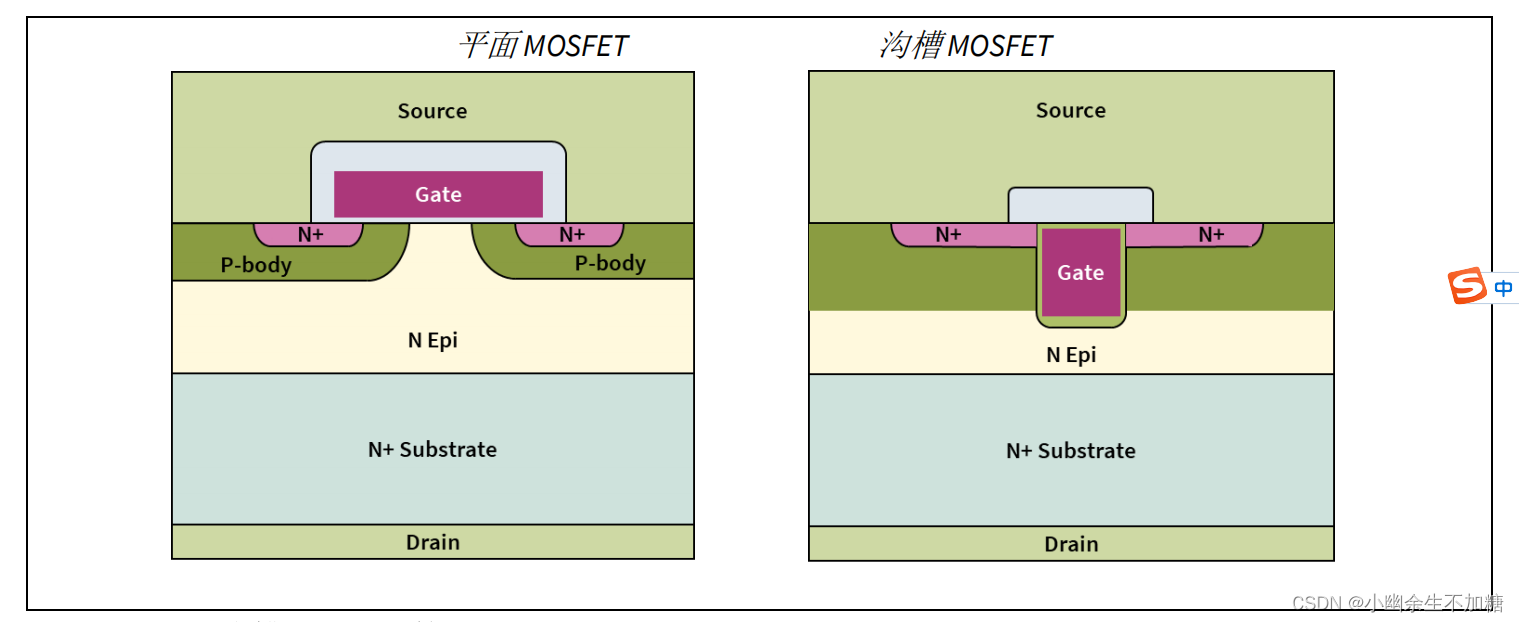

构成 MOSFET 管芯的硅的不同掺杂方式将 MOSFET 分成两个技术大类,即平面型和沟槽型,如图 所示。

2.反向阻断特性

所有功率 MOSFET 器件都有额定最大反向电压,即 V(BR)DSS。如果漏源电压超过此限制,则会在反向偏置的p-n 结上产生高电场。由于强电离的作用,这些高电场会产生电子-空穴对,它们会出现不受控制的倍增效

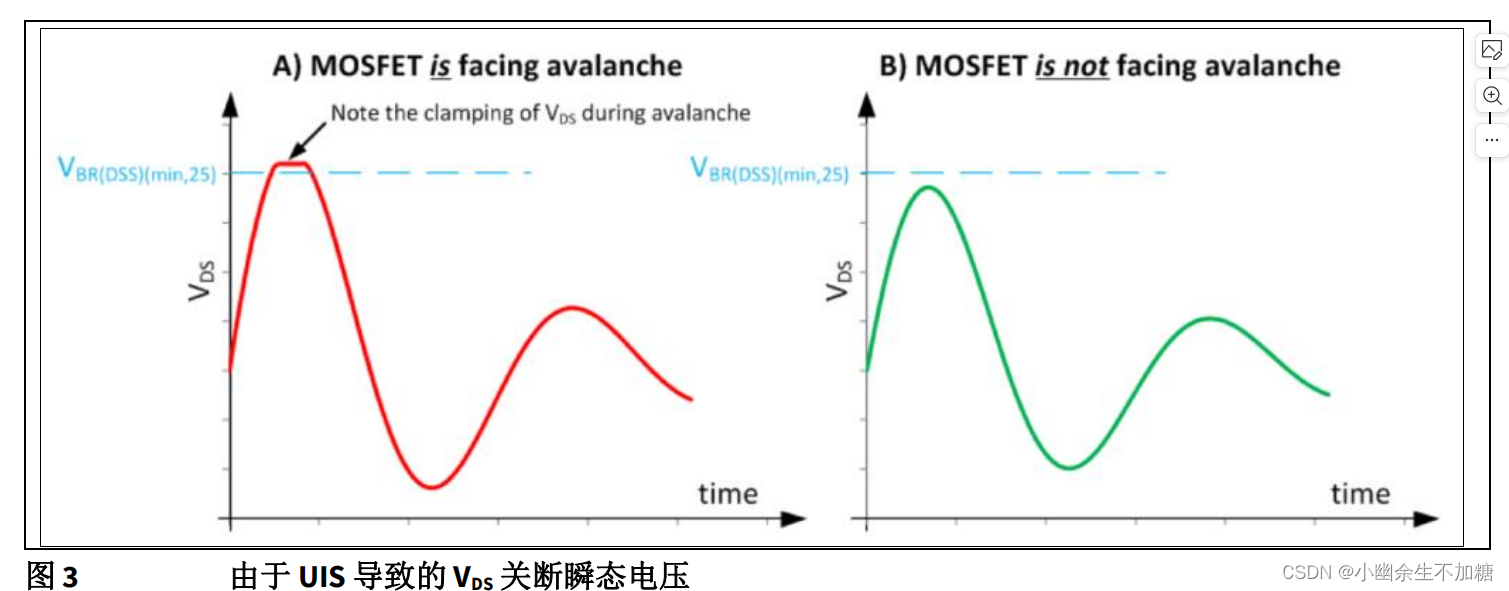

应,导致载流子浓度进一步增加。这就是雪崩效应,会导致流经器件的电流增加,从而导致高功耗、快速升温和潜在的器件损坏。在超过 MOSFET 的击穿电压时,通常会发生雪崩,这通常是由于非钳位电感开关(UIS) 造成的,其中器件的使用超出了其数据表规范。因此,应尽一切合理努力避免 MOSFET 工作在雪崩状态。实际上,在大电流应用中,由于 MOSFET 封装和 PCB 走线中的寄生电感或变压器漏感(例如在反激式转换器中),会导致关断瞬态高压。通过漏极电压的钳位效应可观察雪崩。

2.1 雪崩失效机制

1.闩锁效应

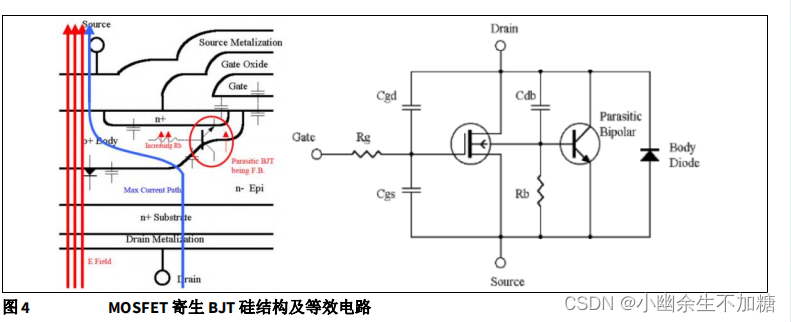

在这种情况下,雪崩事件会产生漏极电流,在电场强度更大的位置,漏极电流也会更大。闩锁效应是由寄生 在功率 MOSFET 中的 NPN 双极结型晶体管 (BJT)产生。如果器件的结构使得寄生 BJT 附近的电场很高,则大量电流将流过其基极电阻,从而在基极和发射极之间产生电压。如果此电压达到某个阈值,双极晶体管就会导通,大部分雪崩电流会流经它,从而产生潜在的破坏性影响,因为没有办法可以控制电流。

2.热失效

当 MOSFET 的结温达到 Tj,destr时,就会发生热损坏。Tj,destr 接近硅材料的本征温度,在这个温度时热载流子的密度等于本地掺杂的浓度。因此,当达到这样的温度时,MOSFET 将不再像半导体器件那样工作。

2.2 雪崩测试

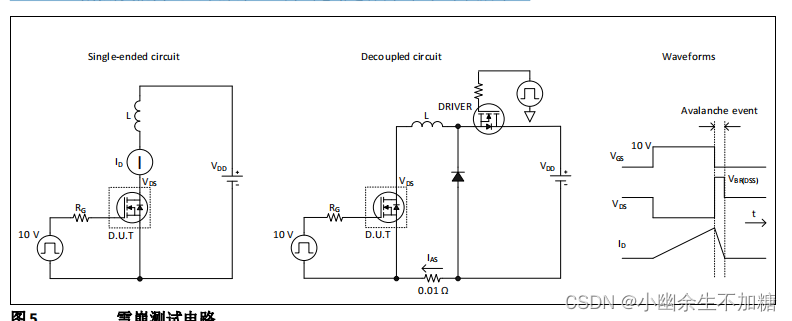

MOSFET 雪崩耐受能力通过单脉冲 UIS 测试电路进行测试,如下图所示。

在这些电路中,特定时长的脉冲施加到 MOSFET 栅极以导通器件,漏极电流因串联电感而线性上升。然后

MOSFET 关断,此时会出现较大的负 di/dt,从而产生瞬变电压。在去耦电路中,两个 MOSFET 同时导通和

关断,因此电感电压等于施加在 MOSFET 漏极和源极之间的电压。关断瞬态上升至 V(BR)DSS 以上,这样在雪崩条件下,存储在电感中的能量(由脉冲长度和电感定义)可以传输到 MOSFET。

2.3 如何避免雪崩事件

首先,有必要为应用选择具有正确 V(BR)DSS 额定值的器件。这意味着在最坏的工作条件下,器件漏极和源极

两端的最大稳态电压应考虑至少 20% 的安全裕度。在可能发生大的关断瞬态情况下,将需要更高的安全裕

度来实现可靠操作。

例如,在电机驱动逆变器中,采用 MOSFET V(BR)DSS 额定值为 DC 总线电压两倍的情况并不少见。然而,选择比所需额定值更高的器件是错误的,因为这会带来更高的 RDS(on),而且成本也可能更高。

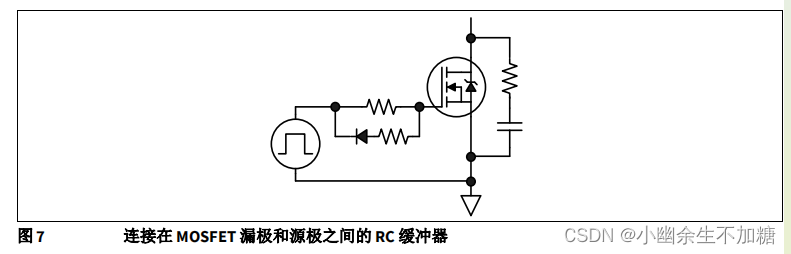

用于减少关断瞬态的方法包括通过调整栅极驱动网络来减缓 MOSFET 的关断速度,以及在漏极和源极之间

添加 RC 缓冲器。当然,这两种方法都会造成额外的开关损耗,从而降低系统效率。

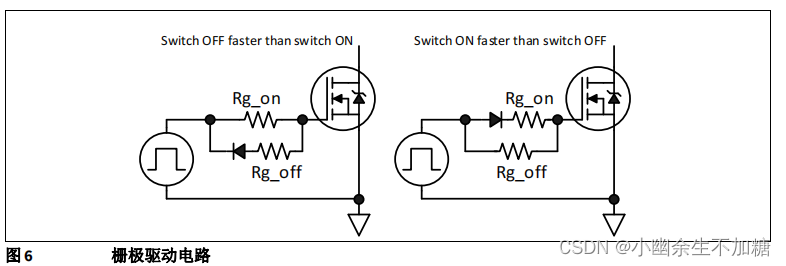

根据设计的具体情况,上述栅极驱动电路之一可用于控制导通和关断速度。调整 Rg_off 可使设计人员在不影

响导通速度的情况下降低关断瞬态电压。然而,在硬开关半桥电路中,Rg_off 值不能太高,因为这可能会导

致在低侧栅极处出现感应导通尖峰,此现象由CGD.di/dt 效应引起。如果值足够大,此尖峰可能会超过MOSFET VGS(th),并产生危险的击穿电流。

仔细考虑栅极驱动电阻值对于在最小化关断瞬态振幅、避免感应导通(如适用)和控制 EMI 之间实现最佳平衡至关重要。

如前所述,可以在漏极和源极之间添加一个串联 RC 缓冲器,以吸收一些关断瞬态,从而降低其峰值电压; 然而,这会产生额外的开通损耗。

3.MOS管额定电流和散热

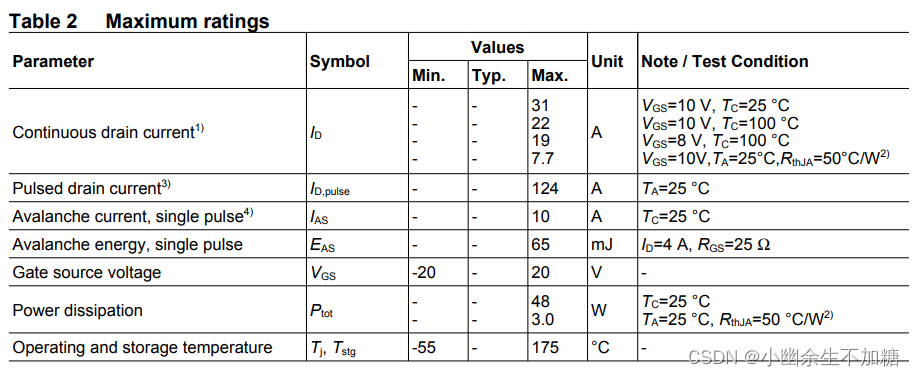

没有经验的用户可能会认为 MOSFET 数据手册上的连续漏极额定电流 ID(MAX) 代表器件在实际系统中的工作电流。

事实并非如此!

此类 ID(MAX) 额定值基于实际设计中无法实现的理想测试条件。测试条件通常涉及非常大的散热器或通过人工冷却将管芯温度保持在较低水平。

应该注意的是,不同制造商使用不同的标准(有些标准比其他标准更保守)来确定其 MOSFET ID(MAX) 额定

值,这些方法也在随着时间的推移而发展。

因此,通过这些额定值来比较不同器件的能力是错误的!

作为第一个标准,比较 25°C 时的 RDS(on) 很有用,因为这为比较提供了通用基础。RDS(on) 由串联管芯和封装电阻组成,前者取决于栅源电压 VGS。

RDS(on) 与结壳热阻 RTH(JC) 结合使用,可以更好地显示功率 MOSFET 的真实电流承载能力。

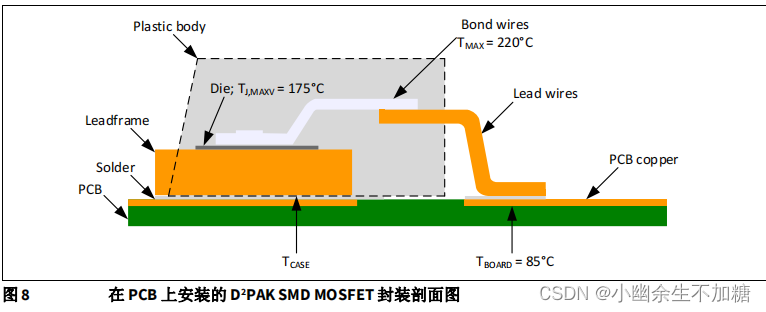

以下焊接到 PCB 上的典型的 SMD 封装 功率 MOSFET 的剖面图提供了更清晰的图像。管芯底部连接到金属片,使漏极与电路板相连接。源极和栅极连接通过键合线连接到形成外部引线的引线框架。由于漏极电流流经源极,因此使用了几根键合线,有时还会用到几根源极引线。在一些大电流器件中,会使用铜夹代替源极键合线以实现更低的电阻。

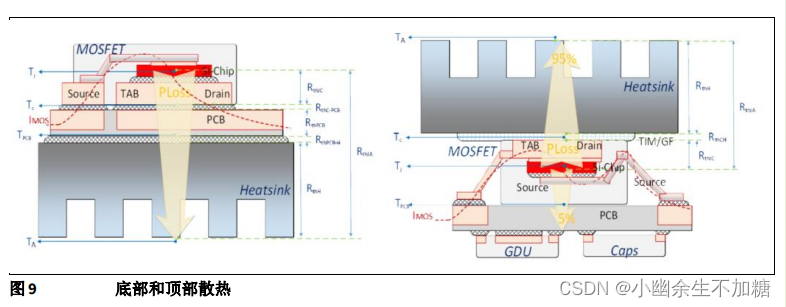

显然,当电流通过漏源路径时,会产生导通损耗,并产生热量。开关功率转换器也会产生开关损耗,每个

开关周期都会消耗一定的能量,开关损耗与频率有关。总损耗包括导通损耗和开关损耗,通过封装顶部和/

或底部传输出去。散热方式因封装而异。大多数封装都是底部或背部散热,如上例所示,其中大部分热量通过漏极散热片传递到 PCB,这需要在漏极焊盘下方添加大量热通孔以将热量传递到电路板底部。然后可以在电路板下方安装散热器。也有顶部散热封装,如 TOLT 封装,其封装内的管芯和引线框架的内部布局不同;它们在封装顶部有一个裸露的金属焊盘,可以用来安装散热器。

散热器尺寸必须能够从 MOSFET 管芯传递足够的热量,使其结温保持在最大额定水平以下。必须首先选择正确的 MOSFET 管芯尺寸和封装以限制功率损耗,接着必须选择合适的散热器来保持安全结温。

除了散热器尺寸和表面积(由翅片的形状和数量决定)外,还必须考虑结至环境热阻。这取决于所使用的散热器布局,可以通过将结与散热器之间的所有串联热阻(包括 PCB、隔热材料/TIM 等)以及散热器本身

的热阻相加来计算热阻(参见 图 9)。显然,需要低结至环境热阻来有效地传递 MOSFET 管芯的热量,并使其能够安全地传导尽可能高的电流。

总之,从电流处理的角度来看整体情况比过分关注数据手册的 ID(MAX) 额定值更有意义。