Zynq和FPGA区别——快速认识Zynq开发

ZYNQ包含了2个部分,双核的ARM和FPGA。根据Xilinx提供的手册,用ARM实现的模块被称为PS,而用FPGA实现的模块被称为PL。简单的说FPA更偏向于逻辑,不跑系统。

ZYNQ内部包含PS和PL两部分,ZYNQ开发有一下四种方式:

文章目录

前言

ZYNQ是赛灵思公司(Xilinx)推出的新一代全可编程片上系统,它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

ZYNQ旨在为视频监控、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。这款基于ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力等要求。

一、单纯做纯PS/PL开发

1、纯PS开发

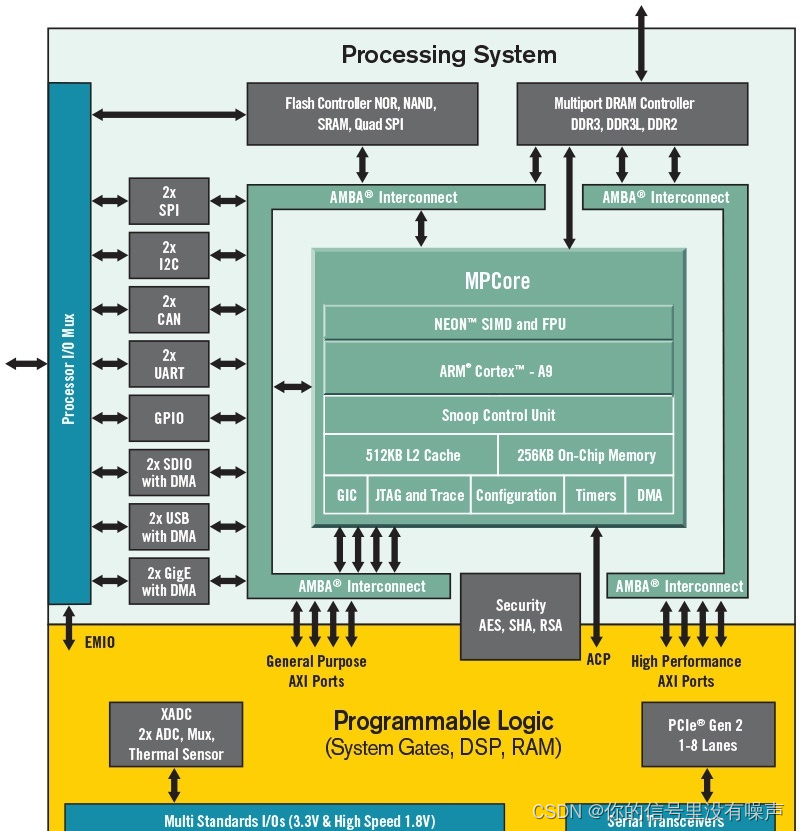

PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS中包含以下4个主要功能模块:

Application processor unit (APU)

Memory interfaces

I/O peripherals (IOP)

Interconnect

PS开发有两种方式:即传统的arm的方式和xilinx方法(这个是生成一个elf文件,这个elf文件包括了硬件配置信息(xmp)和裸跑程序(c文件))。

2、纯PL开发

PL即FPGA,这个和一般的xilinx的FPGA没有很大的区别。

二、混合在一起开发

3、PS+PL(不跑操作系统)开发

生成elf文件包括了硬件配置信息(xmp)和裸跑程序(c文件),还有一个.bit文件。

4、PS+PL(跑操作系统)开发

这个就需要BOOT.BIN,设备树,linux内核镜像,文件系统了。

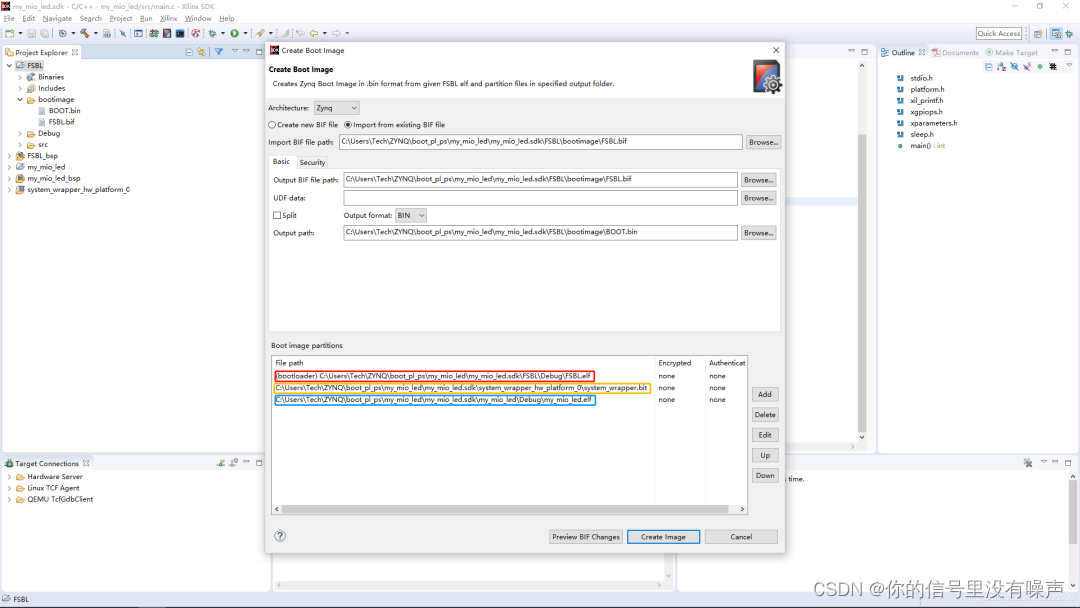

其中BOOT.BIN是由3部分组成的(boot.elf, .bit, fsbl.elf),boot.elf这个是由交叉编译环境产生的,相当于ssbl,.bit文件是PL使用文件,fsbl.elf这个是fsbl。

之前刚开始学FPGA的时候用的是基于spartan的FPGA开发板,当上手ZYNQ后一直以为ZYNQ就是在资源上做了升级,我所要做的工作无非是把开发工具从ISE升级到VIVADO罢了,后来发现自己还是过于天真了,很多事都有存在的意思,上手之后便发现ZYNQ和之前的板子有区别。

三、SOC FPGA

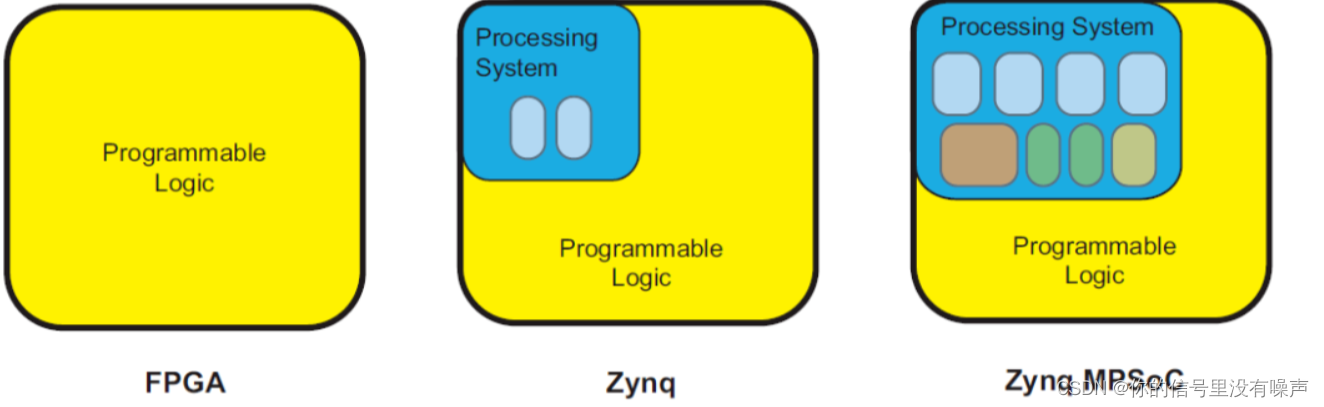

区别就是ZYNQ除了传统FPGA外,还把ARM核和FPGA结合在了一起,成为了内嵌处理器硬核的FPGA,即SOC FPGA,二者利用高速总线AXI4进行通信。

内部结构 PL与PS

由于它既有FPGA又有ARM,所以它同时具有ARM软件的可编程性和FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。

从结构来看,支持FPGA的部分称为PL(Programmable Logic),支持ARM的部分称为PS(Processing System),如下图所示。

可以看出PS部分有很多接口,如SPI,UART,CAN等等,这些接口的存在可以让FPGA不用写控制器去传输,节省了资源但是牺牲了速度。

可以看出PS部分有很多接口,如SPI,UART,CAN等等,这些接口的存在可以让FPGA不用写控制器去传输,节省了资源但是牺牲了速度。

工作

PL端和PS端一般通过AXI4总线通信,使用AXI4的PL模块会有相应c驱动文件,用于PL端模块的控制。这些驱动文件有裸机版本,也有linux版本,linux运行时,如果调用pl端模块就使用这些驱动即可。

Zynq的启动分三个阶段。阶段0是BOOTROM的固化代码,不用管;阶段1中,first stage boot loader 首先配置PS端,之后硬件比特流对PL进行配置。阶段2运行用户程序,Linux的BOOT loader在这个阶段才开始运行。

ZYNQ并不能说是一个嵌入ARM核的FPGA。从它的启动过程就可以发现,绝对是ARM主导的,因此称它为以高性能FPGA为外设的双核ARM或许更为合适。

那么就有一个问题Zynq可以作为独立的ARM或者独立的FPGA使用吗?答案是肯定的,可以的。

首先,Zynq可以作为独立的ARM使用是显而易见的,因为Zynq中ARM就是主处理器,上电启动过程也是由ARM来完成的,除了新建ARM工程时需要HDL硬件描述文件(HDL硬件描述文件的制作也很简单),其他都一样。

其次,Zynq作为独立的FPGA使用其实也是可以的,首先我们可以跟使用传统的FPGA一样使用Vivado集成开发环境综合编译工程并通过JTAG接口下载bit文件。唯一的不同是在我们烧写启动时,我们需要把bit文件和FSBL源码合成为一个bin文件烧写后才能启动,上电启动时ARM会先运行加载FSBL程序,然后通过FSBL会加载FPGA的程序。FSBL程序是Xilinx提供的集成在SDK里的二级boot loader程序,我们在SDK集成开发环境中通过很简单的操作就可以完成FSBL程序和bit文件的合成。

上图中红色框框出来的是二级boot loader程序,黄色框框出来的是FPGA程序,蓝色框框出来的是ARM的用户应用程序,如果我们把Zynq作为独立的FPGA使用时,我们就可以删除蓝色框即ARM用户应用程序,保留红色框二级boot loader程序和黄色框FPGA程序即可。

在功耗方面总结

FPGA和SoC设备的功耗是密切相关的,因为所有的SoC都包括一个与FPGA有效相同的PL区域。与Zynq和Zynq MPSoC相比,Zynq MPSoC器件的中的功耗(每个逻辑单元)较低,整体性能较高,这是由于UltraScale+ FPGA体系结构的各种优化所致。在PS方面,Zynq MPSoC体系结构更加复杂,提供了更高的性能,还包括了电源管理等附加特征。