知识就像货币,流动才有意义。

一、前言

因为我是做硬件的,想用这样一篇文章介绍一下我们常见的电脑主板,或者说电路板卡,是怎么设计出来的。仅以技术之所学,得此文章,若有表达不周之处,欢迎反馈。

首先我想用这样一个例子来说明一下我们的工作究竟是什么情况。我们对板卡的设计,以汽车来举例,就相当于我们拿到一台常规、一般的“通用”汽车。我们的用户有不同的需求,有的希望这辆车的轮胎大一些,便于他跋山涉水;有的希望这辆车的灯光亮一些,便于他夜间行驶;有的希望这辆车油耗低续航长,便于他以较低成本的方式高频次使用.....所以我们的工作,就是不断“改造”,修改成不同的配置,以满足不同的客户。

随着硬件电路不断的集成化,很多的电路设计已经放在芯片里面,所以我们就像是4S店,维修改造,搭积木,芯片原厂就相当于汽车官方原厂,虽然这个举例不免有拉低地位之嫌,但事实确实如此。

幸运的是目前的市场上仍需要很多很多的4S店,因此也有我们存在的意义;

幸运的是也有不少“4S店的员工”会去专研技术,深入学习研究每一个零部件存在的意义、原理,甚至精通如何“改造”能让这辆车变得非常可靠安全的同时,费用更低。

下面步入正文。

[其他设计要点未尽事宜,在我此前的文章大多都有提到,且阐述可能会更详细,可移步查阅。]

以Intel为例,电脑主板肉眼可见的主要组成部分如下

1 |

CPU |

7 |

HDMI/DP接口 |

2 |

PCH |

8 |

M2接口 |

3 |

内存DDR/插槽 |

9 |

SATA插槽 |

4 |

EC/MCU |

10 |

PCIE插槽 |

5 |

网卡IC及网口 |

11 |

风扇接口 |

6 |

USB接口 |

12 |

ATX电源接口 |

CPU

CPU在主板中主要肩负着数据运算的功能,这倒没什么特别的,同一个厂商的不同CPU在封装上可能是兼容的,只是功能不一样,因此选取的时候需要确认这点。关键参数还看CPU核数,主频等。

PCH

PCH是一颗独立的芯片,在主板中的重要性可以说仅次于CPU,是一个集成了SATA、HDMI、PCIE、USB等硬件接口的芯片,通过DMI通道将数据传输给CPU。

对于国产飞腾来说,X100套片跟PCH的作用是非常相似的,X100通过PCIE与CPU通信。

内存

内存要么是板载内存,容量固定好了,要么是有内存插槽,可以插入自己购买的内存条。

以上部分的电路,一般是直接通过原厂获取的,原厂会有一份参考设计,内存部分layout会希望直接参考走线,原理图部分其实差异不会太大,主要是芯片型号和数量的区别。其余部分就看需求与硬件工程师的功力了。

二、确立需求

客户会告诉我们板卡要做成什么样子,一般会规范形成一份文件,文件内容非常清晰的说明了这个产品的所有信息,比如CPU是否有指定需求,主频多少,内存要多大,板载内存还是插件内存条的方式,要多少个SATA硬盘接口,PCIe、RJ45网口、USB接口的数量以及速率要求,显示接口是HDMI还是TYPE-C还是其他类型,研发周期多长,物料是否要全国产化,等等。

前期不要闲麻烦,一定要把这些信息提前确定好,能避免后面的可能跟客户重复低效沟通的场景,最差的情况是客户希望做的是这样,而你理解的是那样,做出来的便是那样,最后会很尴尬。

因为硬件工程师是前期对接客户的,后面还有整个服务链包括PCB工程师,采购,生产等等,前期出问题,后面这条链路都会受到影响,所以一定要尽力一次做对,虽然我们不是神,无法保证百分百正确,但是我们可以通过自己的细心、实力等方式,无限趋近于完美。

我做东西的一个特点是,把需求捋清楚以后,先做一个硬件框图,检查所选的芯片是否能满足要求。我觉得先做框图的意义,不仅仅能够帮助我们以一个更高的角度去统筹规划我们的设计,更是能够在设计过程中,一边设计一边辅助检查我们的图纸,同时方便别的工程师初次查阅时能很快的熟悉这个设计方案。所以画图的美感就很重要,你敢相信,我将一个CPU主板的框图画成一个机器人的形状……

其实是因为这并不是一个电脑主板,而是一块核心板,通过业界的标准口,将Intel的CPU和南桥基本所有的资源都拉出来到左右两边的Come口,对应的配板板卡,也称底板,通过所匹配的接口,接受信号,做成类似主板的形态。

三、电源设计

电源的设计在主板中可以说重中之中,电脑电脑,这个字就占了一半,在板卡中无处不在。DC-DC在主板中呈分布式,一般某一个功能的芯片,会配以专门的电源芯片,少部分以公用的形式。

电源接口

主板的供电接口大多是ATX,如下图,其特点是传递功率大,单PIN大约能通过9A电流,性能可靠。在选型的时候,需要考虑整个板子的最大功率来确定电源座子的引脚数,因为电流需要回流,所以是按照连接器的一半引脚数计算功率。

我们在进行电源设计的时候,有如下考虑。

满足负载功率

比如CPU的主供电为0.8V,需要查看规格书,确认该电压的最大电流(满载运行时),所选的DC-DC输出电流一定要大于这个规格,甚至要留有余量,一般可以预留百分之二十。不仅如此,还要横向对比,CPU可能会有不同的型号,比如商业版,工业版,等等,负载电流可能是不一样的,设计时要按照最大规格,以满足未来不同的场景。

其他

这里就很笼统了,选型时还要考虑芯片效率,静态电流,响应,原生支持度,是否需要国产化,芯片是否稳定,便于采购购买,等等,需要考虑的因素很多。事实上,DC-DC在板卡上的设计,专门用一本书可能都讲不完,这里只是侧重于主板形态的电源设计主要需要关注的地方,不细化阐述。

CPU主要电源

对于CPU还说,其他的电源都是通过常见的DCDC产生,但是其核心电源,会通过SVID协议,CPU自己控制自己的供电,达到动态电压的效果,以实现降低功耗的目的。所以这部分设计,外部软件上不会参与太多。

怎么知道电源拓扑有没有问题,以后需要提供相关文档给客户的时候怎么办,因此,对关键电源部分,可以做这样一个表格,进行评估,主要是包括芯片的输出能力,以及负载的数据,甚至还可以加上采购方面的数据,都可以。

供电 分析 |

|

供电网络 |

芯片 |

输出能力 |

负载 |

评估 |

1 |

DDR4(CPU端+颗粒) |

马赛克 |

8A MAX ; 10A PEAK |

4.3A+5.6A=9.9A |

惯例,基本可行 |

|

2 |

VCCIN AUX_CPU |

马赛克 |

32A MAX |

26.5A |

可行 |

|

3 |

VCCIN_AUX_PCH |

马赛克 |

32A MAX |

14.9A |

可行 |

|

4 |

VCCIN |

马赛克 |

30AX4=120A |

74A |

可行 |

DDR4 |

1 |

VDDQ |

DRAM端VDDQ |

1.2V |

5.6A |

马赛克 |

2 |

VTT |

|

0.6V |

1.1A |

马赛克 |

|

3 |

VPP |

|

2.5V |

1A |

马赛克 |

|

4 |

VREF |

|

VDD2/2 |

- |

电阻分压 |

一般板子上会有A类电源(Always,或者STB待机)和S类电源(System),A类电源需要保持永远存在,而S类电源是系统运行时才有,所以在电源网络规划中,可以用驱动能力较强的DC-DC输出A类电源,通过MOS管控制S类电源的输出,需要注意的是,一定要缓启动,因为后面的负载电容通常而言非常大,打开瞬间冲击电流会很大,稍不注意电压就起不来。

当然,系统电源也可以采用DCDC产生的方式。

四、时序设计

供电跟时序是息息相关的,通过控制DC-DC使能,达到某一时刻上电的要求,在X86架构中,电源网络非常复杂,在电源设计时,一定要确保这个电源网络能够满足时序要求。

时序主要以EC或者CPLD等控制为主,硬件电路自相控制为辅。如下图,Intel架构中,CPU或者PCH会在某一时刻通过某些GPIO响应,相当于,芯片自己可以参与到自己的时序当中,只要我们通过硬件手段连接即可。

如下图,将Intel某个平台的CPU和PCH所有电源引脚罗列出来,确保关注到,提高设计正确率。

这是我整理的该平台时序,可以看到步骤非常多,设计上稍有不慎,电路就很难跑起来。

时序分为软件控制与硬件处理,将需要软件工程师操作的信号罗列好,把对应PIN定义备注好更佳。

五、EC设计

EC在板卡中,是常供电,主要肩负着时序控制、键盘管理等功能。设计上需要注意电平问题,比较多的EC通常是3.3V供电,如果其GPIO跟某些1.8V电平芯片的信号对接的话,需要增加电平转换电路。

这里需要注意的是,不是所有板卡的时序管理芯片都是EC,也可能是CPLD或者FPGA等,因为有的CPU的某些信号电源域的电压实在太低了,低于3.3V,甚至低于1.8V,所以直接使用低压的时序芯片会更好。

在时序电路上,DCDC一般会有EN引脚和PG引脚,要做到检测到上一个信号的PG为有效电平时,才去触发下一个信号的使能,这对板卡第一次上电尤其重要,否则出问题的话真的是板毁人郁闷。

六、网口设计

板卡的千兆网口,通常是使用GMI转MDI的PHY芯片,或者是PCIE转MDI的芯片。如果是PCIE转出来,需要确认使用PCIE的lane数,确定带宽,比如某个网卡芯片支持PCIE*2,PCIE*4,输出为四个10/100/1000M网口,如果因为内部资源原因只能提供两路PCIE到这个网卡芯片,那根据带宽计算,是无法满足四个网口同时支持千兆速率的,所以带宽这个地方要考虑好。

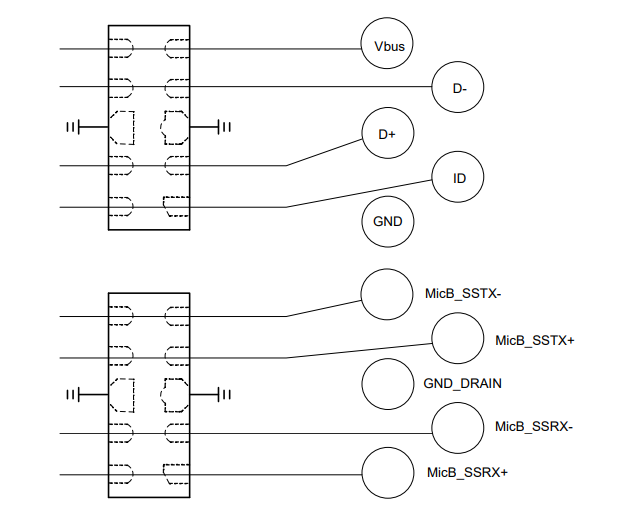

七、USB、DP等设计

这些常见的海岸线接口,如果是INTEL,那基本是用PCH出来的,如果是国产飞腾,基本是通过其搭配的X100套片引出。

这些地方设计的难度并不大,做好对应的AC耦合,确定耦合电容大小,上共模电感,接口处ESD IC基本就差不多了。要注意不同信号,相同信号的不同版本耦合电容都可能不一样,需要明确,相关内容我之前的文章有说过。

共模电感3D图:(来源TDK)

也叫共模扼流圈,应用在差分信号中,用来抑制共模信号。在USB信号上,使用共模电感需要注意直流阻抗,选取时这个参数越小越好。

八、PCIE、SATA设计

一些可拔插的网卡声卡,有一排金手指就是PCIE接口实现的,还有那些M2接口的NVMe盘,跑的也是PCIE协议,如果没有写NVMe,那就是跑的SATA协议。

PCIE是差分信号,在信号上要接AC耦合电容,如果是发送端,就在靠近芯片端,所以接口设计上,如果是PCIEX16那种座子,座子旁边是不需要放电容的,电容要么在主板的芯片端,要么在设备端。

电路上一般会有很多的PCIE设备,这个时候首先需要考虑CPU端是否能够按照这样方式拆分,然后确认时钟是否够用,剩下的直连,给供电就可以了。

如果整个系统的PCIE设备很多,一般会在PCIE复位信号上加上buff,增强驱动能力。

SATA的电路,通常直接从芯片端发出来,然后配以耦合电容,提供电源,就差不多了。

九、接口设计

常见的接口如USB,设计上首要做的是限流保护,可以是专门的IC,可以是自恢复保险丝等,因为产品到用户的手上,无法预知对方会有什么神奇的操作,可能会将一块可以导电的物体插入USB口,导致电路板的电源和地短路,为了确保局部异常不影响主机,加上限流IC以后可以在USB端口过流时切断供电,保证系统的5V电压依旧是正常的,只是暂时无法使用USB接口而已。

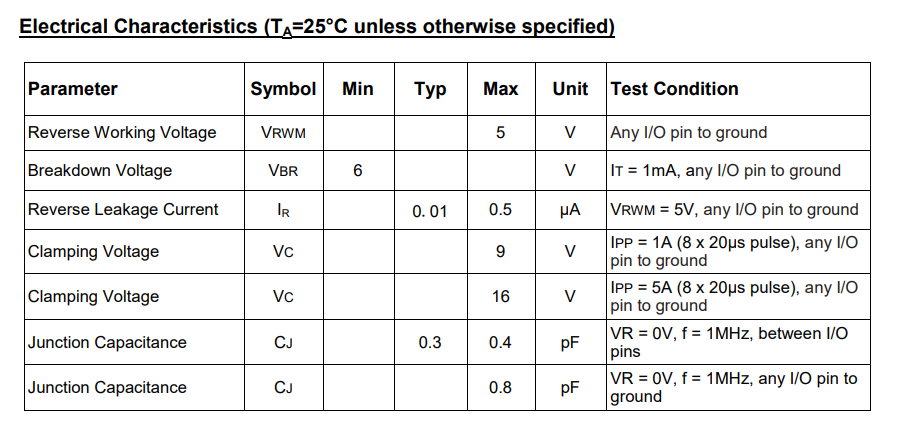

ESD防护,静电防护非常重要,轻则对芯片工作状态有影响,重则烧毁芯片。一般芯片GPIO引脚会有一定的防护等级,规格书会说明,通常防护能力较低,需要外部加上专门的ESD芯片。

常用ESD模型:

不同的信号选取的ESD会有差别

1、信号工作电压要小于ESD的VRWM。这才能在接口电压高于信号工作电压时才发生触发。

2、理论上ESD的寄生电容越小,对信号的上升和下降速度影响越小。所以速率越高的信号,选取的ESD寄生电容要更小,USB3.0的建议低于0.5PF。

3、确定被保护IC的钳位电压

4、确认防护等级,如IEC 61000-4-2_4,接触8KV,空气15KV。防护等级通常而言,跟芯片的封装大小有直接关系,封装越大,能承受的静电越高。.

下图是某ESD的关键特性:

如果是拔插类的排针等接口,最好做到防呆,防止用户误操作造成损坏。

十、EMC设计

EMC,电磁兼容,设备在运行时会对外界产生电磁骚扰,同时,该设备在运行时也会受到周围产品产生的干扰,其需要具备一定的抗扰能力。这个词更倾向于整个产品而言,而不是单独的一块板卡。EMC和下面的可靠性都需要一定的工作经验,还有足够的专研精神才能设计好,而且这两篇涉及的内容其实很多。

十一、热设计

一般来说器件的可靠性、寿命与工作温度成反比,因此热设计在产品思维中非常重要,我们既要保证产品能够正常工作,还要尽量使其在不同的环境中可靠运行。

热设计其实是倾向于layout来说的,当然了,一般大功率板卡都会设计有风扇。对于layout来说,主要是合理布局,将板卡的热源诸如CPU,DC-DC等在不影响功能的前提下,合理分布,不能将所有DC-DC都放在一边,甚至靠近容易受温度影响的器件。

这里有一个知识点,究竟一个芯片,该用多大的散热片,该用多大的风扇,这里涉及的知识点其实很多,其中对于芯片来说,一般规格书会有一个参数,TDP,就是热量设计功耗,意思是芯片在满负荷运行时释放出来的热量,我们在选用散热片和风扇时,需要考虑这个因素。

十二、可靠性

产品的设计严格上要能通过企业标准的可靠性(高温、高湿、低温,反复开关机等)、兼容性(接口对不同设备的识别率等)、电性能(高速信号眼图、阻抗标准)、EMC(辐射、抗干扰)等测试。可靠性需要结合测试情况进行处理整改。

因为产品会在不同的地区使用,可能环境天差地别,有的工作环境温度很高,有的工作环境温度很低,因此产品设计之初,就需要考虑到板卡的性能是否能够承受住复杂环境的考验,因此出货前的测试尤为重要。

总结来说,通过测试去提前发现问题,解决问题,让产品更可靠,对于口碑的提高和减少售后问题降低经营成本有着重要意义。

十三、物料选型

1、大量发货产品选择器件最重要的就是要能持续稳定供应,因此要物料要谨慎选择,尤其是一些好多年前的产品,不仅性能可能跟不上,还有供应风险。

2、一片板卡上的物料,能合并的尽量合并,比如有两个功能芯片分别需要用到DC-DC支持供电,那尽量选择同一家供应商的DC-DC,方便采购。

3、原则上最好选择有实力的供应商,其产品出货稳定,质量通常也有保障。

4、不少国产芯片会跟外国比如TI的芯片是PIN TO PIN的,所以关键时候是能够替代使用。

十四、调试顺序

板卡设计完成,打样回来以后,有如下调试顺序:

上电前,目测板卡表面状态,确认是否有明显的焊锡粘连,元器件接触不良等现象,使用万用表测量供电接口,确保没有短路。

准备上电时,电压源设置一个比较低的限流保护,这样即使真的有过流情况也能极大的减少损失

上电后板卡正常无异常,电流正常时,安排软件工程师烧录时序代码。

按照主要到次要,功能块逐步调试,先调试CPU,检查时序是否满足,是否有跑起来的现象,然后调试其他功能,比如网卡,声卡等等。

MCU/EC/CPLD调试

一般来说,板卡最先调试的就是掌管全局供电的芯片,通常是MCU或者CPLD等,笔记本基本是EC。这类芯片比较简单,确认供电,复位信号,如果是外部时钟的话也需要看一下,基本就能跑起来了,然后软件工程师烧录代码,时序当然是硬件做的,因为硬件最清楚整个板卡逻辑要怎么跑。

CPU调试

根据CPU规格书,提供合理的时序后,CPU如果能够跑起来,会先通过SPI信号读取BIOS,所以我们可以测量FLASH信号的DATA或者CLK,一步到位就是测量FLASH的DATA OUT,也就是CPU端的DATA IN,如果有正常的波形,说明CPU已经跑了一部分,正在读取配置文件。同时,还可以搭配比如CPU发出的进程信号,PWRGOOD等,确保给到CPU的时钟幅值和频率都是正常的,供电后时刻关注芯片是否有温度,如果还是冷冰冰的,信号都暂时不需要测量了,需要确认启动的相关信号。

PCH调试

Intel的PCH启动跟CPU密切相关,我理解为是一起起来的,因为他们通过一些引脚信号,互相传递,左一步右一步,仔细看时序会发现两者时序是互相交叉的。

我们要使用EC去获取PCH的数据、状态,一般是通过LPC或者ESPI进行数据传输的,ESPI是更新的一种协议,主要是为了取代LPC。这两者都是类似IIC一样,一主多从的连接方式,如果是使用的LPC,还需要确认电路是否有正常产生对应的LPC时钟,通常是33MHz。

时钟调试

在主板中,PCIE是用得非常多的,因此基本都会有专门的PCIE时钟芯片,国产也好,非国产的也罢,通常该芯片是输入一个固定的时钟比如25M,然后通过IIC或者其他方式或者直接固定输出某个频率的时钟,如果是专门的PCIE时钟芯片,那输出就都是100M。

一般在CPU和PCH或者主要的芯片工作起来之前,时钟就要先产生了,因此,电源域上要保证时钟芯片的供给是在第一梯队,接在STB类电源上。

网卡调试

首要确保供电都是正常的,确认时序是要有满足要求,如果有时钟输入,确认信号频率,幅值,有必要的话测试电源纹波,上升时间、晶振的频偏。

网卡一般也是需要有一个专门的FLASH,所以如果此芯片工作不正常,可以直接测量芯片是否有向FLASH读取数据,用示波器测量波形,如果有波形,说明供电复位基本都是正常的,芯片已经开始尝试读取指令了,此时需要确认固件是否是验证过的。如果没有任何波形,就需要确认好电路上下拉配置、电源等等。

如果芯片工作没问题,是PCIE转出去的话,首先能在系统上看到该PCIE设备,一般是带有芯片名称相关的标题。然后进网络管理器查看,固件正确的话,配置相关的IP就可以ping出去了。

十五、测试

功能调试完以后,需要送去安排测试,就是要保证这个板卡不仅仅能用,还能在复杂环境下稳定工作。然后要跟踪测试过程中遇到的问题,及时整改。

同时,事实上很多板子是很难做到一次性做对的,所以就要在使用和测试过程中发现问题,作为硬件工程师,将这些问题记录好,然后一次改版好。

十六、总结

调试每一部分的时候,最好提前研读该芯片的规格书,做到心中有数,才能在上电,左手万用表右手示波器的时候不慌不忙,确保整个调试过程思路清晰,一步一步解决。

其实板卡做多了,感觉通过那一套规则就能设计好调试好,在此之上,如果还能投以兴趣,加以时间积累,那做出来的板卡一定是美观可靠的。