在今年8月的中国研究生集成电路创新大赛上,T-Head发起了设计挑战:基于玄铁Open E902构建双核TEE安全解决方案。在这次比赛中,有很多优秀的设计,一些团队主动分享他们的设计。广东理工大学的ReShaker团队在比赛中获得一等奖,他们在博客中介绍了他们的设计。

可信执行环境(TEE)是一种有效的信息安全方式。为了获得更高的效率,构建具有TEE安全能力的双核片上系统(SoC)是最热门的话题。然而,TEE SoC目前通常使用复杂的处理器核心,如Rocket,导致资源使用率高;更重要的是,加密单元缺乏灵活性,并且忽略了核心之间的安全通信。

为了解决上述问题,我们设计了一个基于RISC-V的双核TEE SoC。

首先,构建了一个与TEE环境完全隔离的多级总线体系结构,并集成了支持SHA1、AES和RSA算法加速的Secure Core,RSA可以灵活配置为五种不同的密钥长度;此外,还引入了基于信任链(CoT)的安全引导过程,以验证加载程序的真实性和完整性。

IOMP还用于配置富执行环境(REE)CPU和安全核心的访问权限。最后,采用邮箱进行核心间通信,并提出了数据交换的分层访问策略,以确保通信的安全性。

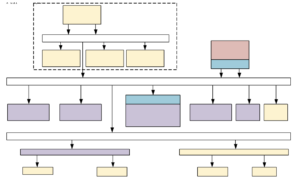

TEE SoC的多层总线体系结构

这项工作中的SoC架构如图1所示。所提出的体系结构使用T-Head开发的两个E902 CPU作为处理器核心。运行在TEE环境中的CPU称为TEE CPU,运行在REE环境中的处理器称为REE CPU。如图1所示,双核SoC采用三层分层总线设计。位于隔离系统中的总线的第一层位于一个名为FL-AHB的安全世界之下。作为主设备,TEE CPU可以访问该总线下的所有设备,如BootRom。总线的这一层不提供对主设备以外的设备的访问。因此,隔离系统是一个完全隔离的环境,内部数据无法直接访问。第二层总线是用于构建TEE系统(SL-AHB)的总线,TEE CPU可以访问该总线层上的所有从属设备。同时,REE CPU的访问被IOMP限制在该总线的从设备上。第三层总线是SL-AHB的子总线,并且被转换为APB总线以连接外围IP(TL-AHB2APBx)。IP被划分并连接到安全和非安全APB总线。对这些IP的访问是基于发起访问的主设备的ID来授予的。在这种设计中,当安全引导完成时,TEE CPU和REE CPU都将从主存中读取相应的代码和数据。从架构中可以看出,两个主设备都可以同时访问主存储器从设备,因此AHB总线在架构中采用循环仲裁,以授予两个CPU相同的优先级,即公平占用总线资源。

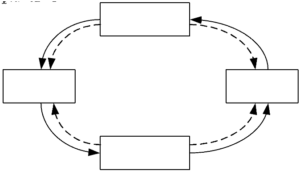

安全引导

安全引导是TEE SoC的必要设计要求,也是确保系统安全的先决条件。在安全引导过程中,通常需要验证代码的真实性和完整性,以确保代码未被篡改。这项工作中设计的安全引导过程如图2所示。双核引导过程分为两个阶段:TEE CPU引导和REE CPU引导。REE CPU将挂起,直到加载并验证代码为止。TEE SoC的安全引导过程如下。

当SoC通电并复位时,TEE CPU首先在BootRom中运行代码。该代码主要负责加载ZSBL代码,并通过安全串行端口将相应的签名携带到隔离系统中的ZSBL RAM。

TEE CPU在ZSBL RAM中执行加载程序的SHA-1提取摘要,并且使用BootRom内的ZSBL代码段的RSA公钥执行签名的解密,用于加载程序的签名验证。当验证通过时,TEE CPU跳到ZSBL RAM运行。

ZSBL首先在SoC中配置IOMP受限访问地址,然后启动安全串口加载TEE_REE代码和RSA私钥签名的代码签名。加载完成后,TEE CPU通过使用Secure Core计算加载的代码和数据的SHA-1摘要,并在开始执行TEE软件堆栈之前使用RSA验证签名。

TEE CPU对REE软件栈中的特定进程执行SHA-1,得到相应的摘要列表,为以后的安全双核通信奠定基础。完成列表生成后,TEE CPU将配置REE CPU引导地址,并将REE CPU的重置信号拉高以启动REE CPU。此时,TEE SoC的安全引导完成。

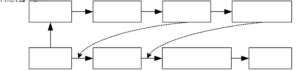

Mailbox的设计

在双核SoC架构中,处理器间通信(IPC)是提供数据通信、事件控制和资源共享的关键。如图3所示,我们使用基于共享内存和核心间中断的邮箱通信,而共享内存是使用FIFO实现的。双核进程可以通过邮箱传输数据,即根据双方法定的交互协议进行读写通信。为了解决共享内存的读写一致性问题,保护共享区域中安全核心的数据安全,TEE CPU和REE CPU分别使用独立的共享内存。基本操作如下,如图3所示,当REE CPU通过邮箱向TEE CPU传输数据时,它首先将数据类型、数据长度和数据写入邮箱的FIFO,当写入完成时,将生成R_Intr信号,通知TEE CPU从邮箱接收数据。当TEE CPU完成接收数据时,它生成R_OK_Intr信号以通知REE CPU该通信完成。类似地,从TEE CPU到REE CPU的数据传输也由R_Intr和R_OK_Intr信号完成。因此,为了实现双核通信,两个处理器核心都需要添加两个邮箱中断响应。

多级访问策略

为了保证双核通信的安全,我们设计了一种基于共享内存的多级访问控制策略。TEE CPU基于多级访问控制策略实现对REE CPU的访问控制,以保护共享内存的安全。我们的TEE SoC提供三种不同的安全访问控制策略。

- 级别1:直接访问策略,不需要任何访问控制,TEE CPU直接向REE CPU提供访问服务,只需要流程满足双核通信的协议。

- 级别2:完整性访问策略,它验证REE CPU进程对安全区域资源的访问,以确保进程代码或数据没有被恶意篡改。

- 级别3:保密性访问策略,包括有效性和完整性访问策略以及数据加密策略,用于对高安全性数据的访问控制,如访问密钥、提取指纹、提取或更改密码、更新安全区内的数据等。

我们指定请求加密的事务是一个机密访问事件,如图4所示。对于这种类型的访问,首先需要对访问任务的代码块进行SHA1,以获得相应的摘要,并将其与安全引导获得的任务代码摘要进行比较,以实现完整性验证。当认证通过时,TEE CPU通过邮箱中的公共共享内存传输密文(使用AES加密)。此时,如果恶意进程截获邮箱读取的值,则该值无效。为了将密钥传输到REE CPU,我们使用安全寄存器和邮箱中仅TEE可写的内存区域进行安全传输。当REE CPU完成接收密文时,TEE CPU将加密密钥写入TEE中的一个单独的内存块(FIFO),而写入安全寄存器有效,并写入中断信号通知REE CPU读取。REE CPU的中断处理器将首先确定安全寄存器的值是否有效,即。,给予REE CPU读取邮箱中只有TEE CPU具有写访问权限的存储区域的权限。当有效时,REE CPU从隔离存储器中读取数据;否则,它将从共享内存中读取。因此,对于机密访问,原始访问过程将该值作为密文返回。当REE接收到密文时,它会调用特定的密钥请求任务来获取AES密钥,这样攻击者就无法轻松获取密钥来解密密文。在我们的方法中,AES密钥不直接暴露于REE。保密任务分两部分传输,第一部分是TEE通过邮箱中的共享内存将加密后的密文发送给REE。第二部分是REE向TEE请求AES密钥,这也验证了密钥请求任务的完整性,为了确保安全,密钥通过隔离存储器传输。

在我们的工作中,一个TEE安全的SoC系统,具有双核RISC-V CPU和多级总线架构。RISC-V新提出的IOMP也被用来限制CPU在非安全环境中的访问权限。为了提高安全引导和加密解密操作的处理效率,我们为RSA、AES和SHA1算法设计了硬件计算单元,并将它们作为安全核心集成到TEE SoC中;对安全核心的访问受到IOMP的限制。同时,我们设计了一个简单的基于CoT的安全引导过程,以确保SoC环境引导的引导时间真实性和完整性。我们使用基于共享内存和内核间中断的邮箱来实现双核通信。我们的架构具有更低的资源消耗、更高的灵活性和更好的安全性,很好地满足了物联网边缘设备的基本安全和计算要求。