处理流程

在指令预取时,如果目标地址是非法的,该指令被标记成有问题的指令。这时,流水线上该指令之前的指令继续执行。当执行到该被标记成有问题的指令时,处理器产生指令预取中止异常中断。

当发生指令预取中止异常中断时,程序要返回到该有问题的指令处,重新读取并执行该指令。因此指令预取中止异常中断程序应该返回到该指令预取中止异常中断的指令处,而不是像前面两种情况下返回到发生中断的指令的下一条指令。

指令预取中止异常中断是当前执行的指令自身产生的,当指令预取中止异常中断产生时,程序计数器 PC 的值还未更新,它指向当前指令的后 2 条指令(对于 ARM 系统来说它指向当前指令地址加 8 个字节的位置,对于 Thumb 指令来说,它指向当前指令加 4 个字节的位置)。

当指令预取中止异常中断发生时,处理器将 PC-4 的值保存到异常模式下的寄存器 LR_mode 中,这是 LR_mode 中的值 即为PC-4 ,即指向当前指令后的第一条指令。因此返回操作需要将 LR_mode - 4(指向当前指令) 赋给 PC,可以通过下面的指令来实现:

SUBS PC, LR, #4 // 注意 S ,指定了 S 意味着同时将SPSR 拷贝到 CPSR

该指令将寄存器 LR 中的值减 4 后,复制到程序计数器 PC 中,实现程序返回,同时将 SPSR_mode 寄存器内容复制到 CPSR 中。

当异常中断处理程序中使用了数据栈时,可以通过下面的指令在异常中断处理程序时保存被中断程序的执行现场,在退出异常中断处理程序时恢复被中断程序的执行现场。异常中断处理程序中使用的数据栈由用户提供。

subs lr, lr, #4

stmdb sp!, {

r0-r12, lr} // 保存现场 r0-r12 - reg_list

// user code

ldmia sp!, {

r0-r12, pc}^ // 恢复现场 r0-r12 - reg_list

在上述指令中,reg_list 是异常中断处理程序中使用的寄存器列表。标识符 ^ 指示将 SPSR_mode 寄存器内容复制到 CPSR 寄存器中,该指令只能在特权模式下使用

示例

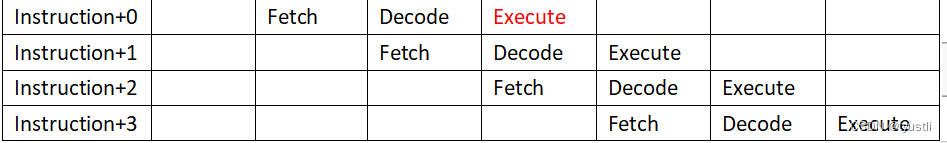

1、假设instruction+0 指令地址是非法的,发生了指令预取中止异常中断

2、此时 PC 的值还未更新指向 instruction+2

3、进入指令预取中止异常中断处理程序后,LR_mode = PC -4,所以此时 LR 指向 instruction+1

4、指令预取中止异常中断处理完成之后,程序需要返回到有问题的指令处,即 instruction+0 处执行,所以将此时的 LR_mode 寄存器的值 -4 赋给 PC。