DRV8301的使用

特点

- 电压6V到60V

- 1.7A栅极驱动电流,2.3A吸收电流

- 支持3.3V和5V接口

- 集成一个buck电源,可调节输出电压和开关频率,可对外提供1.5A电流

- 死区时间可调整、过流保护可调整、PVDD 和GVDD欠压锁定、GVDD过压锁定、过温提示/关机

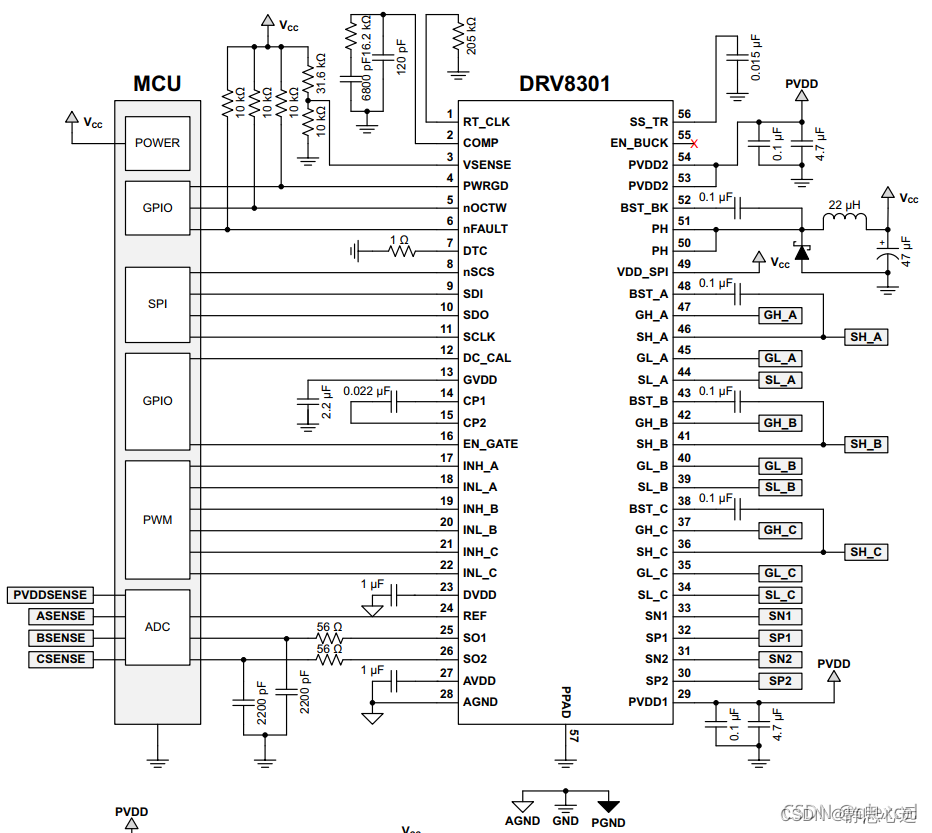

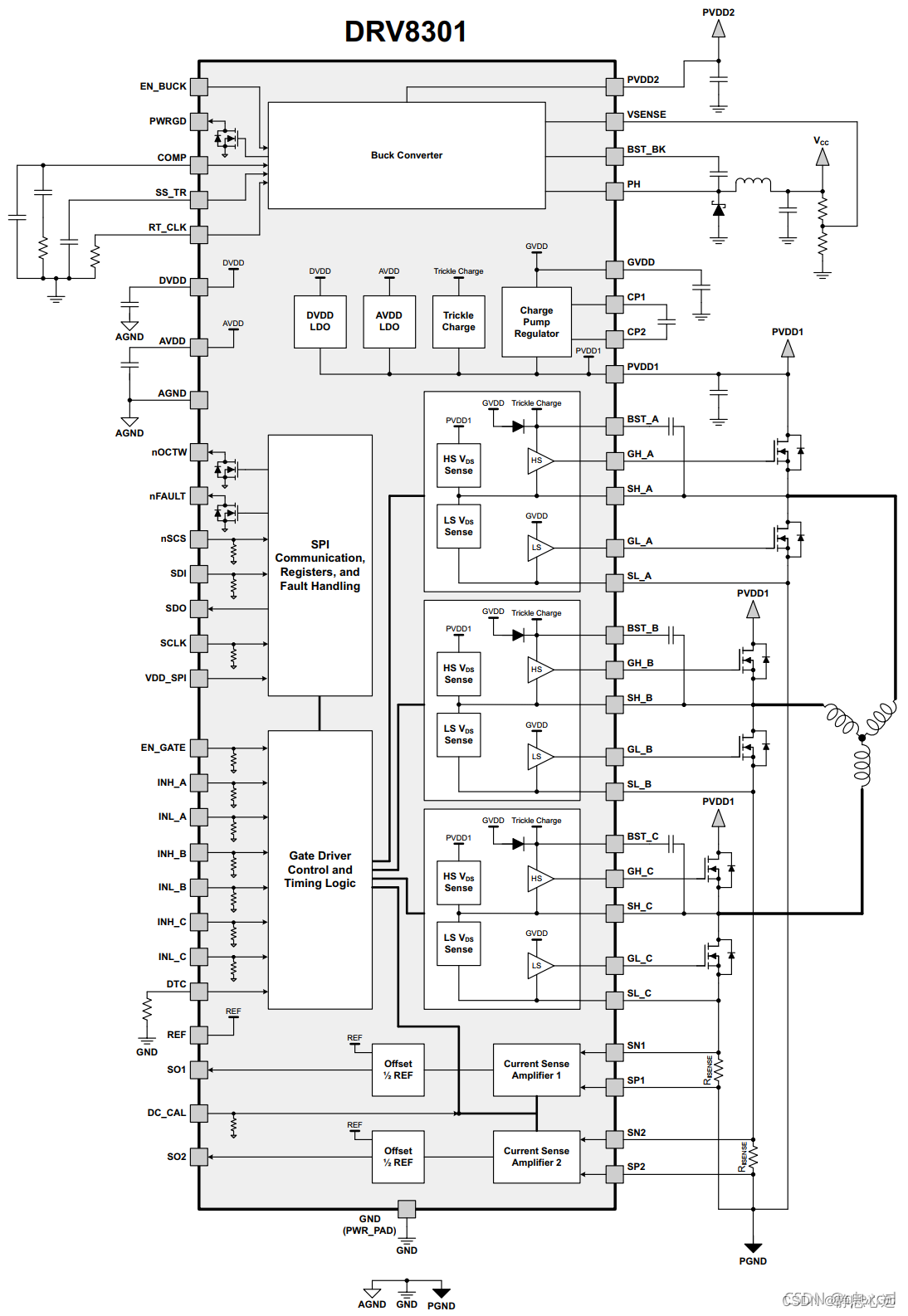

内部框图和引脚介绍

buck电源相关引脚

其他电源相关引脚

SPI通信和故障指示引脚

栅极驱动和PWM输入引脚

半桥电路相关引脚

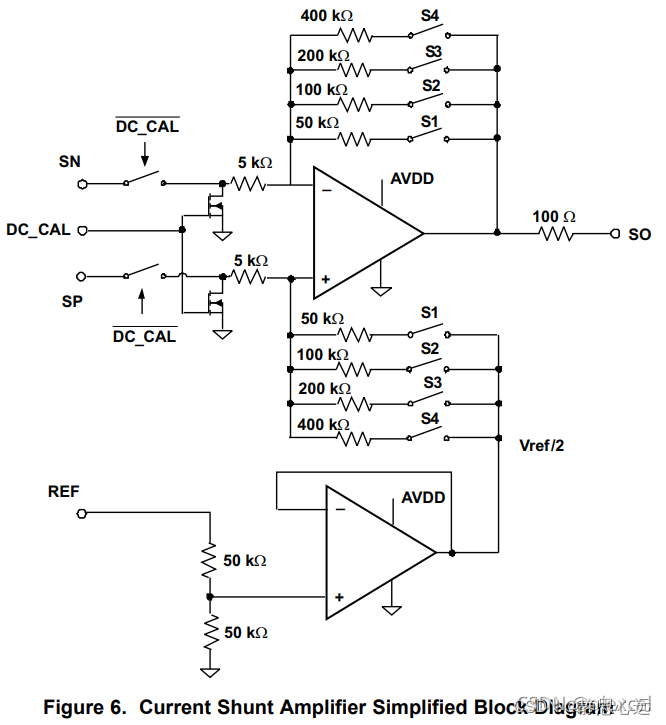

采样电流放大器:

DRV8301包括两个高性能的电流放大器,用于精确的电流测量。

电流放大器通过SPI寄存器有四个可编程增益设置,分别是10、20、40和80 V/V。

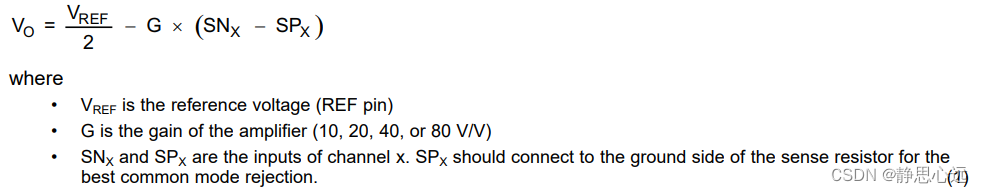

电流放大器提供高达3V的输出偏置,以支持双向电流检测。偏移量被设置为参考引脚(REF)上电压的一半。

为了减小直流偏置和漂移超温,提供了一种通过DC_CAL引脚或SPI寄存器进行校准的方法。当直流校准启用时,设备将短路电流放大器的输入并断开负载。直流校准可以在任何时候完成,甚至在MOSFET开关期间,因为负载是断开的。为了获得最好的结果,在无负载时,在开关OFF期间进行直流校准,以减少潜在的噪声对放大器的影响。

电流分流放大器的输出可计算为:

简化框图:

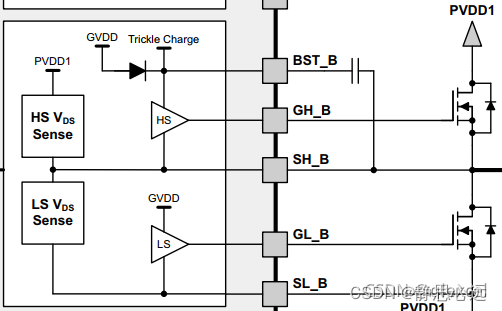

保护功能

由于MOS管有内阻,通过VDS = IDS × RDS(on)可以把电流值转换为电压值,再和通过SPI修改寄存器设置的过流值比较判断是否出发过流保护。高侧过流保护是采集PVDD1和SH_X之间的电压,低侧是采集SH_X和SL_X之间的电压,因此他们最好差分走线来消除PCB线阻差异。设置的过流值最好留20%的余量。

通过SPI寄存器可以设置四种不同的过流模式(OC_MODE)。OC状态位以锁存模式操作。当过流情况发生时,对应的OC状态位将锁定在DRV8301寄存器中,直到下一个SPI读取命令。在读取命令之后,OC状态位将从寄存器中清除,直到出现另一个过流状态。

1、限流模式

在限流模式下,设备在过流事件期间使用电流限制而不是设备关机。

在这种模式下,设备通过nOCTW引脚报告过流事件。nOCTW引脚将被保持低最大64µs周期(内部定时器)或直到下一个PWM周期。如果另一个过流事件由另一个MOSFET触发,在先前的过流事件期间,报告将继续另一个64µs周期(内部定时器将重新启动)或直到两个PWM信号周期。在检测到过流的场效应晶体管中,将置位相关的状态位。

在限流模式中有两个电流控制设置。这些是由SPI寄存器中的一位设置的,默认模式为CBC (cycle by cycle)。

- Cycle by Cycle mode (CBC):在CBC模式下,检测到过流的MOSFET将关闭,直到下一个PWM周期。

- Off-Time控制模式:在Off-Time模式下,当MOSFET检测到过流时,关闭时间为64µs(由内部定时器设置)。如果在另一个MOSFET中检测到过流,定时器将重置另一个64µs周期,两个MOSFET将在此期间被禁用。在此期间,特定MOSFET的正常运行可以通过相应的PWM周期恢复。

2. 锁存关闭模式

当过流事件发生时,高边和低边mosfet将在相应的半桥中被禁用。nFAULT引脚和nFAULT状态位将与检测过流的MOSFET的相关状态位一起被激活。OC状态位将锁定直到下一个SPI读取命令。nFAULT引脚和nFAULT状态位将锁定,直到通过GATE_RESET位接收到复位或快速的EN_GATE复位脉冲。

3.只报告模式

在此模式下,当发生过流事件时,不会采取保护动作。过流事件将通过nOCTW引脚(64 μ s脉冲)和SPI状态寄存器报告。外部单片机应根据自身的控制算法采取相应的行动。

4. OC禁用模式

设备将忽略且不报告所有过流检测。

欠压保护 (PVDD_UV and GVDD_UV)

当PVDD或GVDD低于其欠压阈值(PVDD_UV/GVDD_UV)时,DRV8301通过拉低GH_X、GL_X提供欠压保护。这将使外部mosfet处于高阻抗状态。当设备处于PVDD_UV时,它将不响应SPI命令,SPI寄存器将恢复到默认设置。

PVDD1从13µs到15µs的瞬时欠压限电,会导致DRV8301对外部输入无响应,直到满功率周期。瞬态条件是PVDD1大于PVDD_UV水平,然后PVDD1在13 ~ 15µs的特定时间内降至PVDD_UV水平以下。瞬变时间短于或长于13 ~ 15µs不会影响欠压保护的正常运行。可以在PVDD1上增加额外的大电容以减少欠压瞬变。

过压保护 (GVDD_OV)

如果GVDD电压超过GVDD_OV阈值,设备将关闭栅极驱动器和电荷泵,以防止与GVDD引脚或电荷泵相关的潜在问题(例如,外部GVDD电容或电荷泵电容短路)。故障是一个锁存故障,只能通过EN_GATE引脚上的复位转换来复位。

过温保护

实现了两级超温检测电路:

•1级:超温警报(OTW)

对于默认设置,OTW通过nOCTW引脚(过流和/或过温警告)报告。

OCTW引脚可以设置为仅通过SPI寄存器报告OTW或OCW。参见SPI寄存器部分。

•2级:门驱动器和电荷泵的超温锁存关闭(OTSD_GATE)

OTSD_GATE通过nFAULT引脚报告。这是一个闩锁关闭,所以门驱动器不会自动恢复,即使超温条件不再存在。EN_GATE复位或SPI (RESET_GATE)需要在温度低于预设值tOTSD_CLR后恢复门驱动器正常运行。

SPI操作仍然可用,在OTSD操作期间,只要PVDD1在定义的操作范围内,寄存器设置就会保留在设备中。

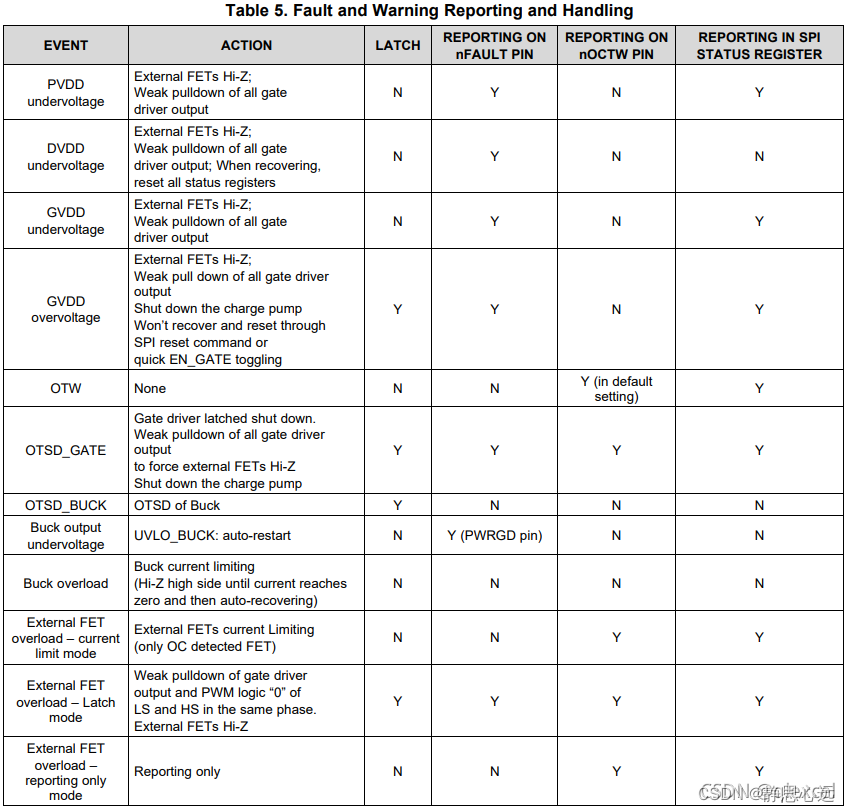

故障和保护的处理

nFAULT引脚指示何时发生关机事件,这些事件包括过流、过温、过压或欠压。注意,nFAULT是一个开漏信号。在开机启动过程中,当栅极驱动为PWM输入做好准备时,nFAULT将会拉高。

nOCTW引脚指示过流事件或过温事件何时发生。这些事件与关机无关。

表5提供了所有保护特性及其报告结构的摘要。

开关机顺序

在上电过程中,所有栅极驱动输出保持低电平。通过将EN_GATE从低状态切换到高状态,可以启动栅极驱动器和电流放大器的正常工作。如果没有错误存在,DRV8301准备接受PWM输入。只要PVDD在功能区域内,即使在栅极驱动禁用模式下,栅极驱动也始终对MOS进行控制。

从SDO到VDD_SPI有一个内部二极管,因此VDD_SPI需要一直被供电到与其他SPI设备相同的功率级别(如果有来自其他设备的SDO信号)。在SDO引脚上出现任何信号之前,VDD_SPI电源应该先通电,在完成所有SDO引脚上的通信之后再断电。

EN_GATE功能说明

EN_GATE low用于将栅极驱动器、电荷泵、电流放大器和内部稳压器模块置于低功耗模式,以节约能源。在此状态下SPI通信不被支持,SPI寄存器在完全EN_GATE重置后将恢复到它们的默认设置。只要PVDD仍然存在,器件将把MOSFET输出级设置为高阻抗模式。

当EN_GATE引脚从低到高时,它将经过一个上电序列,使能门驱动器、电流放大器、电荷泵、内部调节器等,并复位所有与门驱动器块相关的锁存故障。EN_GATE也将重置SPI表中的状态寄存器。当在错误事件之后切换EN_GATE时,所有锁存故障都可以重置,除非故障仍然存在。

当EN_GATE从高到低时,它会立即关闭门驱动块,因此门输出可以将外部fet置于高阻抗模式。然后,它将等待10µs,然后完全关闭其余的区块。一个快速的故障复位模式可以通过切换EN_GATE引脚非常短的时间(少于10µs)来实现。这将防止设备关闭其他功能块,如电荷泵和内部调节器,并带来更快和简单的故障恢复。SPI在这样一个快速的EN_GATE重置模式下仍然可以工作。要执行完全复位,EN_GATE应该被切换超过20µs。这允许所有功能模块完全关闭并达到已知状态。

10 - 20 μ s的EN_GATE复位脉冲(高→低→高)不应该应用于EN_GATE引脚。DRV8301有一个从快速复位模式到完全复位模式的过渡区域,这会导致设备对外部输入无响应,直到一个全功率循环。如果期望在EN_GATE引脚上出现此周期的重置脉冲,可以在引脚外部添加RC滤波器。

重置所有错误的另一种方法是使用SPI命令(RESET_GATE),它只重置门驱动模块和所有SPI状态寄存器,而不关闭其他功能块。

一个例外是重置GVDD_OV错误。快速的EN_GATE快速故障复位或SPI命令复位将不适用于GVDD_OV故障。重设GVDD_OV故障需要一个完整的EN_GATE,低电平保持时间大于20µs。TI强烈建议在GVDD_OV发生时检查系统和单板。

SPI通信

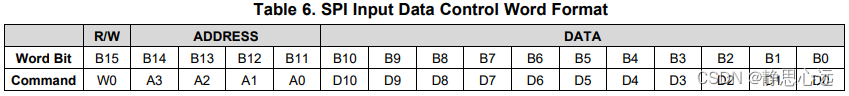

数据帧结构

The SDI input data word is 16 bits long and consists of:

• 1 read/write bit W [15],0表示写,1表示读。

• 4 address bits A [14:11]

• 11 data bits D [10:0]

应用

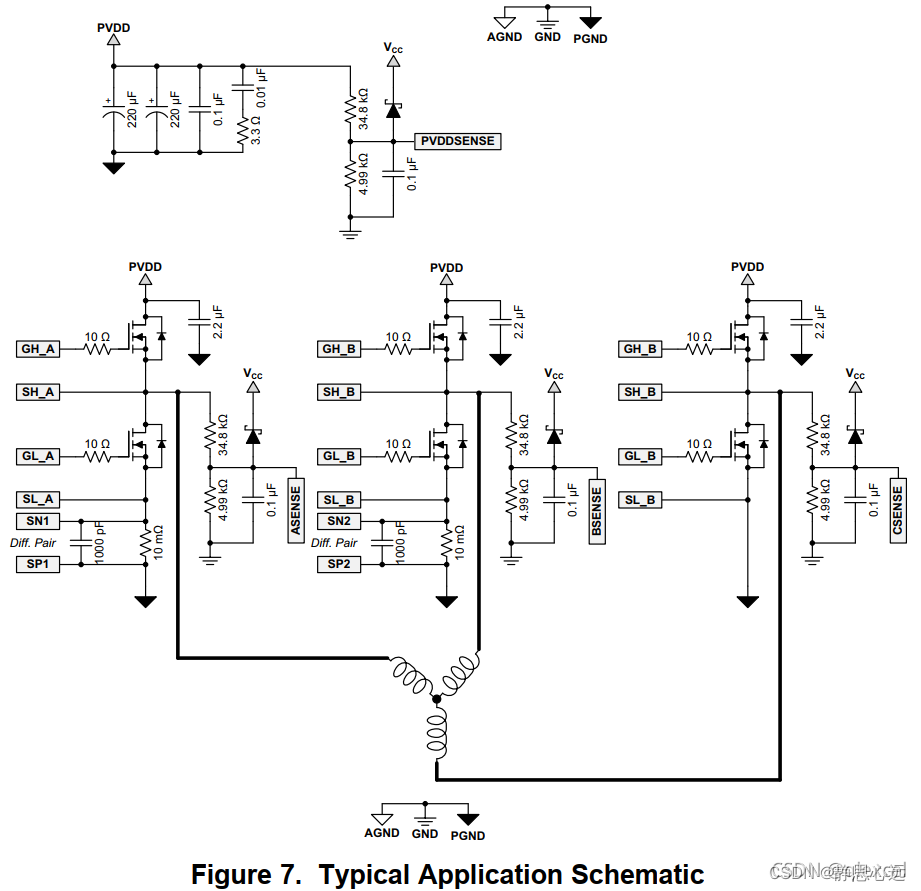

典型原理图如下: