本文目录

一、实验要求

- 使用两片62256扩充RAM空间为00000H-0FFFFH。

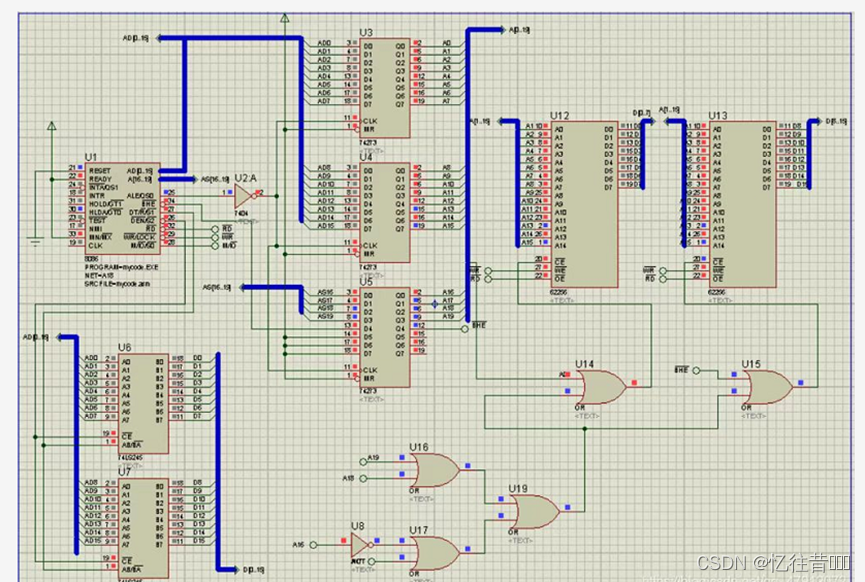

分析如下:

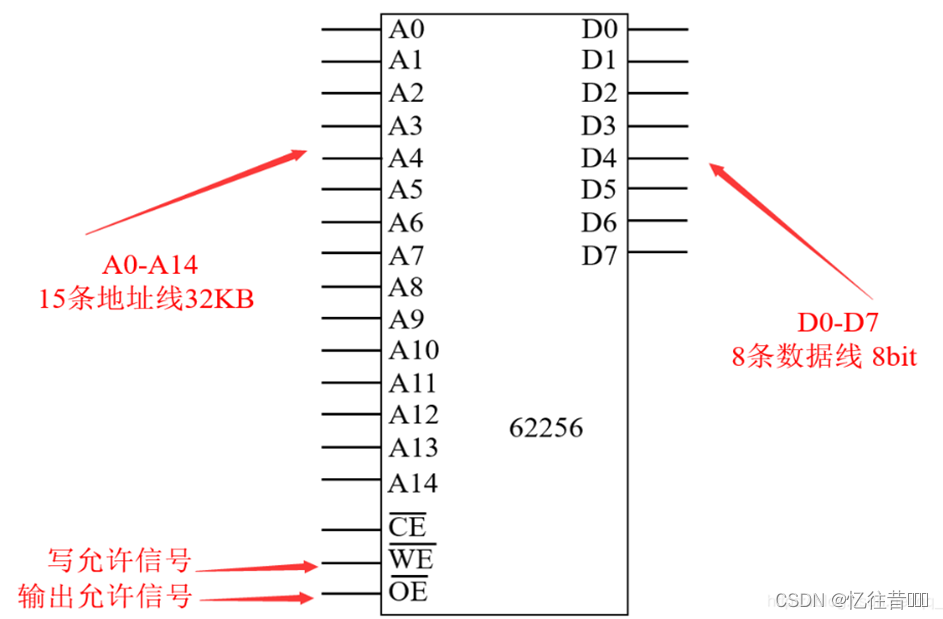

62256共有15根地址线 A0~A14,存储大小为32KB。8条双向数据线 D0~D7,共8bit。CE非为片选信号引线。WE非为写允许信号,当其值为 0 时,允许将数据写入芯片。OE非为输出允许信号,当其值为 0 时,允许该芯片将某单元的数据送到芯片外部的 D0~D7 上。芯片引脚图如下:

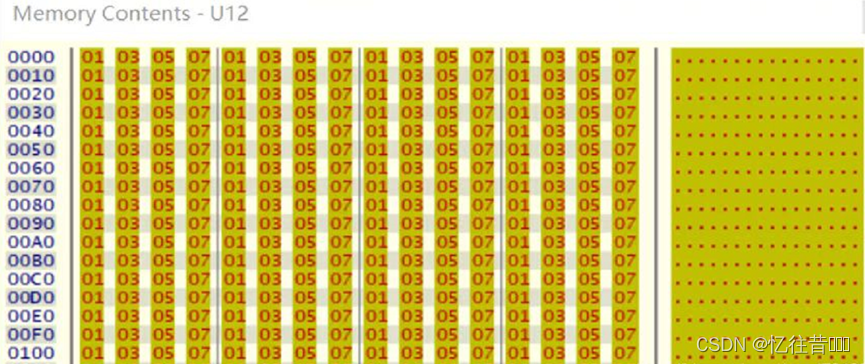

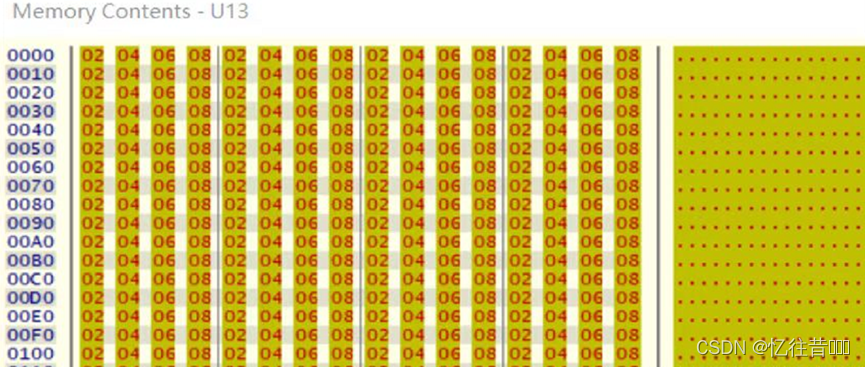

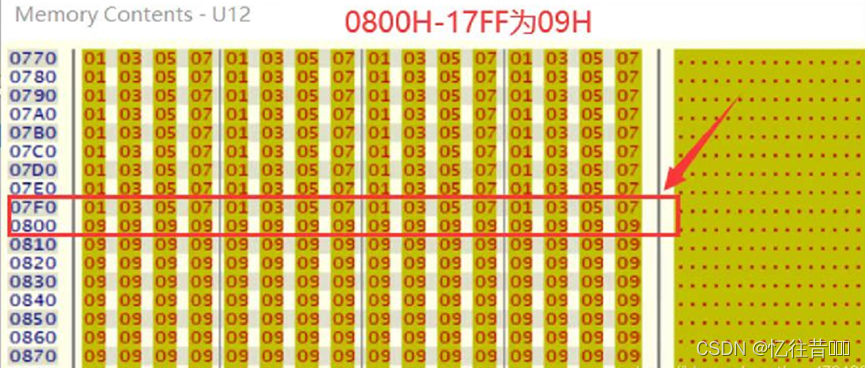

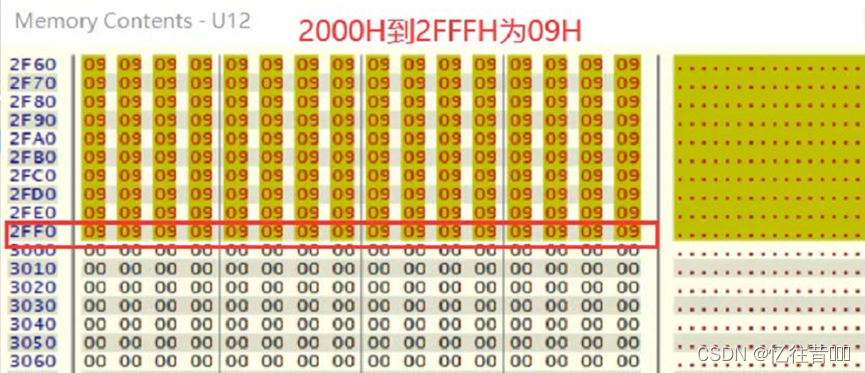

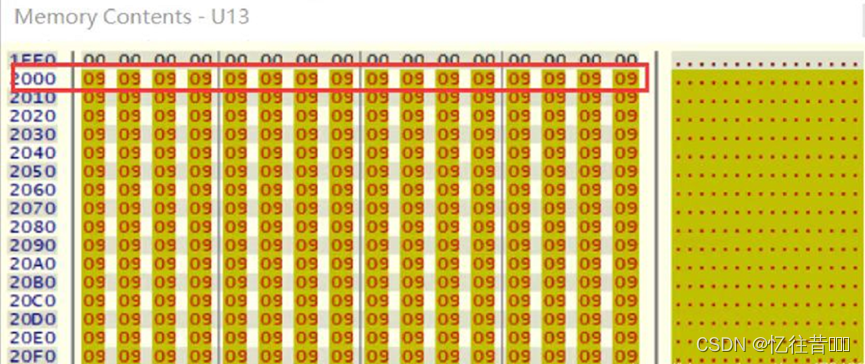

- 编制程序,将字符1~8循环写入00000H-00FFFH中,将9写入01000H-02FFFH中。将01000H-02FFFH中的内容搬移到04000H-05FFFH中。

原理分析:

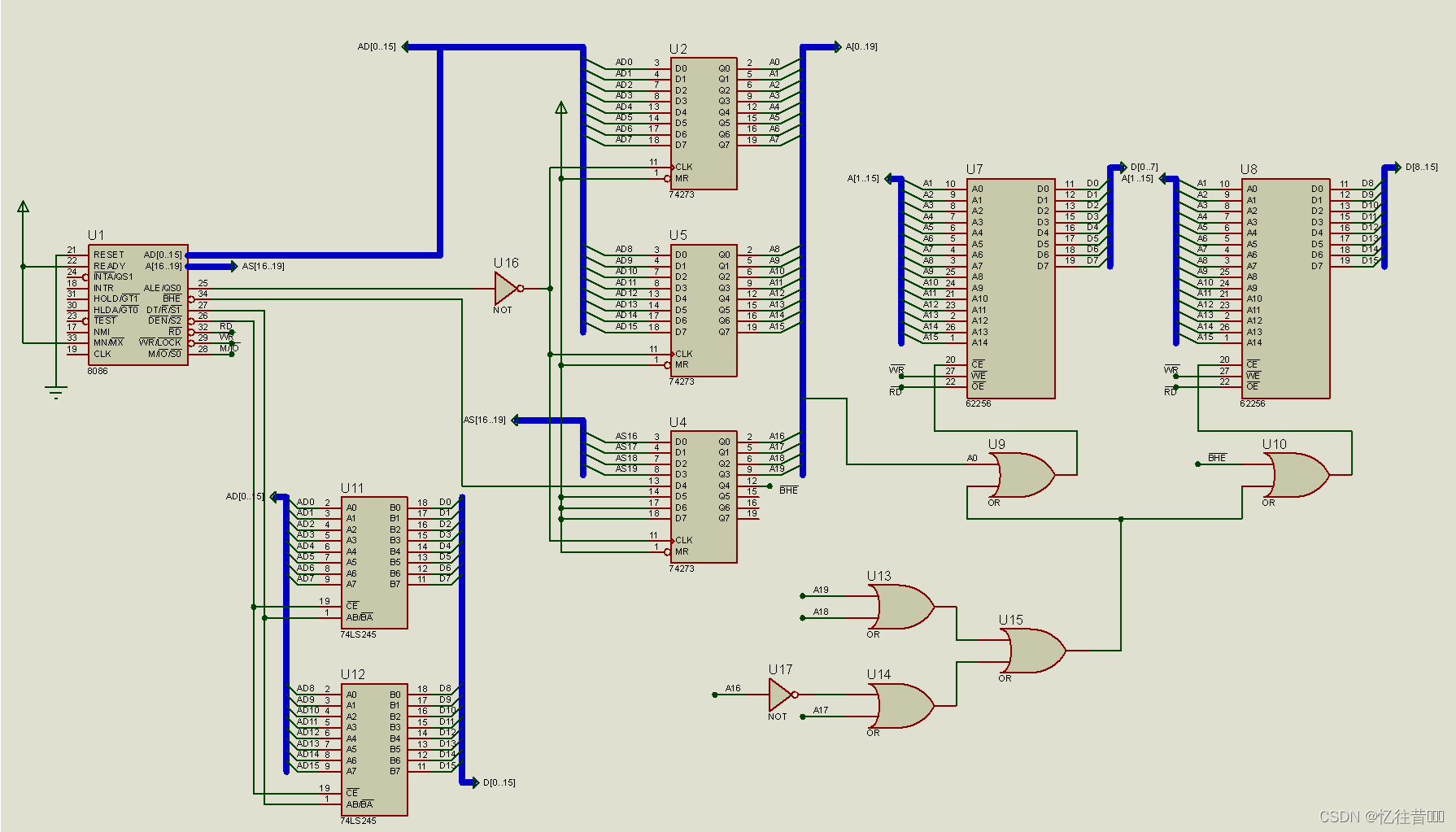

- 8086CPU数据地址线不能直接和外部芯片进行传送数据,故添加锁存器。

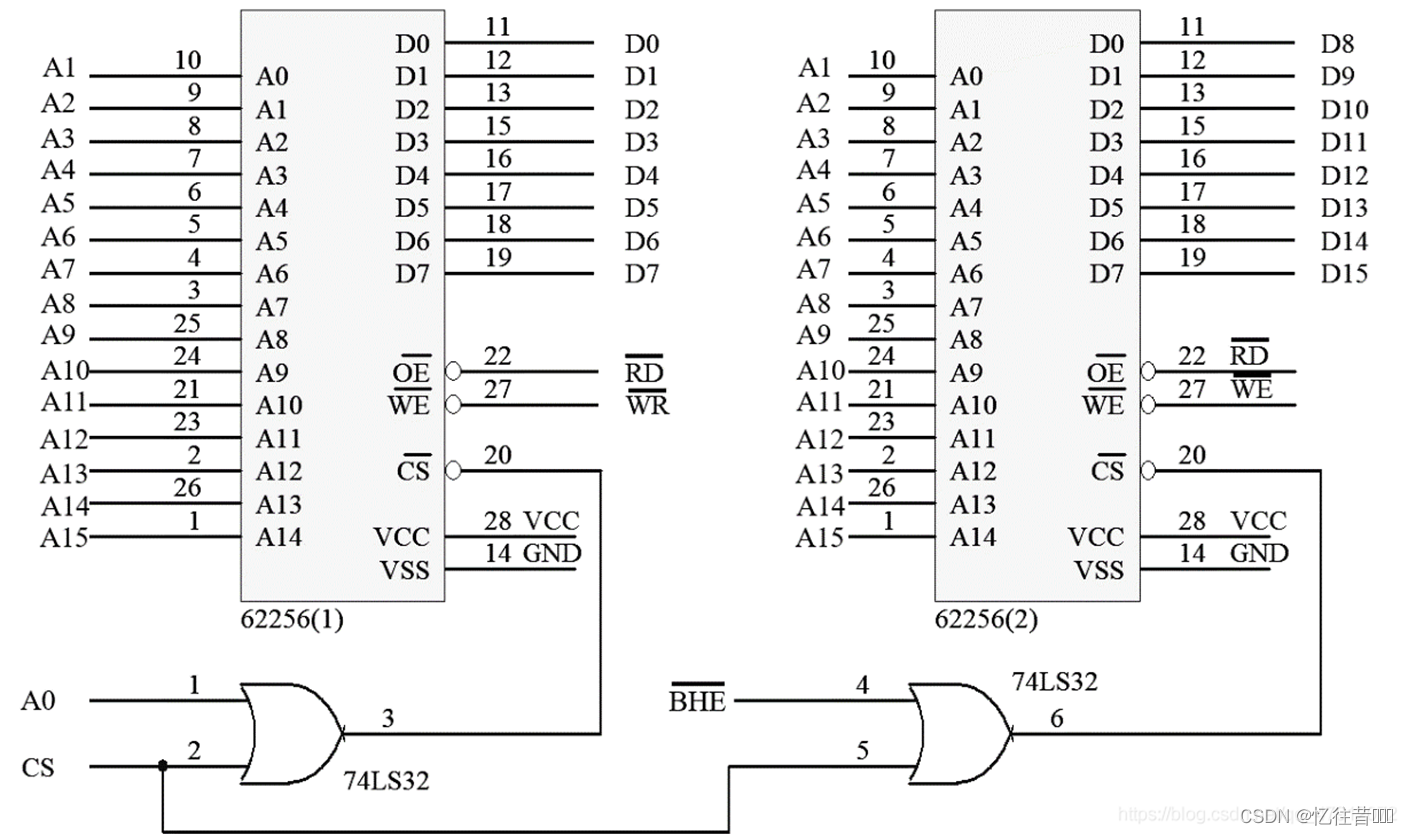

- 由于62256为32KB×8bit,而8086CPU共有16位数据线,故利用两个62256芯片进行位扩充,变成64KB×16bit。

- 位扩充功能由 BHE 和 A0 共同完成,偶地址的数据内容存放在一个芯片,奇地址的数据内容存放在另一个芯片。

- 10000H-1FFFFH高四位地址线 A19-A16 参与译码电路,要求其为0001时选中两个62256芯片中的一个。

锁存器:

- 74LS273 和 74LS373 均为地址锁存器。在最小模式下,8086CPU的20条地址线和1条 BHE 信号线用三片 74LS373 或 74LS273 锁存器形成,从而形成地址总线信号。

- 双向数据总线用2片 74LS245 形成。利用最小模式下8086CPU提供的 DEN 和 DT/R 分别控制2片 74LS245 的允许端和方向控制端,从而实现16位的双向数据总线 D0-D15。

二、实验目的

- 学习PROTEUS EDA仿真工具的使用方法;

- 学习8086最小系统中系统总线的形成方法;

- 掌握内存扩充方法和外围接口方法,正确设计译码电路,按照要求的地址实现存储器芯片的连接。

三、实验电路

四、实验代码及实验结果

(1)实验代码:

CODE SEGMENT

ASSUME CS:CODE

START:

MOV AX,1000H

MOV DS,AX ;设置数据段地址

MOV AL,1

MOV BX,0000H

MOV CX,1000H ;循环次数

MOV [BX],AL

JMP M1

;1~8循环写入10000H-10FFFH

ZERO:

MOV AL,1

M1:

MOV [BX],AL

INC BX

INC AL

CMP AL,8

JA ZERO

LOOP M1 ;循环次数CX的值

;将9写入11000H-12FFFH

MOV AL,09H

MOV CX,2000H

MOV BX,1000H ;偏移地址1000H

M2:

MOV [BX],AL

INC BX

LOOP M2

;将11000H-12FFFH内容移到14000H-15FFFH

MOV BX,1000H

MOV CX,2000H

TRANS:

MOV AL,[BX] ;读入

ADD BX,3000H

MOV [BX],AL

SUB BX,3000H

INC BX

LOOP TRANS

HLT

CODE ENDS

END START

(2)实验结果:

五、实验总结

通过本次实验,我对硬件电路设计有了初步了解,熟悉了Proteus的基本使用方法,掌握了如何将汇编程序载入到处理器中,从而完成了相应的功能。