1. 存储器的类型

1.1 按照存储介质来分类

- 半导体存储器: TTL, MOS 易失性

- 磁表面存储器: 磁头, 载磁体;

- 磁芯存储器: 硬磁材料, 环状元件

- 光盘存储器: 激光, 磁光材料;

1.2 按照存取方式分类

存取时间与物理地址无关: (随机访问)

-

随机存储器, 在程序的执行过程中, 可读 , 可写;

-

只读存储器, 在程序的执行过程中, 只读;

存取时间 与 物理地址有关 (串行访问)

-

顺序存取存储器, 磁带

-

直接存取存储器, 磁盘;

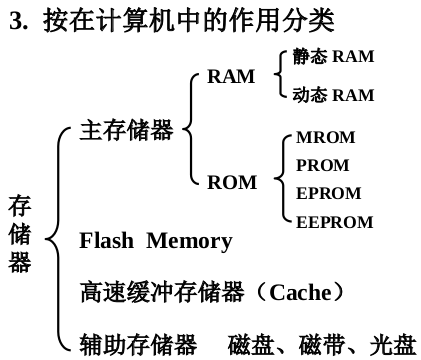

1.3 按照作用分类

存储器:

主存储器,

Flash Memory;

高速缓冲存储器 cache;

辅助存储器

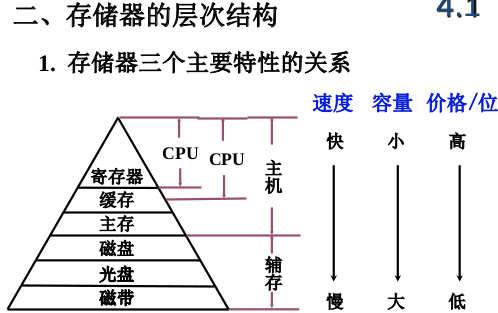

2. 存储器的层次结构

2.1 为什么要划分 存储层次

由于各种不同类型的存储器之间,

存取速度 和存储容量 相差较大,

即寄存器类型的 存储器, 速度最快, 但是容量却最小;

而主存级别的 存储器, 虽然容量增大,但是相对于CPU 中寄存器,速度却慢了很多;

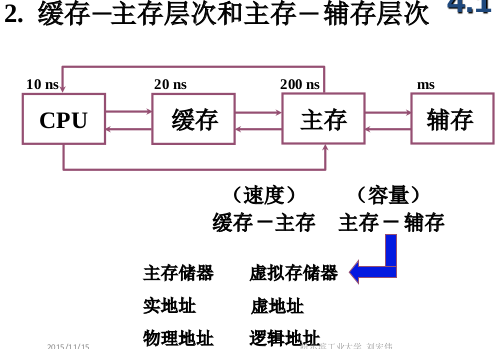

2.2 缓存和主存层次

缓存和 主存之间, 是为了 解决 速度差异较大的问题,

主存和辅存之间: 是为了解决 容量 的问题, 而主存 和辅存 之间采用了 虚拟地址映射的关系。

3. 主存储器

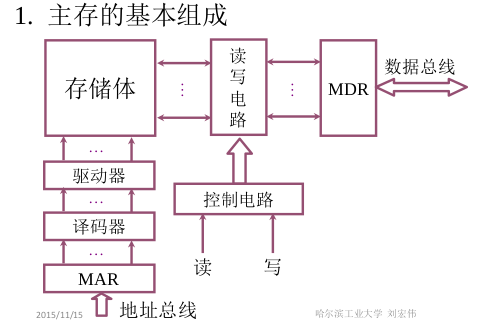

MDR: memory data register, 主存数据寄存器, MDR 用来保存要被写入地址单元 或者 从地址单元读入的 数据, 是一个数据寄存器,即该寄存器中存放的是数据

MAR: memory address register 主存地址寄存器, 地址寄存器, 该寄存器中 存放的是地址, MAR: 用来保存数据将要被传输到的 地址位置 或者 数据来源的地址位置;

之所以前面开头加上M: 代表的是Memory 主存,表示目的地是主存或者来源于主存。

即虽然当前的数据 保存在cpu中寄存器中, 但是该数据来源于 主存,或者将要存放到主存中;

数据将要存放到主存中的地址, 或者数据来源于主存中的地址;

3.1 主存储器的基本组成

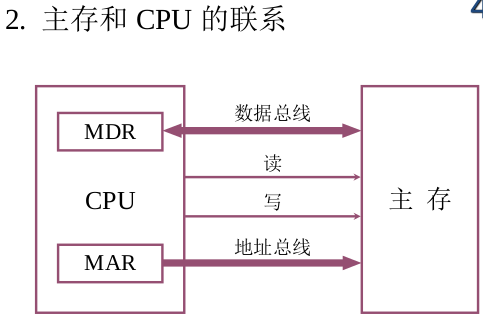

由地址总线负责: CPU 中的MAR(主存地址寄存器) 和主存之间进行通信;

数据总线负责: CPU 中的 MDR(主存数据寄存器) 和主存之间通信;

CPU中的控制电路, 控制读写 功能;

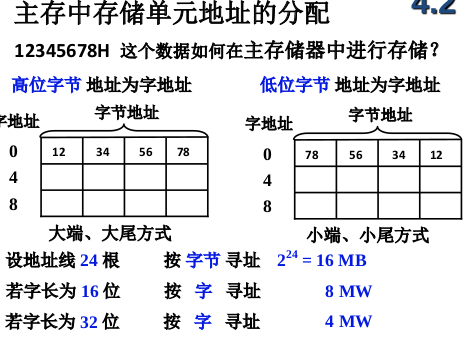

3.2 主存中存储单元地址的分配

一个十六进制数需要占用4位二进制,

8 个 十六进制数, 需要占用 32位 二进制;

保存在存储单元当中,

-

将高位字节的地址作为存储器的地址;

高位字节,12存放在低地址;

低位字节,78存放在高地址;

并且以高位字节,即12所在的地址,作为存储地址,即图中的字地址0,

-

将低位字节地址作为存储器的字地址;

低位字节,78存放在低地址,并且作为字地址

观察,两者都是以低地址作为字地址的;

3.3 主存的存储容量与存储速度

存储容量 主存 存放二进制代码的总位数

存储速度

- 存取时间 存储器的访问时间, 读出时间 写入时间

- 存取周期 连续两次独立的存储器操作, (读或写)所需的最小间隔时间 读周期 写周期

- 存储器的带宽: 位、秒

4 主存储器的 - 半导体芯片简介

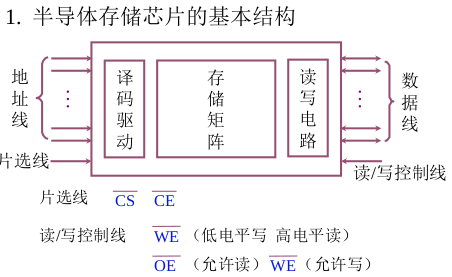

4.1 半导体存储芯片的基本结构

上方带有横线,表示低电平有效

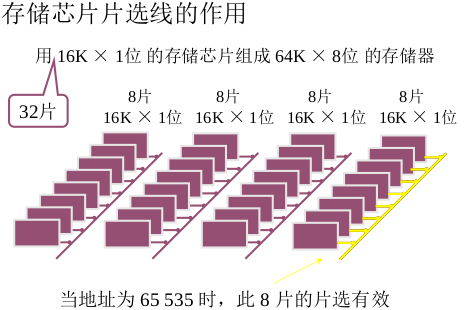

片选线:CS, CE

读写控制线: WE

用 8 个一位的16k 存储芯片, 组成一组8位的存储器,

每组为8位,总共需要4组;

4.2 半导体存储芯片的译码驱动方式:

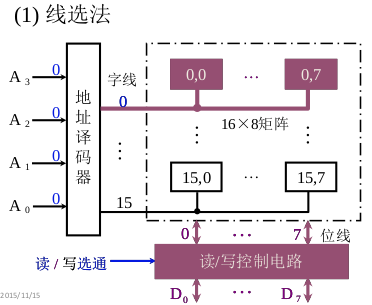

- 线选法:

通过地址译码器, 选出其中的一个地址线。

读写控制电路, 选择 读操作 还是 写 操作;

不足之处, 对存储容量较大的芯片, 线的密集程度较大。

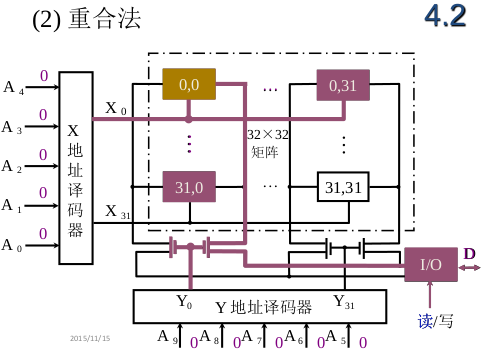

- 重合法

使用行,列地址译码器;

行,列地址分别进行译码;

分别,只能有一条线有效的;

5. 随机存取存储器RAM

内存便是RAM 构成,

- 保存0和1的原理是什么?

- 基本单元电路的构成是什么?

- 对单元电路如何读出和写入?

- 典型芯片的结构?

- 静态RAM芯片的如何进行读出和写入操作?

5.1 静态 RAM

- 保存0和1的原理是什么?

静态 RAM: 通过触发器保存0,1的状态;

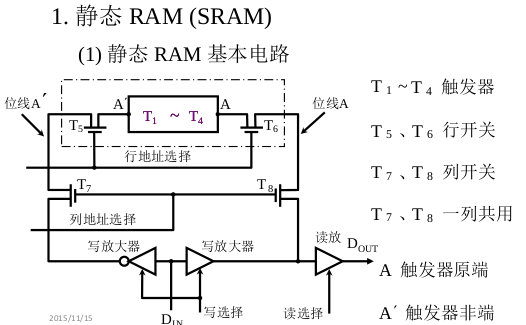

有T1~ T4 共4根管子构成触发器,双稳态触发器,用于保存数据;

多组 T1~ T4;

- 基本单元电路的构成是什么?

总共有6晶体管构成,

保存0,1的部分: 其中4个晶体管构成的触发器;

控制读写的部分: 两个晶体管:

这6个晶体管,组成了基本单元电路,在图中的虚线表示,将该虚线框的单元电路,重复多个,构成一列;

列开关: T7, T8一列公用; T7, T8 是这一列上所有的基本单元电路, 共有的控制开关, 用于控制 这一列,

A 触发器的原端, A' 触发器的非端;

存储器的读,写操作:

- T5, T6 两个晶体管决定对存储器进行读还是写,都是由行地址选择进行控制;

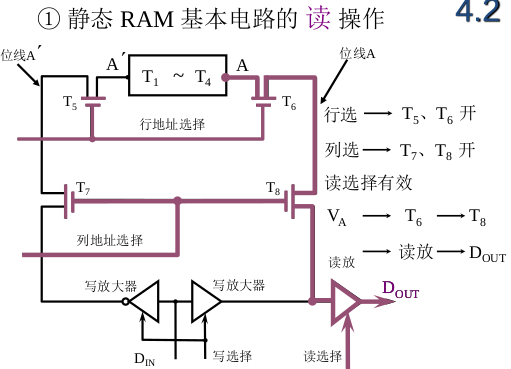

5.2 静态 RAM 的读写操作

读操作:

行选信号,控制T5, T6 打开;

列选信号,T7, T8 打开;

之后,读选择有效;

存放在A中的数据,

通过T6晶体管,送到位线上去,

同时T8导通,输出到读放大器中;

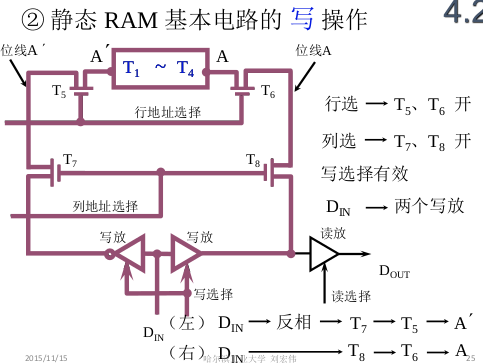

写操作,

选择写信号,

通过原信号与原信号取反,输入到A, A'

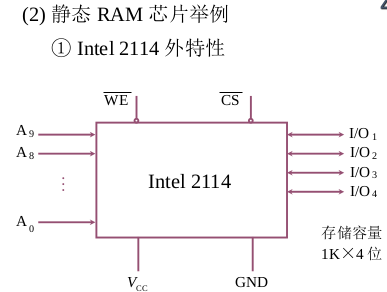

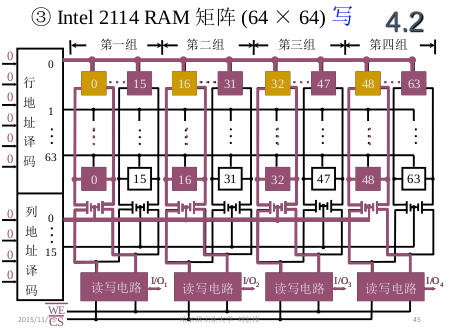

静态RAM芯片举例

we: 带横线, 表示低电平, 表示进行写操作;

通过选择行地址译码器, 选择其中的一行;

列地址译码器, 选择其中的一列;

5.3 动态RAM 随机存储器

-

保存0和1的原理是什么?

使用电容元器件保存电荷, 有电荷表示1,

电容当中没有电荷, 便表示是0; -

基本单元电路的构成是什么?

基本单元有三个晶体管和电容构成。

电荷保存在图中电容 C g C_g Cg 中,

有三个晶体管的电路;

和单个管的电路;

-

对单元电路如何读出和写入?

读选择线, 控制T2晶体管;

写选择线, 控制T3晶体管; -

典型芯片的结构?

-

动态 RAM 芯片的如何进行读出和写入操作

预充电信号有效, vdd 通过T4给读数据线充电,

使读数据线成为高电平,

如果读操作, 读选择线有效, T2 管子进行导通。

若Cg中保存的是0, 则T1的栅极是低电平;

读出与原存信息相反;

写入与输入信息相同

- 动态RAM 为什么要刷新, 刷新方法?

刷新放大器, 动态RAM 使用的是电容存储电荷的原理来保存信息的, 电容会漏电

由于电容会漏电, 经过一段时间后, 电容上的信号会消失,采用刷新放大器,对电容中保存的信息进行重写;

5.3.1 三管动态RAM 芯片 举例

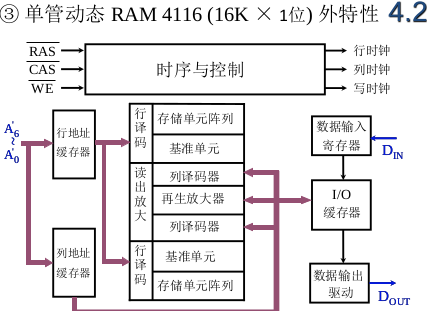

5.3.2 单管动态RAM 的外特性

4116 动态RAM芯片中的读放大器的工作原理是一个撬撬板电路,

其左右两侧的电平相反。

读操作:

在读放大器的左侧这些行中,电容有电表示0, 电容没有电代表1,

在读放大器的右侧侧这些行中,电容有电表示1, 电容没有电代表0;

写操作:

如果写入的数据是1, 则经过读放大器后, 读放大器的另一端中保存的电荷是0;

此时,读出和写入的信息是一致的;

5.4 动态RAM的刷新

动态RAM是使用,电容存储电荷的方式来保存信息的,

电容很小,容易漏电;

在一段时间中,如果不对电容中的信息再生的话, 电容中保存的信息就会丢失;

所以需要对动态电容进行刷新, 刷新的时候只和行地址有关系, 刷新一行中所有的基本单元电路;

两个毫秒之内,对动态RAM中所有的行进行刷新;

集中式刷新,在刷新时间周期内, cpu 和io 设备只能进行等待;

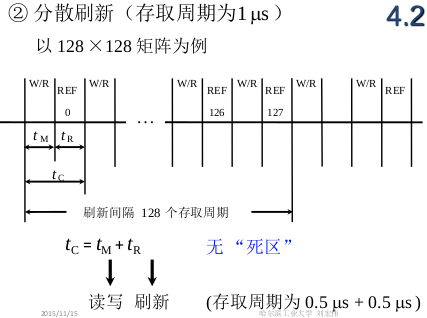

分散刷新( 读取周期)

无 死区, 过度刷新, 将读写周期加长,导致芯片性能下降;

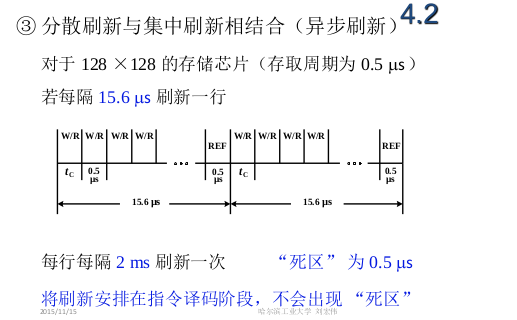

分散式刷新与集中式刷新(异步刷新);

将刷新周期安排在 指令译码的时间段内;

6. 静态RAM和 动态RAM 的比较

| 动态RAM | 静态RAM | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 低,可以由一个晶体管构成 | 高,每个基本单元电路6个晶体管 |

| 芯片引脚 | 少, 行,列地址可以分别进行传送, 地址线条数减少一半 | 多 |

| 功耗 | 低,对电容进行充放电 | 高, 双稳态触发器,3个管子一直漏电, |

| 价格 | 结构简单,价格低 | 结构负责, 价格高 |

| 速度 | 读写时, 对电容充放电, 速度慢 | 触发器方式,速度较快 |

| 刷新 | 有 | 无 |