为什么需要视频编码

举个例子,如果摄像头输出分辨率为400*400的图像,那每一帧的大小就是400*400*8*3=3840000bit,折算下来一帧就需要468KB

一般情况下帧数都是30fps,那么一秒就要占用约13M的空间,不经压缩想保存视频所需要的存储空间就无法估量了,因为视频编码是必须的

硬件编码与软件编码

软件编码应用广泛,但是总体来说,在编码效率上,软件编码是无法比拟硬件编码的。因为视频编码算法十分复杂,需要并行计算的地方很多,CPU很难承受;而FPGA可以很好地做好并行计算,硬件编码就开始被广泛研究。

然而硬件编码所需要的Logic资源比较多,对LUT(查找表)的需求较高,低端的FPGA板子无法做这一个工作

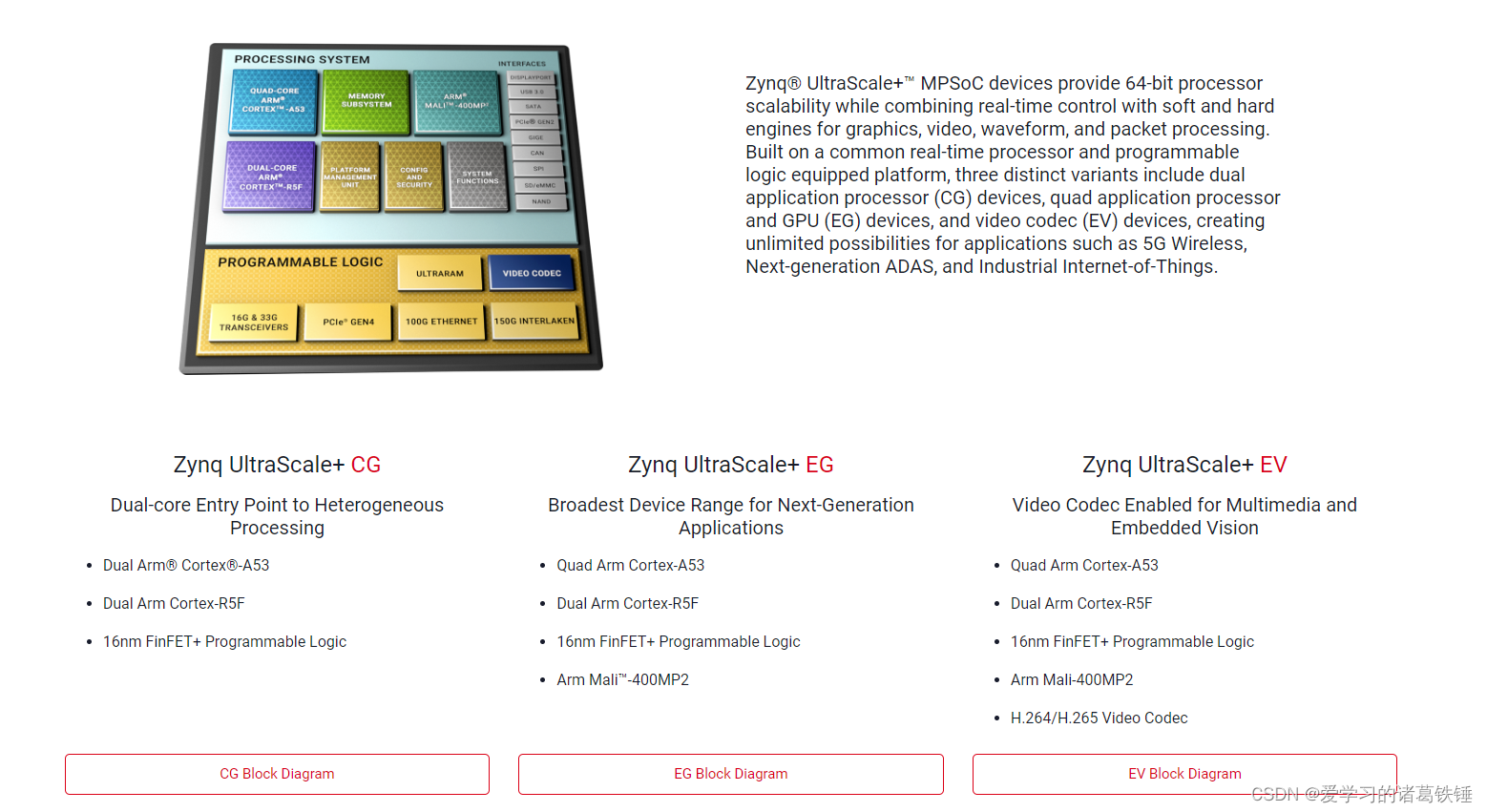

Xilinx也推出了 Zynq UltraScale+ EV 这一款自带Codec的产品,想必能很好地解决这一问题,不过它的价格也相对较高了

H.264编解码原理浅析

贴一个链接:H.264编解码原理浅析

不得不说其中涉及的算法很是复杂,如果用Verilog去实现H.264硬件编码的话,需要消耗的精力和时间也无法估量了

H.264/H.265开源项目

贴一个链接: 优秀的 Verilog/FPGA开源项目介绍(十)- H.264和H.265

其中复旦大学ASIC中发布的项目(官方地址:http://www.openasic.org/)值得学习,但是用来商业化用来做产品还是需要做很多工作的

小小总结

硬件编码无论是H.264还H.265亦或是MJPEG编码,所需要消耗的FPGA的Logic资源是庞大的

笔者在ZYNQ7010和ZYNQ7020上尝试综合过上面提到的开源项目,发现需要的LUT和DRAM资源很多,这两款产品难以支持

同时也看过一些论文,其中 李斌杰在论文《基于ZYNQ的高清视频压缩平台设计与实现》中使用了ZYNQ7100这款资源丰富的板子上完成了设计基于H.264的视频压缩平台,但是没有做UI界面去显示

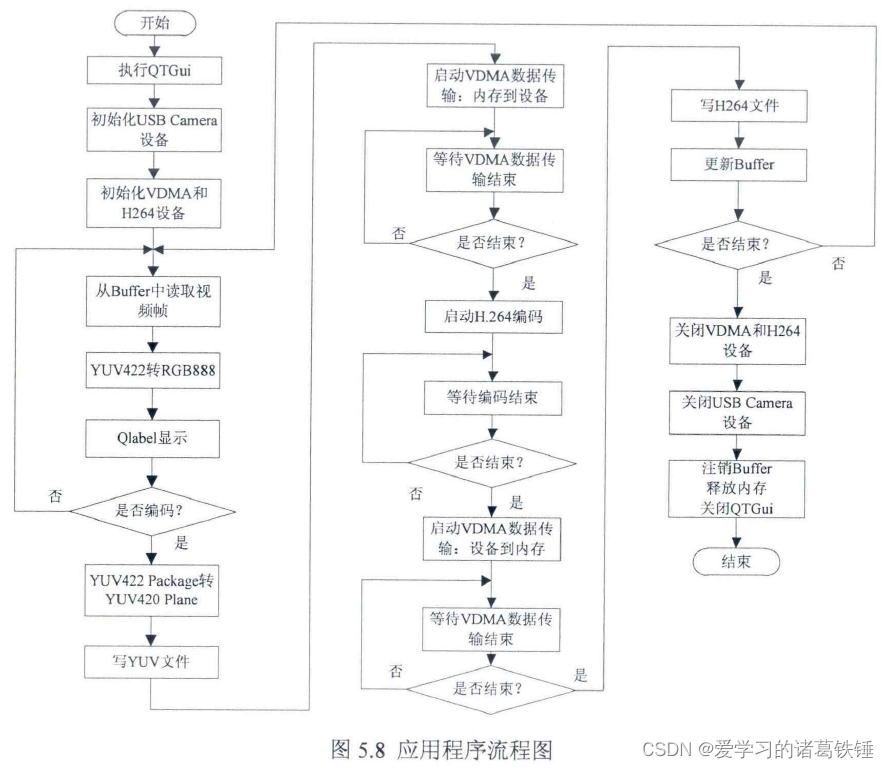

相比之下,荣超群的《基于FPGA的H.264编码系统设计与实现》就设计了界面去显示视频,采用的策略是采集显示结束之后再进行编码,设计的系统的流程图如下

整体来说还有很多路要走,慢慢学吧