文章目录

I2S 协议详解

信号线定义

各个信号线的功能及描述见下表

| 信号线 | 描述 |

|---|---|

| MCLK | 主时钟,也叫系统时钟(Sys Clock),为了使系统间能够更好的同步,MCLK的频率=256fs 或384fs(fs 指采样频率) |

| SCLK | 串行时钟,也叫位时钟(BCLK),对应数字⾳频的每⼀位数据,SCLK 都有⼀个脉冲。SCLK 的频率=2x采样频率x采样位数 |

| LRCLK | 帧时钟,⽤于切换左右声道的数据。LRCLK(Left/Right CLOCK),LRCLK 的频率 = 采样频率 |

| SDATAI | 串行数据输入,用二进制补码表示的音频数据输入信号(MSB->LSB:数据由高位到低位依次传输) |

| SDATAO | 串行数据输出,用二进制补码表示的音频数据输出信号(MSB->LSB:数据由高位到低位依次传输) |

根据 data 相对于 LRCLK 与 BCLK 位置的不同,I2S 协议一般分为 5 种不同的模式,发送端和接收端必须使用相同的数据格式。

- 飞利浦(I2S)标准模式

- 左(MSB)对齐标准模式

- 右(LSB)对齐标准模式

- PCM/DSP 模式

- PCM/DSP 模式 A

- PCM/DSP 模式 B

相关术语

- MSB:表示数据的最高 BIT 位

- LSB:表示数据的最低 BIT 位

- PCM:Pulse Code Modulation - 脉冲编码调制

- TDM:Time Division Multiplexing - 时分复用

- slot:槽 - 是指某个通道的一帧数据

- slot_num:槽的个数

- slot_width:一帧数据的位数

位宽与位深

位宽

根据上面公式 SCLK 的频率=2x采样频率x位宽,可以得到 I2S 的数据位宽

位宽 = S C L K / B C L K 2 L R C L K = S C L K / B C L K 2 f s 位宽 = {\frac{SCLK/BCLK}{ {2} {LRCLK}}} = {\frac{SCLK/BCLK}{2fs}} 位宽=2LRCLKSCLK/BCLK=2fsSCLK/BCLK

位深

表示音频数据量化后的精度

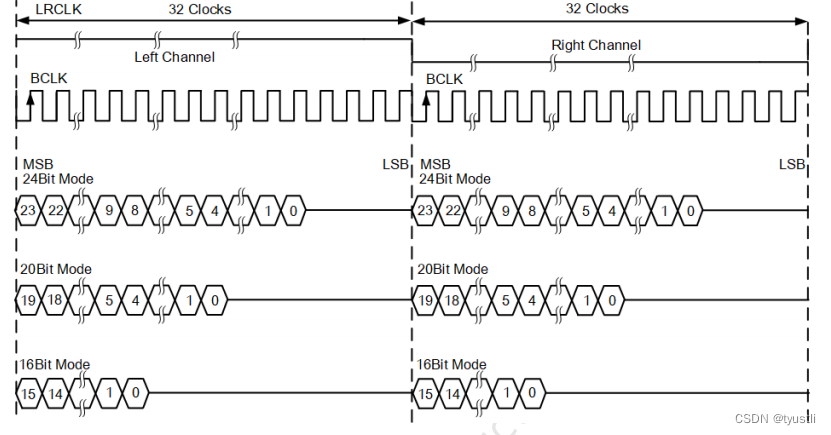

例如,在下文出现的图中,位宽均为 32 位,位深可以设置为 16/20/24 等

需要注意在 I2S/LJ/RJ 模式中,位宽/位深 是由 master 决定的

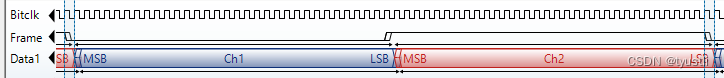

32位位宽,32位位深

- I2S mode

- MSB first

32位位宽 word width,32位位深 bit depth- 2通道

时序如下

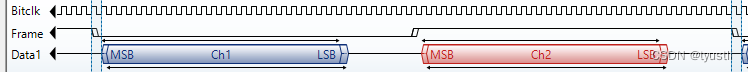

32位位宽,24位位深

- I2S mode

- MSB first

32位位宽 word width,24位位深 bit depth- 2通道

时序如下

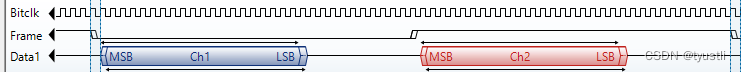

32位位宽,20位位深

- I2S mode

- MSB first

32位位宽 word width,20位位深 bit depth- 2通道

时序如下

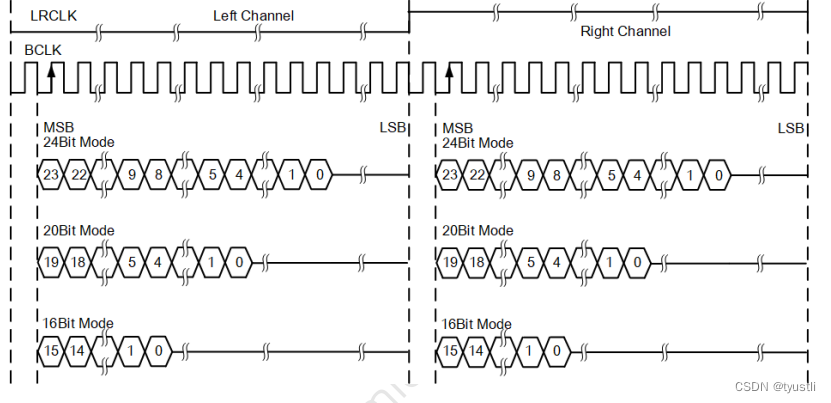

32位位宽,16位位深

- I2S mode

- MSB first

32位位宽 word width,16位位深 bit depth- 2 通道

时序如下

I2S format

飞利浦 (I2S) 标准模式

- 数据在跟随 LRCLK 传输的 BCLK 的第二个上升沿时传输 MSB,其他位一直到 LSB 按顺序传

- 传输依赖于字长、BCLK 频率和采样率(BCLK=Fs x 声道数 x 采样位数)

- 在每个采样的 LSB 和下一个采样的 MSB 之间都应该有未用的 BCLK 周期

- LRCLK 为 0 传输左声道数据,LRCLK 为 1 传输右声道数据

飞利浦标准模式的 I2S 传输协议如下所示:

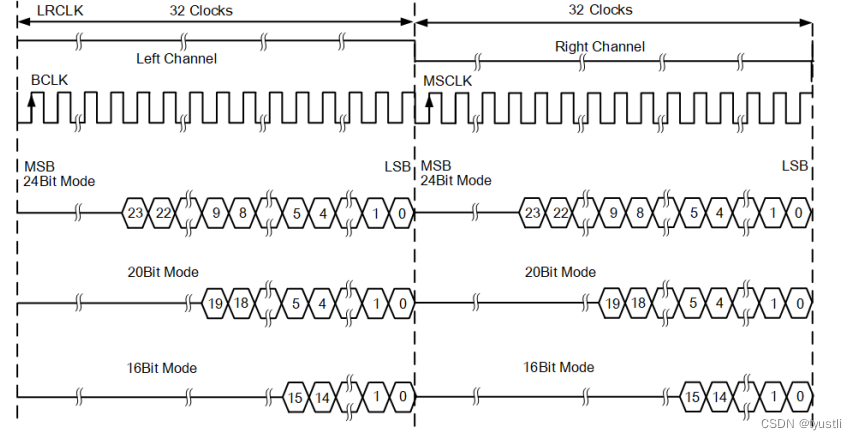

I2S left

I2S 左对齐标准

- 标准左对齐格式的数据的 MSB 没有相对于 BCLK 延迟一个时钟。左对齐格式的左右声道数据的 MSB 在 LRCLK 边沿变化后 BCLK 的第一个上升沿有效

- LRCLK 为 1 传输左声道数据,LRCLK 为 0 传输右声道数据,这也飞利浦标准刚好相反

- 左对齐格式的优点在于,由于在 LRCLK 变化后的第一个 BCLK 上升沿就开始采样,它不需要关心左右声道数据的字长

- 从波形可以看出 I2S 模式属于左对齐模式中的一种特例,由左对齐模式数据延迟一个 BCLK 时钟周期变化而来。

I2S right

I2S 右对齐标准

- 也叫日本格式,sony 格式。相比于标准左对齐格式,标准右对齐的不足在于接收设备必须事先知道待传数据的字长

- 声⾳数据 LSB 传输完成的同时,LRCLK 完成第⼆次翻转(刚好是 LSB 和 LRCLK 是右对⻬的,所以称为右对⻬标准)

- LRCLK 为 1 传输左声道数据,LRCLK 为 0 传输右声道数据

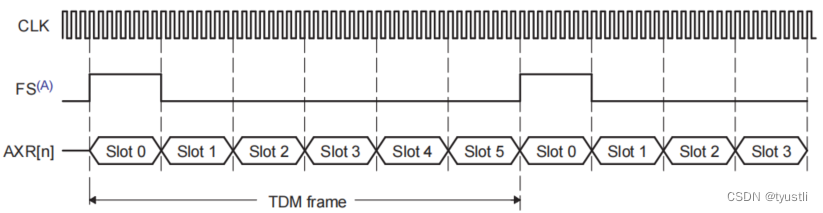

PCM/DSP format

PCM 接口分为两种常用操作模式:DSP A mode 和 DSP B mode,统称为 DSP mode

基于 DSP mode,PCM 接口可以配置支持 TDM(Time Division Multiplexing)数据传输。可以支持传输多个声道的数据,允许多个设备同时使用总线。由于没有统一的标准,不同厂商在 TDM 实现的时序上略有差异。

- 在 PCM 模式中 LRCLK 的高低不再代表不同通道的数据,它是一个比特宽的脉冲,标志着一帧的开始

- PCM 只有⼀个起始信号,并且对数据进行对齐,使左通道数据紧跟着右通道数据。为剩余的位进行零填充

- 数据和帧时钟可以配置为在 BCLK 的上升沿或下降沿有效

PCM 和 I2S 的区别于数据相对于帧时钟(FSYNC/WS)的位置、时钟的极性和帧的长度。其实,I2S 上传输的也是 PCM 类型的数据,因此可以说 I2S 是 PCM 接口的特例。

相比于 I2 S接口,PCM 接口应用更加灵活。通过时分复用(TDM, Time Division Multiplexing)方式,PCM 接口支持同时传输多达 N 个(N>8)声道的数据,减少了管脚数目

TDM不像I2S有统一的标准,不同的IC厂商在应用TDM时可能略有差异,这些差异表现在时钟的极性、声道配置的触发条件和对闲置声道的处理等

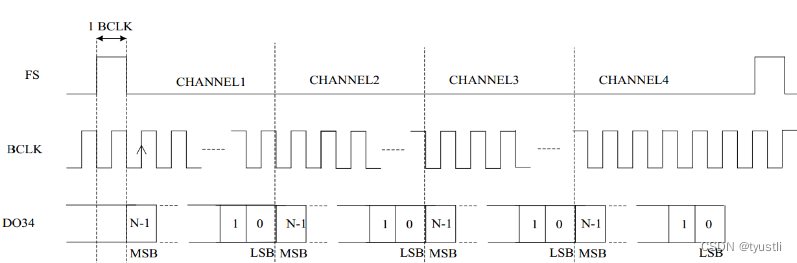

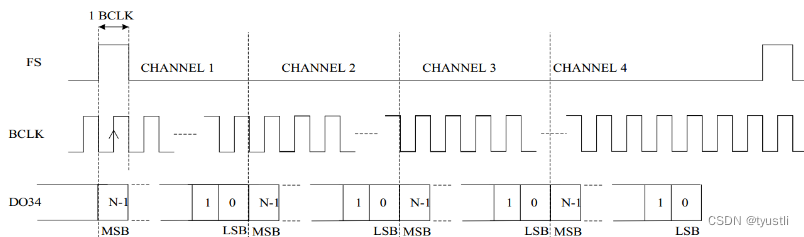

PCM/DSP format A

- DSP A:FSYNC 有效后,数据在 BCLK 的第 2 个上升沿(下降沿)有效(one bit clock delay)

- TDM mode

- MSB first

32位位宽 word width,16位位深 bit depth- 4 通道

时序如下

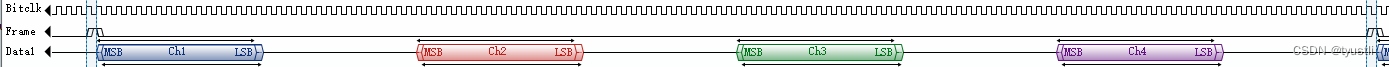

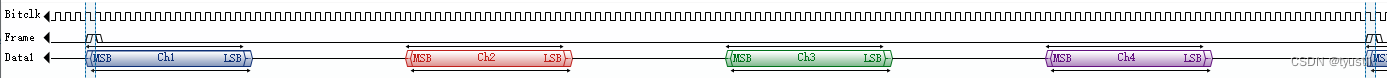

PCM/DSP format B

- DSP B: FSYNC 有效后,数据在 BCLK 的第 1 个上升沿(下降沿)有效(no delay)

- TDM mode

- MSB first

32位位宽 word width,16位位深 bit depth- 4 通道

时序如下

在DSP B 模式内,数据延迟一个bit clock 周期有效就是 DSP A 模式。可见 A 是 B 的特例。

不同厂商对 Mode A 和 Mode B 定义可能有所差别,PCM 帧同步模式大致可以分为两种

- 长帧模式 - long frame sync

- FSYNC 脉冲宽度等于 1 个 slot 的长度,slot 在 TDM 中表示的是传输单个声道所占用的位数。注意,slot 的位数并不一定等于音频的量化深度。比如 slot 可能为 32 bit,其中包括 24 bit 有效数据位(Audio Word) + 8 bit 零填充(Zero Padding)

- 短帧模式 - short frame sync

- FSYNC 脉冲宽度等于 1 个 BCLK 周期长度