I2S协议

概念

I2S(Inter—IC Sound)总线, 又称集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。

特点

1. 支持半双工\全双工

2. 支持主从模式

3. I2S的变体也支持多通道的时分复用,因此可以支持多声道

信号线

1. 主时钟MCLK,也是以上两个时钟的参考时钟,一个系统应该使用同一的MCLK以保证时钟同步要求。常见频率256fs或384fs。有时为了使系统间能够更好地同步,当I2S配置为主模式(并且SPI_I2SPR寄存器中的MCKOE位置1)时,使用此时钟,该时钟输出频率 256×fs,fs即音频信号采样频率(frequency of sample)

2. 串行时钟SCLK,也叫位时钟BCLK,对应数字音频的每一位数据,该时钟都有一个脉冲。

sclk = (slot_num * slot_bit + 2) * bclk //slot的概念后面补充

3. 帧时钟LRCK(也称WS),用于切换左右声道的数据。LRCK为1表示传输右声道数据,为0则是左声道。

lrck = fs

4. 输入、输出引脚DIN、DOUT,就是用二进制补码表示的音频数据

IIS包括两个声道(Left/Right)的数据,在主设备发出声道选择/字选择(WS)控制下进行左右声道数据切换。通过增加IIS接口的数目或其它IIS设备可以实现多声道(Multi-Channels)应用

操作模式

1. 标准模式 Phillips Standard

IIS模式是标准左对齐格式再延迟一个时钟位变化来的。

左右通道的数据MSB均是在WS变化后第二个SCK/BCLK上升沿有效。使用WCLK/LRCLK信号来指示当前正在发送的数据所属的声道,为0时表示左声道数据。LRCLK信号从当前声道数据的第一个位(MSB)之前的一个时钟开始有效。LRCLK信号在BCLK的下降沿变化。发送方在时钟信号BCLK的下降沿改变数据,接收方在时钟信号BCLK的上升沿读取数据。LRCLK频率等于采样频率fs,一个LRCLK周期(1/fs)包括发送左声道和右声道数据。

对于这种标准I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在WCLK/LRCK变化(也就是一帧开始)后的第2个BCLK/SCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

时序图如下:

2. 左对齐模式 Left Justified Standard

标准左对齐格式的数据的MSB没有相对于BCLK延迟一个时钟。左对齐格式的左右声道数据的MSB在WS边沿变化后SCK/BCLK的第一个上升沿有效。左对齐格式的优点在于,由于在WS变化后的第一个SCK上升沿就开始采样,它不需要关心左右声道数据的字长

时序图如下:

3. 右对齐模式 Right Justified Standard

也叫日本格式,sony格式。相比于标准左对齐格式,标准右对齐的不足在于接收设备必须事先知道待传数据的字长

时序图如下:

注:

标准左对齐和标准右对齐模式的LRCK/WS高低电平对应的左右声道与标准I2S模式的规定恰好相反

BCLK和LRCK的翻转

以标准I2S模式为例,BCLK在LRCK的第一个上升沿开始有效,数据则是在BCLK的上升沿开始传输;数据在BCLK的上升沿变换,在BCLK的下降沿被读取。

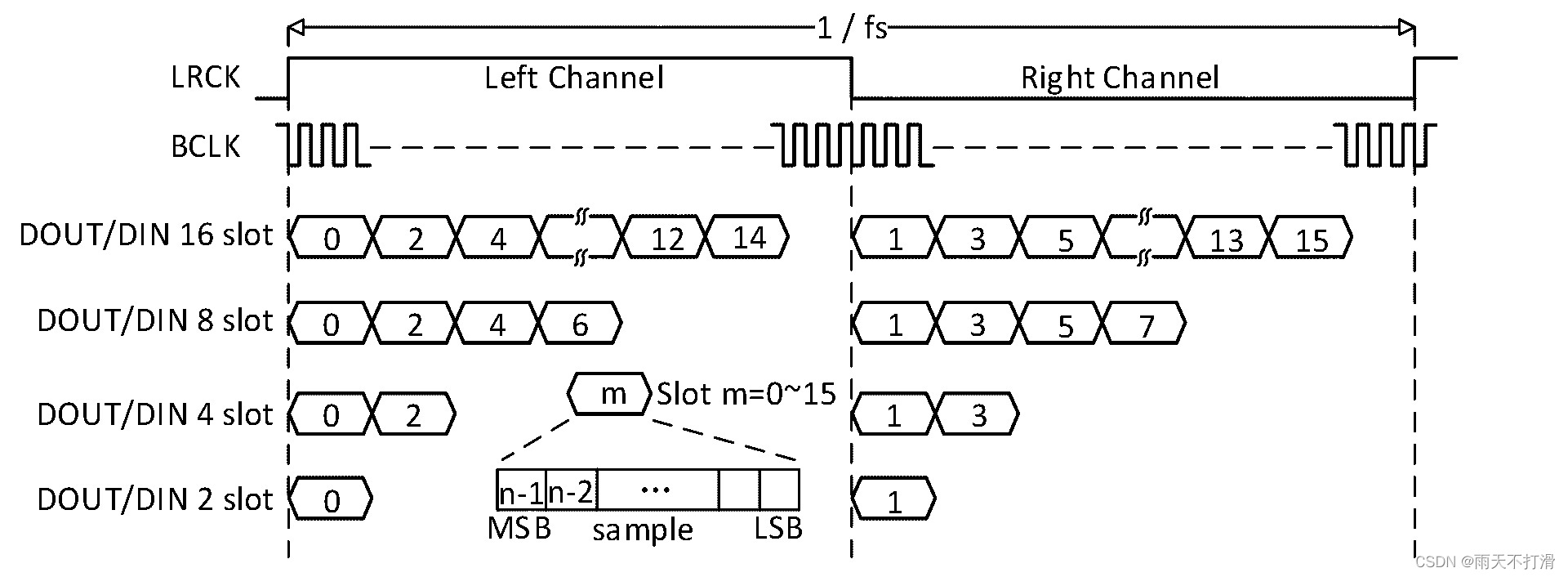

TDM模式

最开始出现的I2S只能传输左右两通道的数据,后来为了传输多通道数据,出现了I2S的变体,即应用了TDM(时分复用)模式

协议时序与旧版I2S类似,但是出现了slot(槽)的概念。

slot是指某个通道的一帧数据

slot_num是指槽的个数

slot_width是指一帧数据的位数

一般来说slot都为偶数,且音频通道数应小于等于槽数,即channel ≤ slot_num,同理采样频率应小于等于槽宽度,fs ≤ slot_width

时序图如下:

标准I2S(standard)

左对齐(left_j)

右对齐(right_j)

PCM协议

PCM接口和I2S接口引脚一致 - 帧同步时钟、位时钟,主要有两种模式:短帧、长帧。

时序图如下:

短帧(dsp_a)

长帧(dsp_b)

由于没有统一标准,不同厂商对FSYNC脉冲宽度及触发边沿的设置可能不同。如上图:

短帧模式下,帧同步时钟宽度为一个位时钟周期,数据在FSYNC有效后,BCLK的第二个上升沿有效;

长帧模式下,帧同步时钟宽度为两个位时钟周期,数据在FSYNC有效后,BCLK的第一个上升沿有效。

时钟计算:

短帧:bclk = lrck * (slot * slot_width + 1)

长帧:bclk = lrck * (slot * slot_width)