前言

唉,裤子还没穿上,收到了通知实验室的FPGA原型验证少了点人,让我去投一下。我还没在舒适区待几分钟,而且安全这一块还有很多让我需要去学习的。人生啊。

对芯片这一块确实不怎么了解,于是乎,这段时间没有写什么东西,都是在刷视频,迷茫。因为这个不知道怎么入手。

到了今天乘着这个圣贤时刻,还是得起来干活,告诉自己别浮躁。然后看了一下才知道FPGA原型验证是处于芯片设计的流程,按照我的学习习惯,咱们进入任何的一个方向的时候,得先去对这个行业的整个线有个认识,知道自己处在了什么的位置。

那么首先得补补芯片方面的知识,于是今天找了本书,来看看。

SoC设计方法、平台、工具

- ● SoC产生的背景、发展及挑战;

- ● SoC、IP的定义及IP核复用的概念;

- ● SoC的设计方法、平台、工具;

- ● SoC的验证与测试;

- ● SoC几种常用总线的架构。

一、 SoC产生的背景

有代表性的集成电路存储器和CPU为例,在集成电路的特征尺寸从1978年的10 μm发展到2000年的0.25 μm的过程中,DRAM的容量从1971年的1KB发展到2000年的1 GB,CPU的主频也从70年代的750 kHz发展到2000年的1 GHz,现在微电子技术已经从3 GB时代发展到了3TB时代(即存储容量由G位发展到T位),集成电路器件的速度由GHz发展到了THz,数据传输速率由Gbps发展到Tbps。

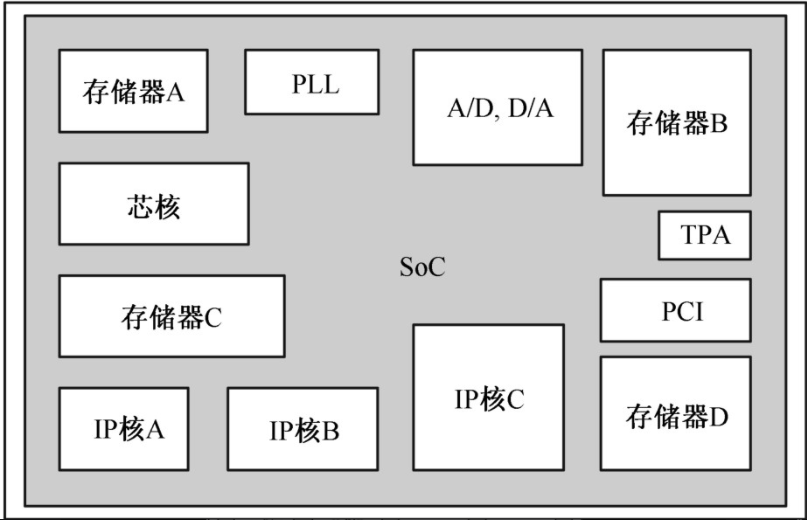

集成电路的集成度越来越高,已经可以把整个系统都集成在一个芯片之内。目前绝大多数的整机系统都是通过印刷电路板(PCB)将各个芯片连接起来组成的,虽然芯片本身功耗小、速度快,但印刷电路板带来的连线延时和噪声却大大降低了系统性能,成为系统发展的瓶颈,在这样的技术推动与需求牵引下就出现了系统级芯片(System on Chip,SoC),如图9-1所示。

那什么是Soc

二、系统级芯片SoC

SoC一词在多年前就已经出现,但什么是SoC仍然没有统一的说法。简单地说,SoC就是System on Chip,其中文翻译就是系统级芯片,它是指在单一芯片上实现的数字计算机系统。该系统应包含两个基本部分:硬件部分和软件部分。硬件部分包括微处理器/微控制器、存储器以及其他专用功能逻辑等计算机的基本部件;软件部分主要指操作系统,也可以包括重要的应用软件。

我们也可以认为SoC是具备了以下特征的一种集成电路芯片:实现复杂系统功能的VLSI(超大规模集成电路),采用超深亚微米工艺技术,使用一个或数个嵌入式数字信号处理器(DSP),具有对外部芯片进行编程的功能,主要采用第三方的IP核进行设计。

从SoC的特征看,它包含了微处理器/微控制器、存储器以及其他专用功能逻辑,但是并不是包含了微处理器/微控制器、存储器以及其他专用功能逻辑的芯片就是SoC。SoC技术被广泛认同的根本原因是采用了已有的或第三方已经设计出来的IP,SoC可以在较短的时间内被设计出来,缩短了产品上市的时间。因此,SoC更合理的定义为:SoC是在单一硅片上集成了微处理器/微控制器、存储器以及其他专用功能逻辑,并广泛使用IP(Intellectual Property,知识产权)而使整个系统得以快速开发的完整系统。

如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。国内外学术界一般倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上。它通常是客户定制的,或是面向特定用途的标准产品。

SoC的特点主要有两个方面:

- 第一是在其设计时大量使用已有的或者第三方提供的可复用的IP;

- 第二是其制成。

SoC芯片是一个集成在单一硅片上的完整系统,如此复杂的芯片,如果每设计一个芯片就重新设计它上面包含的所有模块,那么工作量就会很大,有可能会错过产品上市的最佳时间。

从系统的抽象性结构分析,一般的电子系统是由输入/输出接口、数据处理、数据存储三大部分构成,因此,绝大多数SoC系统都包含一些相同或相似的模块,比如I/O接口、微控制器、数字信号处理器、总线控制器、各种存储器、数/模及模/数转换器、电源模块等,其结构示意如图9-2所示。

正是SoC包含的这些相同或相似的模块促使了许多专门设计、开发IP的第三方IP供应商的产生。同时,迫于市场的紧迫要求,设计者必须要在计划的时间内完成设计,采用已经经过严格验证的高质量的IP模块,缩短开发周期和降低投资风险。

所以SoC芯片的一大特点就是大量使用可复用的IP模块。

SoC芯片的另一个特点就是它的制成。从0.25μm、0.18μm、0.13μm到28nm的集成电路制成可以看出,如今的集成电路已经将以往的电路体积缩小了许多倍。

SoC芯片生产厂商在制成方式不断进步的同时,必须不断提高自己的芯片生产能力,并且必须考虑因缩小芯片体积而引发的一系列问题。例如,当芯片内的走线细到一定程度时将不得不考虑相邻两条线之间的干扰。

作为一个集成在单一硅片上的完整系统的SoC也具有以下优势:

- ● 嵌入式模拟电路的Core可以抑制噪声问题;

- ● 使DRAM和CPU的速度接近;

- ● 能极大地改善功耗开销;

- ● 在相同工艺条件下实现更高的性能;

- ● 可减少印制板上部件数和引脚数;

- ● 减少板卡失效的可能性,有利于板卡的性能改善(由于片内连线缩短);

- ● 降低风险要求,减少系统开发成本;

- ● 尤其适合数字化产品开发,如手持设备、信息家电等。

然而,**SoC芯片与我们通常说的专用集成电路的设计思想以及设计方法都是有区别的,**它是微电子设计领域乃至整个信息产业的一场革命。

三、IP与IP核

**IP(Intellectual Property)核是SoC的建造基础。**已有的或从第三方获得的具有知识产权的模块(或内核)称为IP核。

应用IP核作为宏单元进行系统设计,就是基于IP的设计方法。今天所称的IP是指那些具有较高集成度并具有完整功能的单元模块,如MPU、DSP、DRAM、Flash等模块。

IP核提供的功能包括CPU、DSP、串口、互连标准模块(如PCI、USB、IEEE1394)、图形计算函数和各种存储器。IP模块的再利用除了可以缩短SoC芯片的设计时间,还可以大大降低设计和制造成本,提高可靠性。

从满足SoC设计要求来说,IP核必须有以下4个特征:

- ● 必须符合设计再利用的要求按嵌入式专门设计;

- ● 必须经多次优化设计,达到通常的“四最”(芯片面积最小、运算速度最快、功耗最低、工艺容差最大)的目标;

- ● 必须允许多家公司在支付一定费用后商业运用,而不是设计公司内部专用;

- ● 必须符合IP标准。

从其实现的形式和应用层次上来看,IP核可以有三种不同的表现形式;软核(Soft Core)、硬核(Hard Core)和固核(Firm Core)。

1-软核

软核(Soft Core)是完全用HDL语言描述出来的IP,它与实现技术无关,可以按使用者的需要进行修改,其性能通过时序模拟进行验证。由于软核不依赖于任何实现工艺或实现技术,具有很大的灵活性,使用者可以方便地将其映射到自己所使用的工艺上去,可复用性很高。

软核的另外一个重要的优点是使用者拥有全部源代码,使用者可以通过修改源代码,方便地生成同样功能且自有版权的新软核,从而避免向原有软核的作者支付版税。同时,聪明的软核使用者还可以通过自己的知识和经验,生产出比原始软核广泛得多的新的软核。

正是由于软核的上述优点,它的价格不菲,且提供者寥寥无几。软核的载体是硬件描述语言,且与实现的工艺无关,使用者在最终将其嵌入自己的设计时就要对从描述到版图的转换全过程负责。显然这要涉及经典IC设计的全部内容,IC设计人员必须具备相当的风险意识。另外,工艺映射和系统的性能有着一定的内在关系,是否可以不加修改地将一个软核映射到任何一个工艺上仍然是需要探讨的一个问题。

2-硬核

硬核(Hard Core)是指经过预先布局且不能由系统设计者修改的IP。

硬核对面积和性能进行了优化,映射为专门的工艺,并以版图文件或黑匣子模型的形式提交,经过实际工艺流片验证。

显然,硬核强烈地依赖于某一个特定的实现工艺,而且在具体的物理尺寸、物理形态及性能上具有不可更改性。这些特点对使用者来说有喜有忧。优点是硬核已经通过验证并具有最优的面积和性能的设计,使用者不需考虑与此相关的优化问题。但问题在于硬核与工艺的强相关性迫使使用者也只能使用该工艺完成电路其他部分的设计,而且要在布局布线时注意遵守固核的物理限制。

显然,硬核的特点决定了使用者进行电路设计时的灵活性很小,希望通过获得硬核以生成其他硬核的可能基本上没有,即使有,受到加工工艺经费和知识产权等方面的限制,也会失去意义。从另外一个角度看,正是因为硬核的这些缺点,它的使用价格在软核、固核和硬核三种IP核中是最低的。

3-固核

固核(Firm Core)由RTL描述和可综合的网表组成。 处于软核和硬核之间,以电路网表的形式提交并通常采用硬件进行验证。

硬件验证的方式有很多种,比如可以采用可编程器件(如FPGA、EFLD)进行验证,采用硬件仿真器进行验证等。固核往往对应于某一个特定的实现工艺,在该实现工艺的条件下固核具有最优的面积和性能特性。对于使用者来说不需要对固核的功能给予过多的关注,可以减少许多相关的设计工作,同时由于固核的时序特性是经过严格检验的,设计者只要保证在布局布线过程中电路关键路径的分布参数不会引起时序混乱就可以保证芯片的设计成功。

-

软核:HDL代码全公开,可以直接修改代码。与工艺无关。

-

硬核:是个黑盒,布局布线时放到版图里,对外只有接口,内部结构啥也不知。与工艺强相关。

-

固核:门级网表,可以看到基本的门电路,理解起来较困难。与工艺强相关。

用简单的例子来说,你需要盖一间房子,软核就是一份大学土木施工教材,告诉你一间住了不会死人的房子大概需要有一根横梁,需要有门窗,以及一些门不能开在天花板上之类的描述,有了这些描述普通大学生肯定不可能建出房子,但经验老道的建筑师可以根据一份这样的描述做出定制化程度很高的,有个性的房子。总结就是软核比较抽象,但也非常灵活。

固核大概就是标准的施工文件,画好了具体结构,标好了长宽高,照着施工就可以盖出图纸描述的房子,虽然整体形状已经被规定好了,但房子上面还可以做点雕花啥的,可以自己定制。总结就是固核相比较软核更具体,但灵活性稍差。

硬核则是一个已经完成施工的标准单元,你购买之后用吊车吊起来就可以住人了,但显然你不能对他的结构外观什么的做个性化设置。硬核是最具体的,通常也是应用最方便的,但同时也是灵活性最差的。以上是形象的描述,如果用稍微专业一点的话来描述,软核通常是RTL文件,描述了寄存器级的行为;固核是RTL文件和综合后网表文件,已经完成了部分布局布线;而硬核是经过验证的,完成物理后端设计的版图文件,拿到了就可以直接给台积电生产了。

作者:William Huang

链接:https://www.zhihu.com/question/420197045/answer/1462709981

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

4-小知识

RTL描述方式也称为数据流描述方式。数据流描述是对从信号到信号的数据流的路径形式进行的描述,很容易进行逻辑综合。

但是固核也有其自身的缺点,那就是它与实现工艺的相关性及网表的难读性。与实现工艺的相关性限制了固核的使用范围,网表的难读性则使得布局布线后发生的时序违反的排除变得比较困难。由于固核在使用方便程度上和开放程度上均介于软核和硬核之间,故其价格也处于它们之间。

鉴于对IP核知识产权的保护和技术保密,IP供应商一般不会提供软核,大多数供应商可以提供固核,模拟部件多是硬核或者黑匣子(Black Box)模型。一个IP模块首先要有功能描述文件,用于说明该IP模块的功能、时序要求等;其次还要包括设计实现、设计验证两个方面的文件,即不但要有实现IP模块功能的RTL源码或网表,还要有用于IP模块实现后验证逻辑功能正确性的仿真模型和测试向量。

硬核的使用比较简单,类似于PCB设计中IC芯片的使用。软核的使用较复杂,实现后的性能与其具体的实现方式有关。为了保证软核的性能,软核提供者一般还提供综合描述文件,用于指导软核的实现。固核的使用介于两者之间。

四、SoC与IP产业

目前,集成电路的设计能力远远落后于半导体工艺的发展。

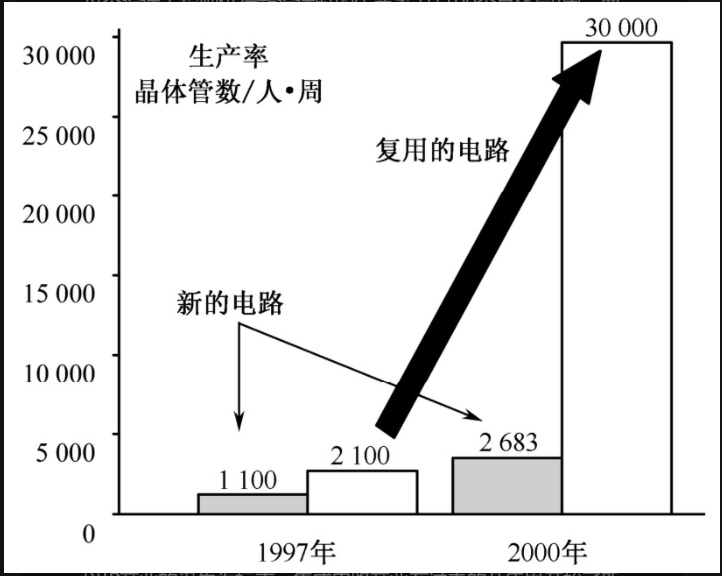

图9-3给出了工艺技术发展与IC设计效率之间的关系示意图。

SoC的设计非常复杂,需要投入大量的人力和物力,单独的一个公司几乎不可能拥有足够的工程资源和经费来进行整个SoC的开发。设计能力和工艺水平之间的矛盾成为了SoC发展过程中一个非常突出的障碍,而基于IP复用的设计方法学是当前解决这一矛盾非常有效的办法。美国Dataquest全球半导体部首席分析师Jim Tuliy指出,IP模块是设计复用的关键部分,是结束“设计间距”唯一有效的办法,如果没有它,半导体生产商和OEM(Original Equipment Manufacturer)供应商根木无法达到今天已经达到的水平。

随着软硬件协同工作领域的不断扩大和深入,嵌入式系统中的软件目前也被设计工程师们视为是IP的一种形式。IP起源于IC生产加工线所提供的标准单元库,IC设计公司使用单元库中的元件模型把基于高级语言的行为级描述转换为基于原理图的网表。在一定意义上说,生产线提供预先设计好的“功能块”,而设计公司则是系统集成公司,只不过在这个层次上功能块的规模仍然十分小(逻辑门),设计公司的工作量仍然十分繁重。

随着设计规模的越来越大,一个合乎逻辑的发展是增大标准功能块的规模,以减少设计公司的重复劳动,从而使设计周期仍然保持在合理的时间范围内。因此,我们可以看到系统级芯片与一般的集成电路设计重要的不同之处就在于其系统级设计与物理设计的界面已经不再是传统意义上的标准单元库,而是具有一定规模的功能模块或子系统。这样就可以大大提高SoC的设计效率。

美国Collett公司曾做过这样一个分析,在通过对三十余个IC设计团队、近百个具体的电路进行跟踪量化比较后发现,IP复用技术对集成电路设计,尤其是SoC设计生产率提高方面的促进作用相当显著。从图9-4中可以看出,在1997年,每个设计工程师进行新设计时的生产率为1100个晶体管/周,而采用IP模块进行设计的生产率为2100个晶体管/周。到了2000年,每个设计工程师进行新设计时的生产率仅增加了一倍,为2683个晶体管/周,而采用IP模块进行设计的生产率约为30000个晶体管/周。

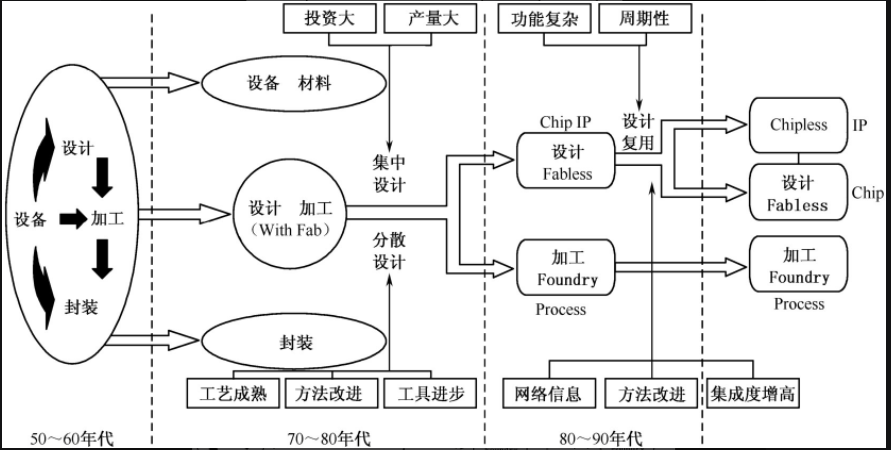

以IP产业的诞生为标志,集成电路产业在过去的几年里开始了新一轮的分工。具体表现为一些中小规模的设计公司提供商业化的IP核设计,而大公司则购买这些设计成果并逐步向系统集成公司的方向发展,如图9-5所示。

参考书籍:《32位嵌入式系统与SoC设计导论》