目录

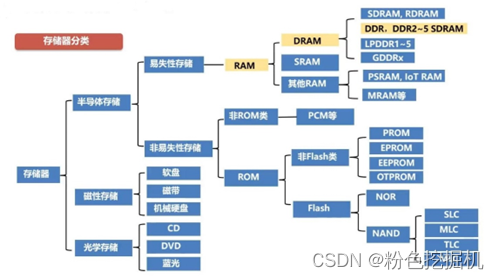

存储器是计算机系统中的记忆设备,用来存储程序和各种数据信息,存储器的存储介质主要采用半导体器件和磁性材料。接下来简单介绍存储器的主要分类。

按存储介质可以分类为半导体存储器、磁表面存储器、光存储器。

按存储器的读写功能可以分类为只读存储器(ROM)、 随机读写存储器(RAM)。

按信息的可保存性可以分类为非永久记忆的存储器、永久记忆性存储器。

按在计算机系统中的作用可以分类为主存储器(内存)、辅助存储器(外存储器)、缓冲存储器。

按功能/容量/速度/所在位置可以分类为寄存器、高速缓存、内存储器、外存储器。

按工作性质/存取方式可以分类为随机存取存储器、顺序存取存储器、直接存取存储器、相联存储器。

ROM与RAM

ROM:只读存储器(ReadOnly Memory),非易失性。它是一种只能读出事先所存的数据的固态半导体存储器。一般是装入整机前事先写好的,整机工作过程中只能读出,而不像随机存储器那样能快速地、方便地加以改写。ROM所存数据稳定,断电后所存数据也不会改变。计算机中的ROM主要是用来存储一些系统信息,或者启动程序BIOS程序,这些都是非常重要的,只可以读一般不能修改,断电也不会消失。

RAM:随机访问存储器(Random Access Memory),易失性。它是与CPU直接交换数据的内部存储器,它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储媒介,凡是整个程序运行过程中,所用到的需要被改写的量(包括全局变量、局部变量、堆栈段等),都存储在RAM中。随机访问存储器分为两类:静态的和动态的。静态的RAM(SRAM)比动态RAM(DRAM)更快,但也贵很多。SRAM用来作为高速缓存存储器,既可以在CPU芯片上,也可以在片下。DRAM用来作为图形系统的帧缓冲区。

例如常见的硬盘属于ROM,内存条属于RAM。

DRAM定义与形态

动态随机存取存储器(Dynamic Random Access Memory,DRAM)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。由于在现实中晶体管会有漏电电流的现象,导致电容上所存储的电荷数量并不足以正确的判别数据,而导致数据毁损。因此对于DRAM来说,周期性地充电是一个无可避免的要件。由于这种需要定时刷新的特性,因此被称为“动态”存储器。相对来说,静态存储器(SRAM)只要存入数据后,纵使不刷新也不会丢失记忆。

与SRAM相比,DRAM的优势在于结构简单——每一个比特的数据都只需一个电容跟一个晶体管来处理,相比之下在SRAM上一个比特通常需要六个晶体管。正因这缘故,DRAM拥有非常高的密度,单位体积的容量较高因此成本较低。但相反的,DRAM也有访问速度较慢,耗电量较大的缺点。

|

|

存储信息 |

破坏性读出 |

需要刷新 |

送行列地址 |

运行速度 |

集成度 |

发热量 |

存储成本 |

| SRAM |

触发器 |

否 |

否 |

同时 |

快 |

低 |

大 |

高 |

| DRAM |

电容 |

是 |

是 |

分两次 |

慢 |

高 |

小 |

低 |

DRAM存储单元

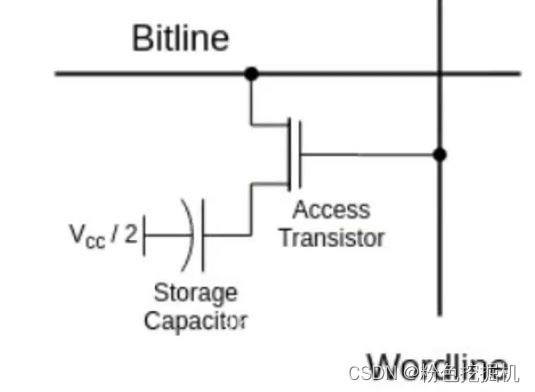

DRAM存储单元为DRAM Storage Cell,使用DRAM Storage Cell来存储bit信息。

DRAM Storage Cell由4个部分组成:

Storage Capacitor,即存储电容,它通过存储在其中的电荷的多少(或者说电容两端电压差的高低)来表示逻辑上的0和1;

Access Transistor,即访问晶体管,它的导通和截止,决定了允许或禁止对Storage Capacitor所存储的信息的读取和改写;

Wordline,即字线,它决定了Access Transistor的导通或截止;

Bitline,即位线,它是外界访问Storage Capacitor的唯一通道,当Access Transistor导通后,外界可以通过Bitline对Storage Capacitor进行读取或者写入操作。

DRAM架构和工作流程

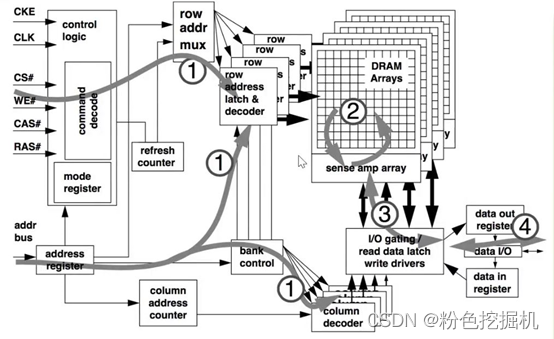

1.Command transport and decode

在这个阶段,Host端会通过Command Bus和Address Bus将具体的Command以及相应参数传递给SDRAM,SDRAM接收并解析Command,接着驱动内部模块进行相应的操作。

2.In bank data movement

在这个阶段,SDRAM主要是将Memory Array中的数据从DRAM Cells中读出到Sense Amplifiers,或者将数据从Sense Amplifiers写入到DRAM Cells。

3.In device data movement

在这个阶段中,数据将通过IO电路缓存到Read Latchs或者通过IO电路和Write Drivers更新到Sense Amplifiers。

4.System data transport

在这个阶段,进行读数据操作时,SDRAM会将数据输出到数据总线上,进行写数据操作时,则是Host端的Controller将数据输出到总线上。