目录

扫描二维码关注公众号,回复:

14585581 查看本文章

时序电路的概念:

在组合电路中,任一时刻的稳定输出只取决于当时的输入,而在时序电路中任一时刻的稳定输出,不仅可能取决于当时的输入,还取决于电路的原来的状态,即与过去的输入情况有关。

下面以一个简单的三位计数器为例,说明时序电路的结构:

3位计数器,由时钟上升沿触发,计数从000~111,到111后则重新回到000。

采用上升沿触发的D触发器作为状态寄存器,D触发器的示意图和真值表如下:

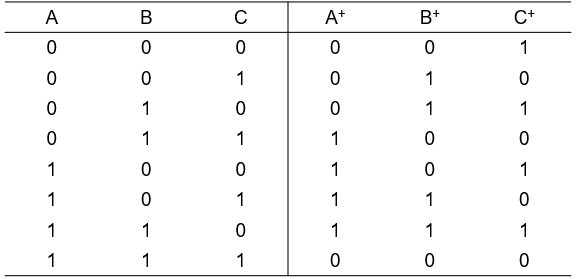

用A、B、C分别表示3个位,则A+、B+、C+表示A、B、C的次态。其真值表如下:

用A、B、C分别表示3个位,则A+、B+、C+表示A、B、C的次态。其真值表如下:

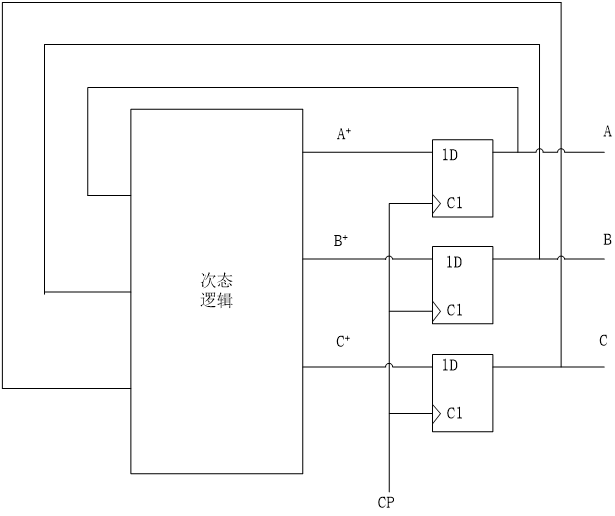

三位计数器的结构:

根据上面的分析,3位计数器需要用到3个状态寄存器。A+、B+、C+是状态寄存器的输入;A、B、C是状态寄存器的输出。由此可根据时序电路的一般模型可画出3位计数器的结构。

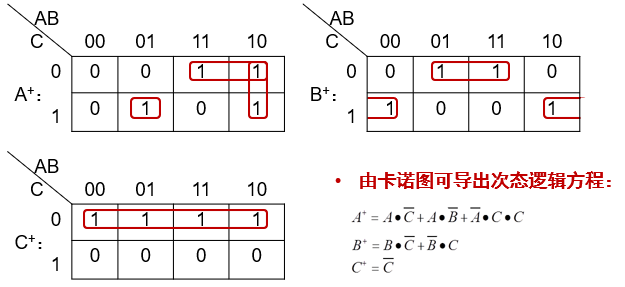

次态逻辑关系的推导;画出卡诺图如下:

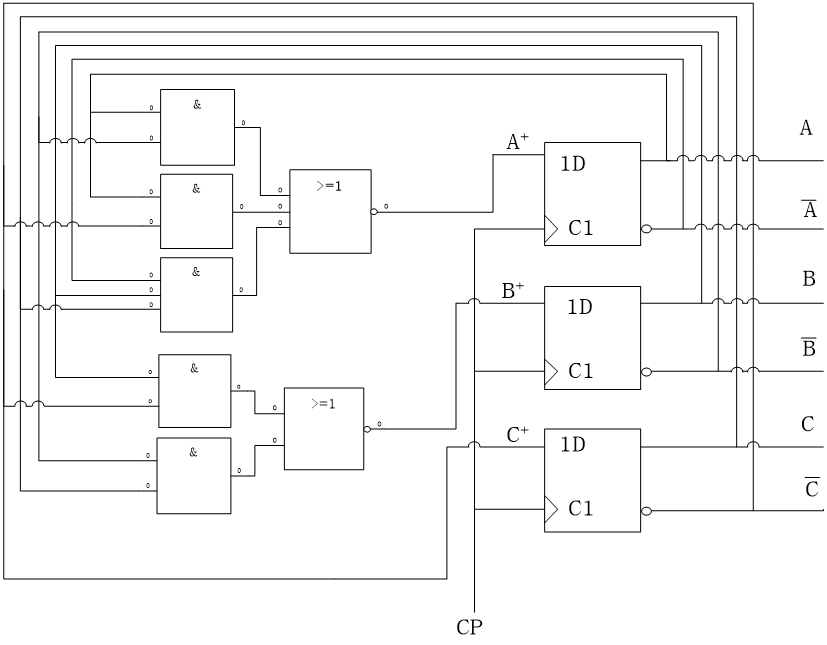

电路图:

根据次态电路的组成,可以得到次态逻辑的组成,从而可以得出3位计数器的详细电路:

时序电路与状态机的关系:

状态机的本质:

状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法。具有逻辑顺序和时序规律的事件都适合用状态机描述。

同步时序逻辑电路符合状态机的一般特征,即具有逻辑顺序和时序规律,所以可以用状态机描述

状态机的基本要素:

状态:也叫状态变量。在逻辑设计中,使用状态划分逻辑顺序和时序规律。

输出:输出指在某一个状态时特定发生的事件。

输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态。

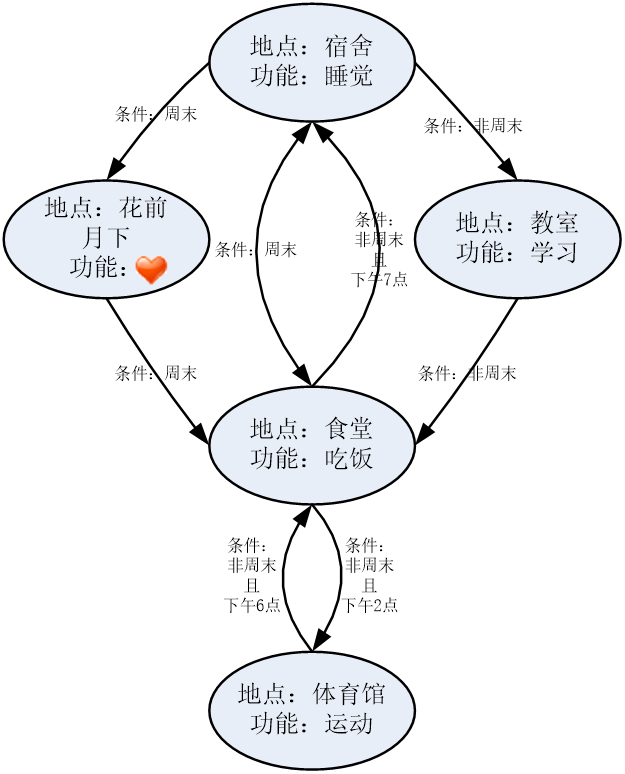

日常生活中的状态机:

描述时序电路的状态机的组成:

组合逻辑:组合逻辑又可分为次态逻辑和输出逻辑两个部分。其中:次态逻辑的功能是用来确定有限状态机的下一个状态;输出逻辑是用来确定有限状态机的输出。

存储逻辑:寄存器逻辑的功能:用来存储有限状态机的内部状态。