嵌入式系统及其原理复习重点笔记

2 ARM处理器和指令集

ARM处理器简介

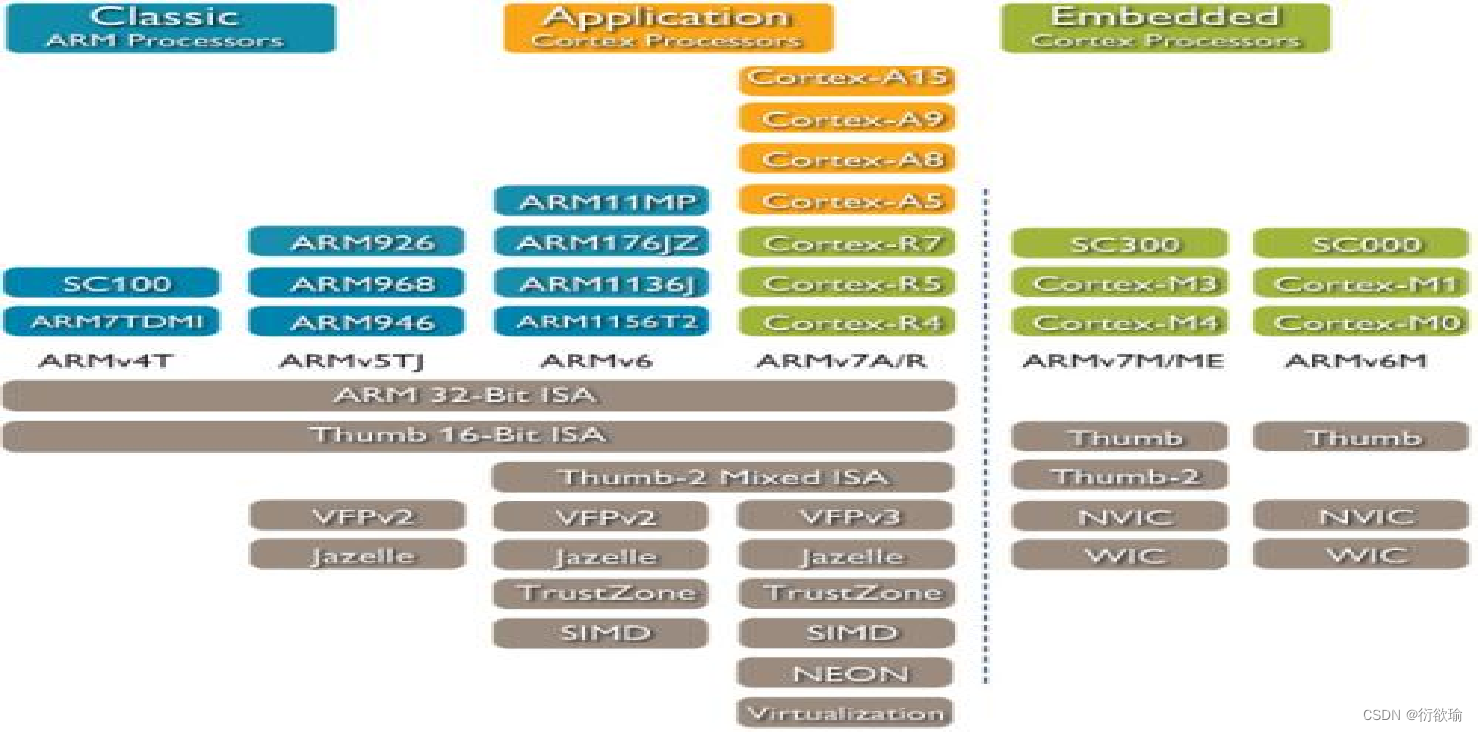

ARM架构与ARM处理器对应关系

V1版架构

该版架构只在原型机ARM1出现过,处理能力有限,其基本性能:

- 寻址空间:64M字节(26位)

- 基本的数据处理指令(无乘法)

- 字节、半字和字的LOAD/STORE指令

- 转移指令,包括子程序调用及链接指令

- 软件中断指令

V2版架构

该版架构对V1版进行了扩展,如ARM2与ARM3(V2a版)架构,增加了以下功能:

- 乘法和乘加指令

- 支持协处理器操作指令

- 快速中断模式

- SWP/SWPB指令,实现最基本存储器与寄存器交换指令

- 寻址空间:64M字节(还是26位)

V3版架构

- 把寻址空间增至32位(4G字节),而且向前兼容

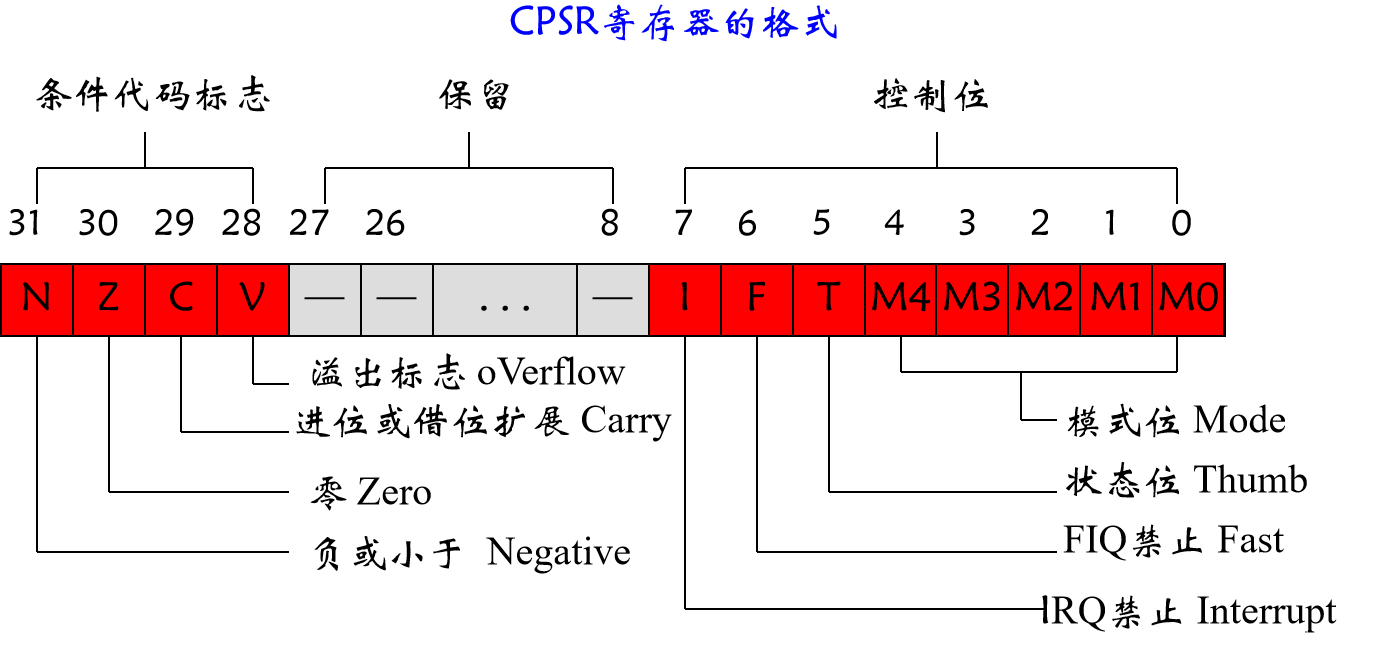

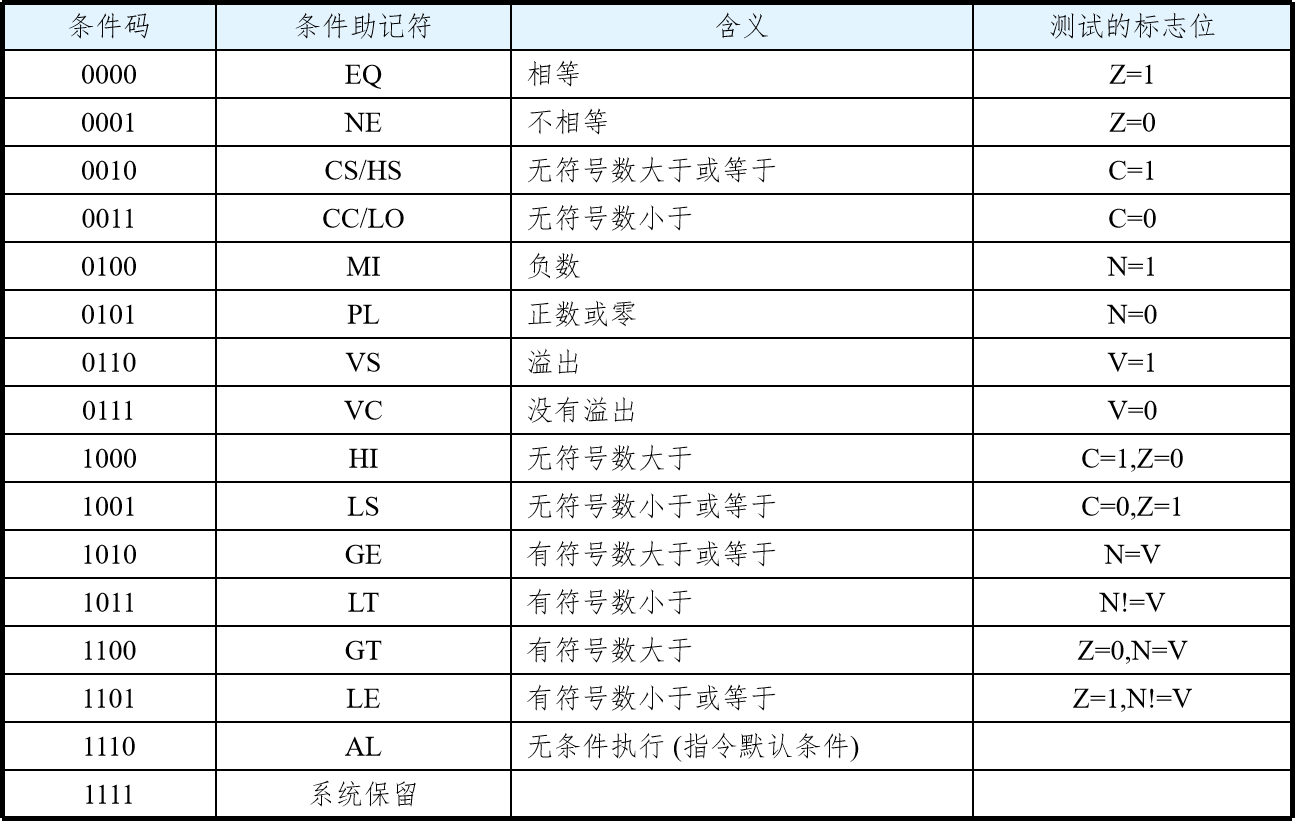

- 增加了当前程序状态寄存器CPSR(Current Program Status Register)和程序状态保存寄存器SPSR(Saved Program Status Register)。

- 增加了中止(Abort)和未定义二种处理器模式。

- ARM6就采用该版架构。指令集变化如下:

- 增加了MRS/MSR指令,以访问新增的CPSR/SPSR寄存器

- 增加了从异常处理返回的指令功能。

ARM的程序状态寄存器(CPSR)简介

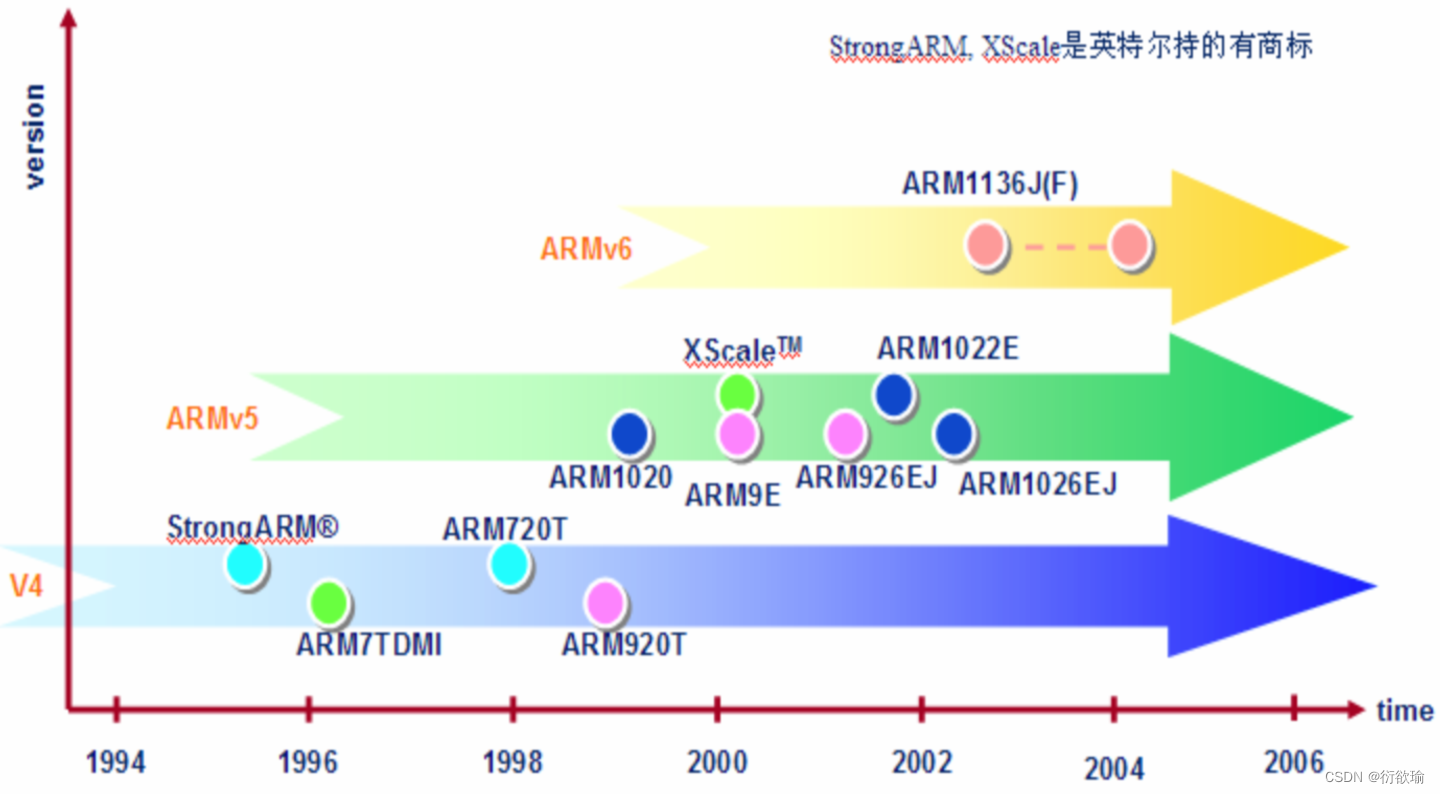

V4版架构

- V4版架构是曾经应用最广的ARM体系结构,对V3版架构进行了进一步扩充。

- 引进了16位的Thumb指令集,使ARM使用更加灵活。

- ARM7、ARM8、ARM9和StrongARM都采用该版架构。指令集中增加了以下功能:

- 增加了16位Thumb指令集

- 增加了处理器系统模式,在该模式下,处理器使用用户寄存器操作

- 符号化和非符号化半字及符号化字节的存/取指令

- 完善了软件中断SWI指令的功能

- 把一些未使用的指令空间捕获为未定义指令

THUMB指令集( ‘T’)

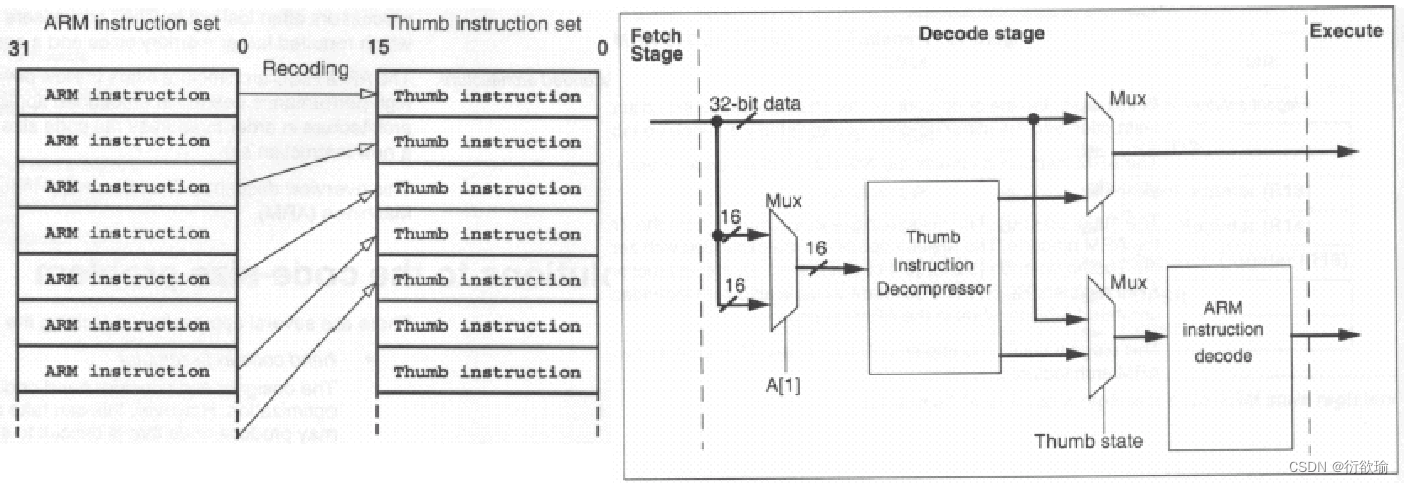

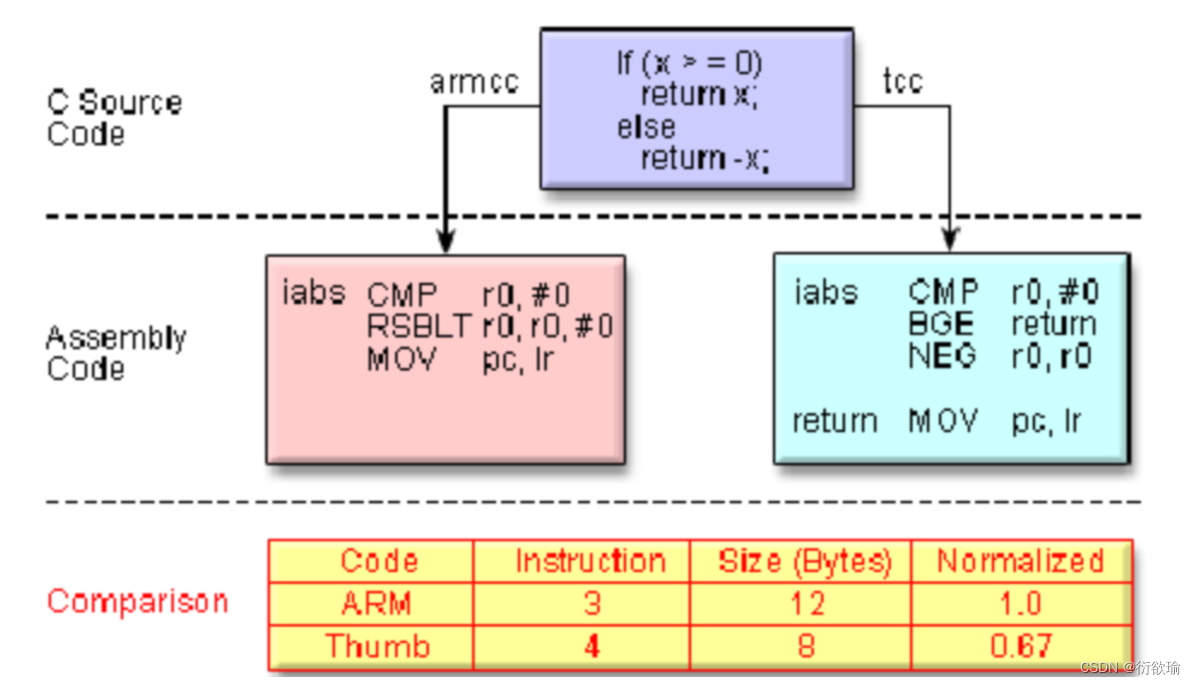

THUMB 指令集: 32位ARM指令集的子集,按16位指令重新编码

ARM指令集效率高,但是代码密度低,Thumb指令集具有更好的代码密度,却仍然保持ARM的大多数性能上的优势,

- 代码尺寸小( up to 40 % compression)

- 简化设计

ARM vs Thumb

V5版架构

在V4版基础上增加了一些新的指令,ARM10和XScale都采用该版架构,这些新增指令有:

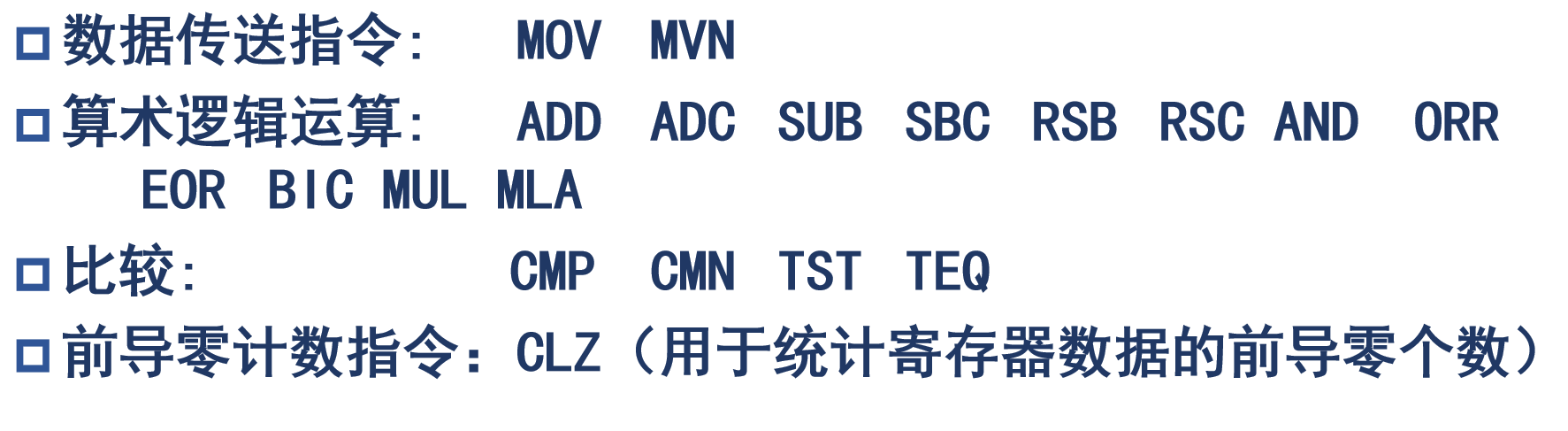

- 前导零计数CLZ指令,提高整数除法和重点优先级排队操作的效率

- BRKT中断指令(软中断)

- 增加了信号处理指令(V5TE版)

- 带有链接和交换的转移BLX指令

- 为协处理器增加更多可选择的指令

V6版架构

在芯片功耗和多媒体处理上有所突破,ARM11采用该版架构。

- 具备高性能定点DSP功能

- 引入全新Jazelle技术,降低Java程序对内存的占用,同时提高性能

- 增加多媒体扩展(SIMD变种)功能,在语音、视频、图像上的处理能力提高4倍

- 使用先进工艺使得芯片的功耗进一步降低。

- 该版本可以广泛应用于移动电话、PDA等手持设备

V7架构

目前为止32位的最高版本,ARM Cortex采用该版架构,定义了三大系列:

- “A(Application Processer)”:面向尖端的基于虚拟内存的操作系统和用户应用,Cortex-A

- “R(Real Time Controller)”:针对实时系统,Cortex-R

- “M(Micro Controller)”:对微控制器和低成本应用提供优化,Cortex-M。

增加了以下功能:

- 采用Thumb-2技术,比纯32位代码减少了内存占用,比Thumb-1提高了性能

- 采用NEON技术,即进阶SIMD延伸集,将DSP和媒体处理能力提高4倍

V8架构

首款支持64位指令集的架构,被用于对扩展虚拟地址和64位数据处理技术有更高要求的产品领域,如企业应用、高档消费电子产品。ARM Cortex采用该版架构,增加了以下功能:

- 采取64兼容32位的方式。包含两个状态:AArch64和AArch32

- 引入了一个全新指令集A64。

ARM 结构体系和处理器家族的演变发展

ARM系列处理器的体系结构,指令集,处理器ip核和处理器

ARM处理器

- ARM7系列,3级流水线,系统主时钟为20MHz到133MHz,适用于价位低、功耗低的消费类应用。无MMU(Memory Management Unit),可运行uCLinux。

- ARM9系列,5级流水线,系统主时钟为100MHz到233MHz,提供全性能的MMU,支持Windows CE、Linux等主流操作系统。

- ARM9E系列,使用单一的处理器内核,支持VFP9浮点处理协处理器,提供了微控制器、DSP、Java应用系统的解决方案。

- ARM10E系列,支持VFP10浮点处理协处理器,时钟频率则可以高达400MHz,性能大幅提升,并功耗极低。

- ARM11系列,8级流水线,时钟频率可达350MHz到1GHz,媒体处理能力强,功耗低。

- Cortex主要分为三个系列

- Cortex-A 面向高性能,13级流水线,多核

- Cortex-R 面向高实时,处理能力强,低能耗

- Cortex-M 面向微控制器,低延迟/能耗/价格

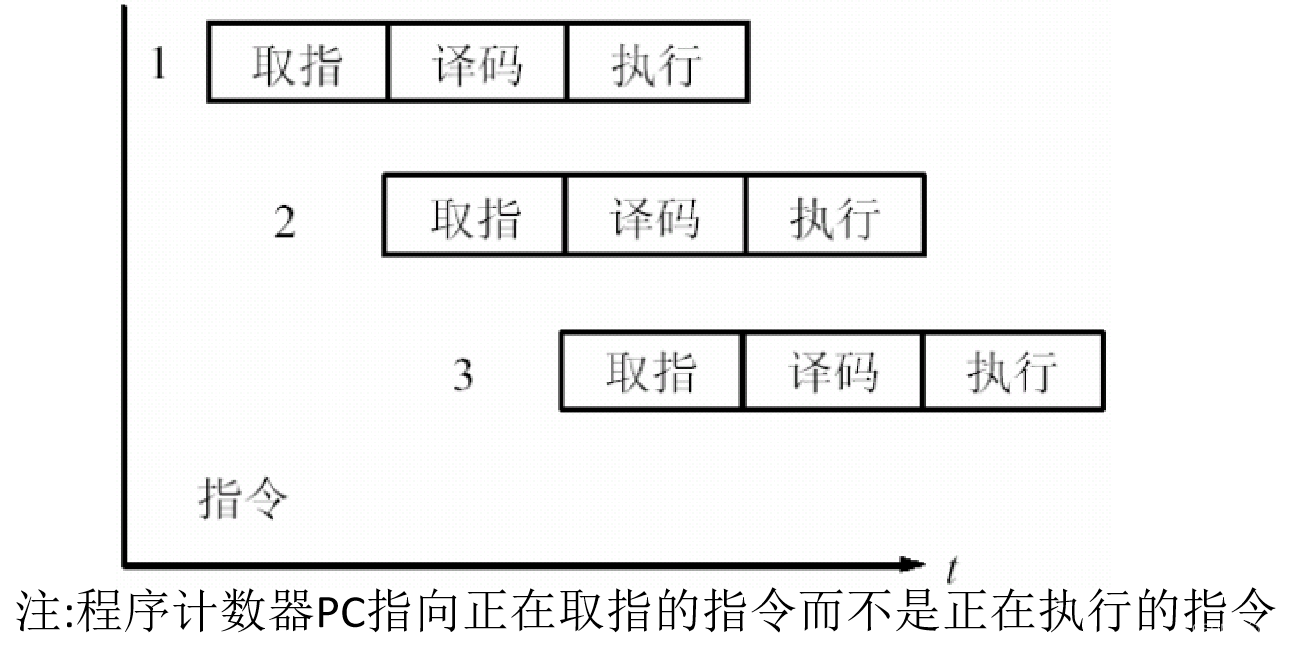

ARM7 TDMI的3段流水线操作

流水线技术

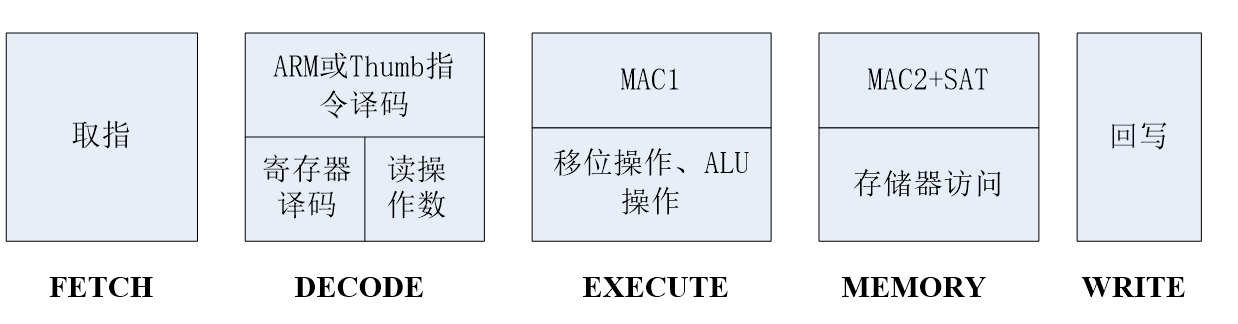

ARM9采用5级流水线技术,分别是FETCH、DECODE、EXECUTE、MEMORY、WRITE

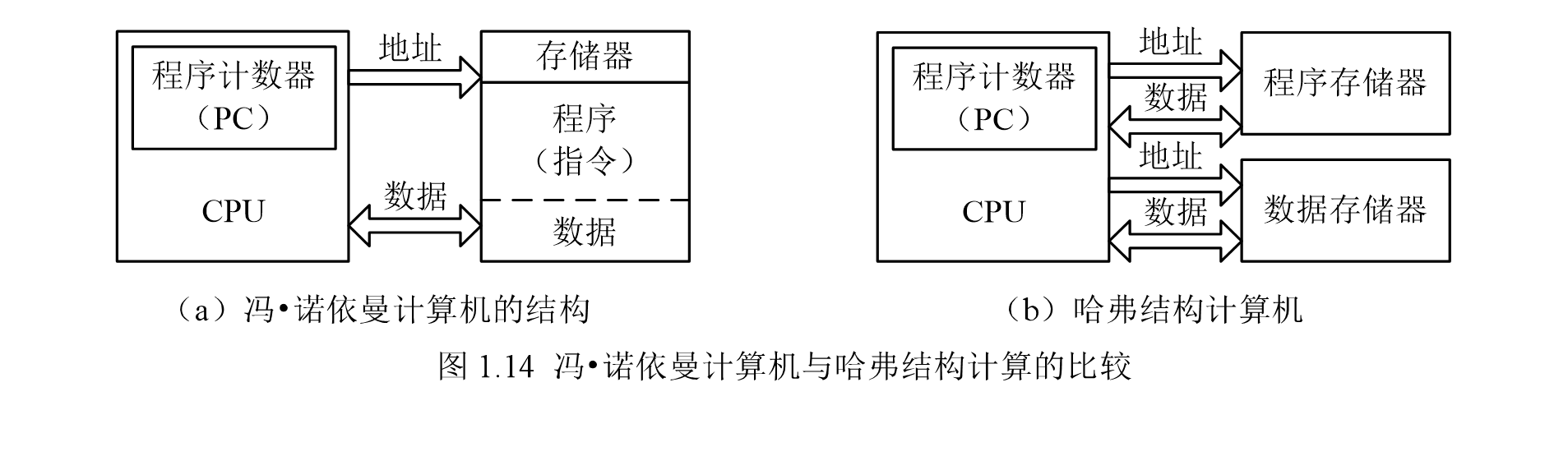

ARM9采用了哈弗体系结构

哈弗结构模型

- 是一种将程序指令存储和数据存储分开的存储器结构。这是一种并行体系结构,目的是减轻程序运行时CPU和存储器信息交换的瓶颈。

- 程序和数据存储在两个分开的物理空间中,因此取址和执行能够完全重叠。中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储器中读取数据,并进行下一步的操作(通常是执行)。

ARM指令集简介

CPU指令集

CPU 根据指令集的数量分为两类:复杂指令运算集 ( CISC )和精简指令运算集( RISC)

- 计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

- IBM研究中心的John Cocke证明,计算机中约20%的指令承担了80%的工作,于1974年,他提出RISC的概念。许多当前的微芯片都使用RISC概念。

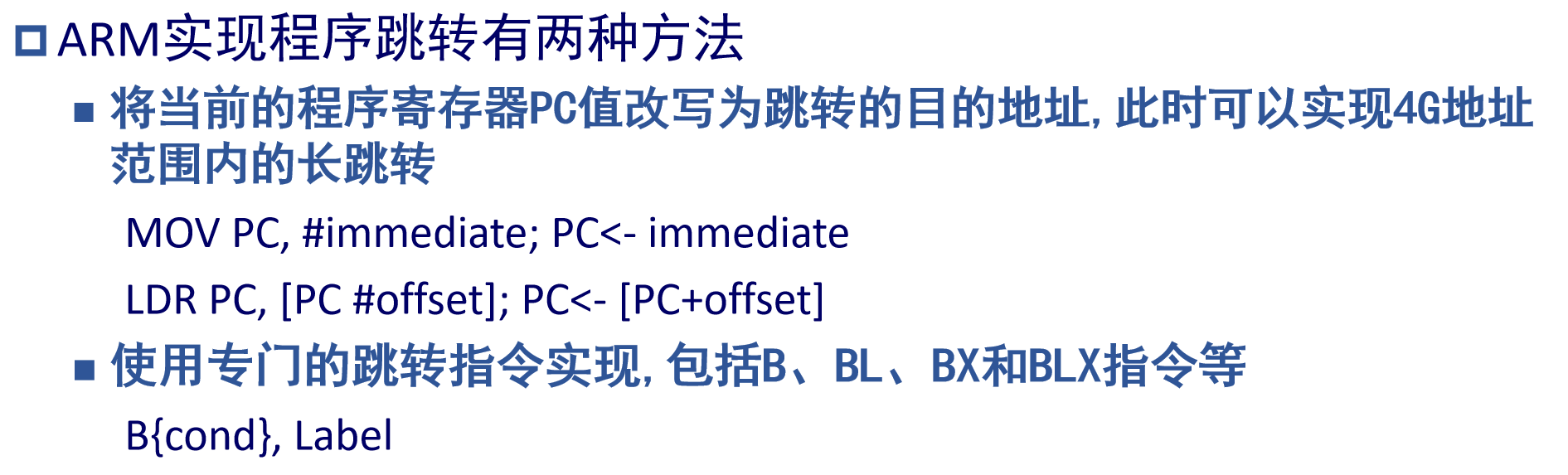

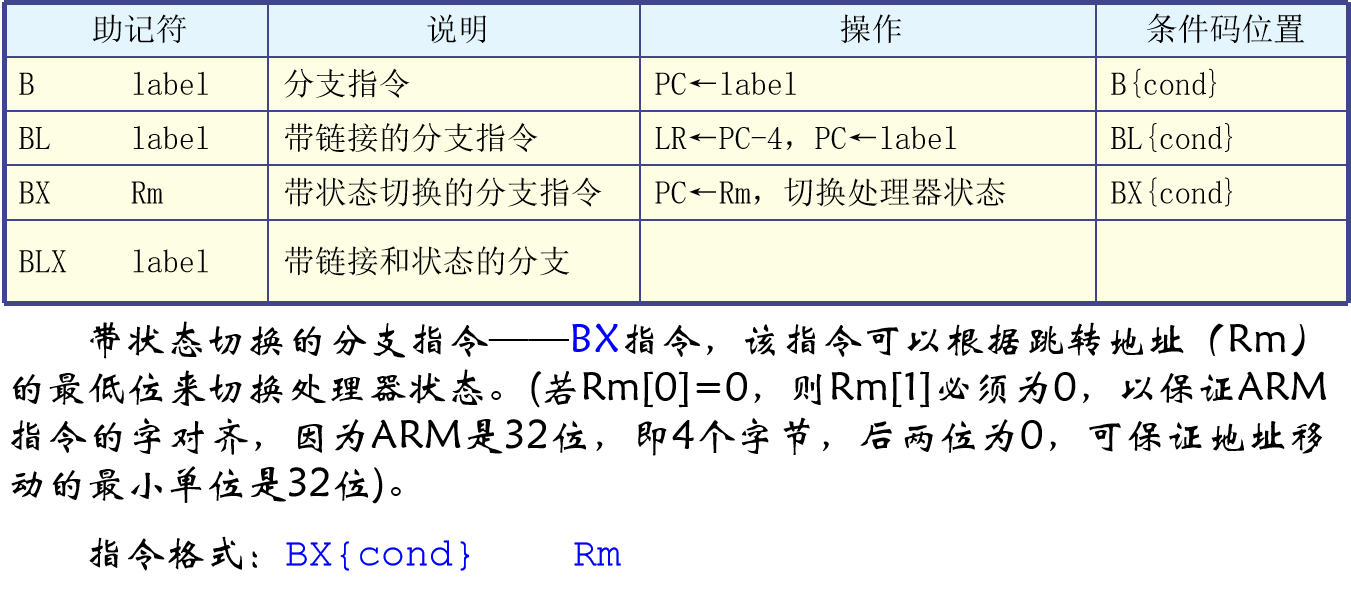

跳转指令

ARM指令集——分支指令

分支跳转指令

数据处理指令

Load/Store内存访问指令

协处理器指令

ARM伪指令

Thumb指令简介

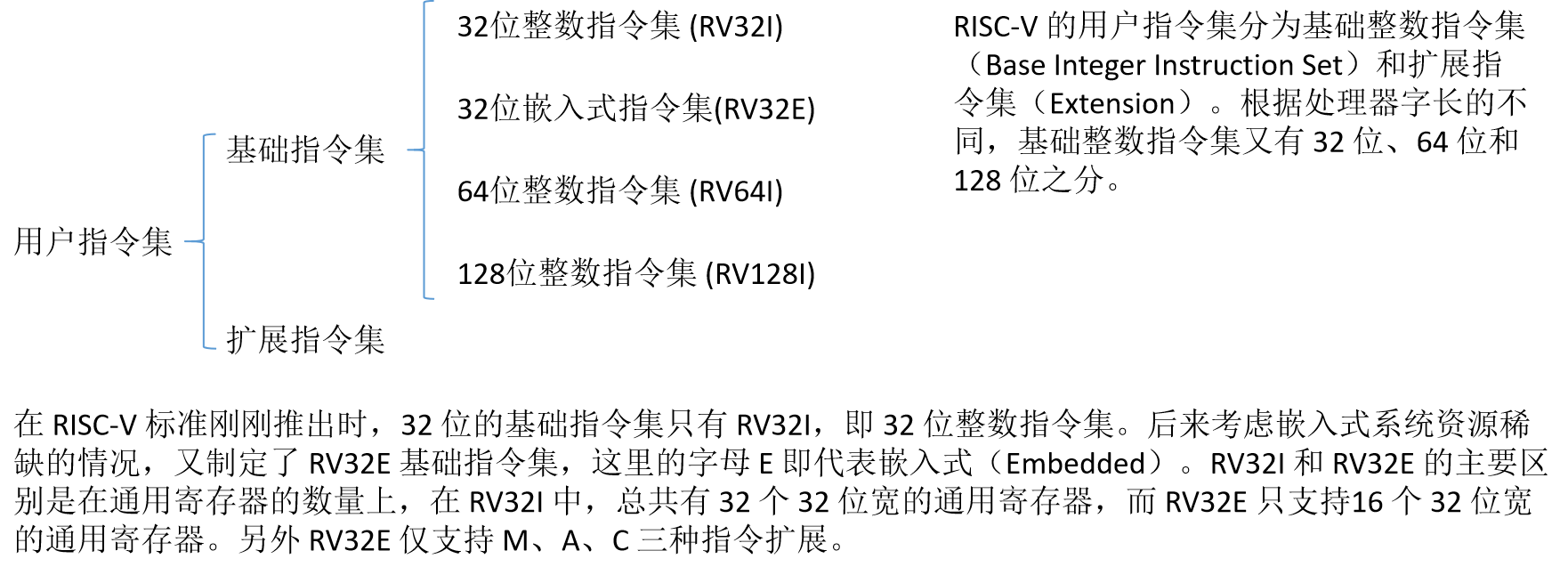

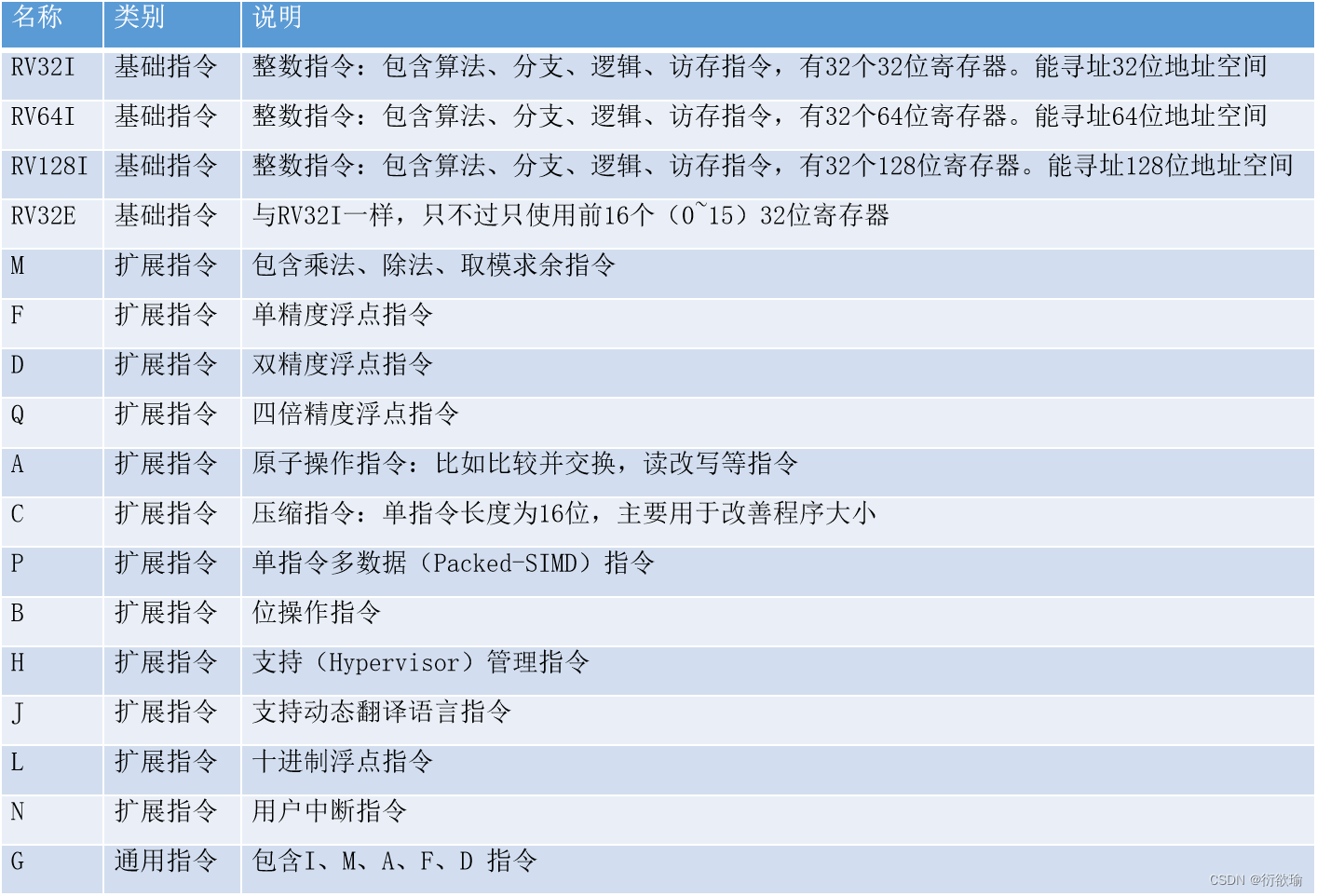

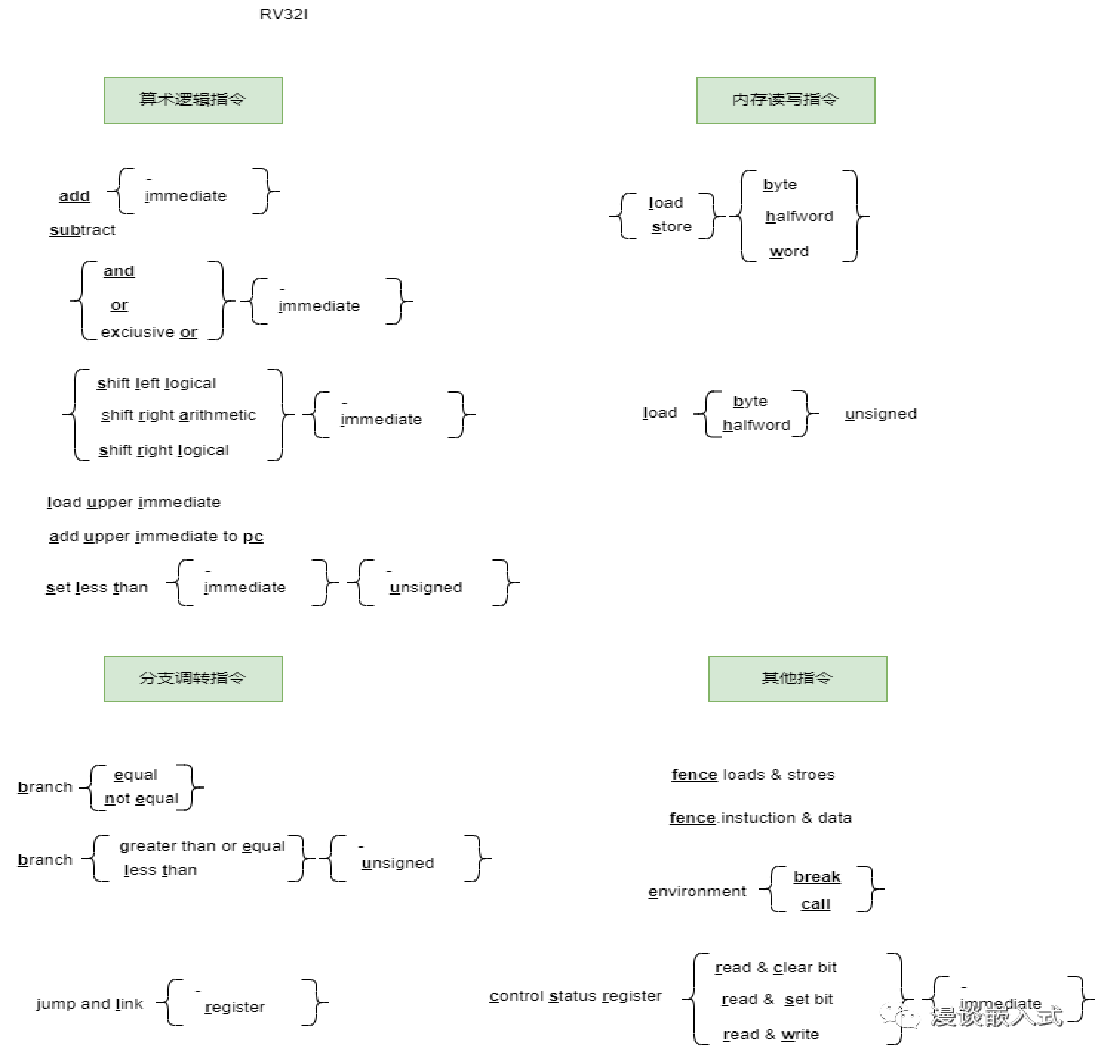

RISC-V用户指令分类

从表可以看到,RISC-V 指令集具有模块化特点。这就允许我们根据自己的需求,选择一个基础指令集,加上若干个扩展指令集灵活搭配,就可以得到我们想要的指令集架构,进而根据这样的指令架构,设计出贴合我们需求的CPU。

要满足现在操作系统和应用程序的基本运行,RV32G指令集或者RV64G指令集就够了。RV32G和RV64G指令集只有寄存器位宽和寻址大小不同。这些指令按照功能可以分为如下几类:

- 整数运算指令:算术、逻辑、比较等基础运算功能。

- 分支转移指令:实现条件转移、无条件转移操作

- 加载存储指令:实现字节、半字(half word)、字(word)、双字(RV64I)的加载,存储操作,采用的都是寄存器相对寻址方式

- 控制与状态寄存器访问指令:实现对系统控制与系统状态寄存器的原子读-写、原子读-修改、原子读-清零等操作

- 系统调用指令:实现系统调用功能。

- 原子指令:用于各种同步锁

- 单双浮点指令:实现浮点运算操作

RISC-V 的最核心部分是一个基础指令集,叫做RV32I。RV32I 包含的指令是固定不变的,这为编译器设计人员,操作系统开发人员和汇编语言程序员提供了稳定的基础框架。

RV32I 指令集:

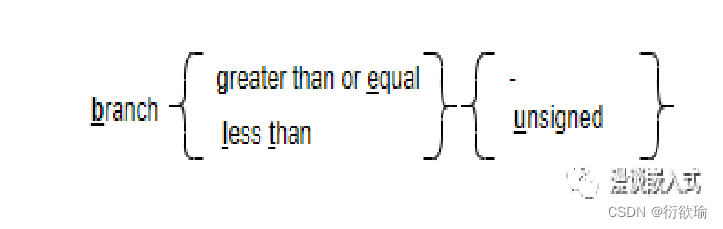

RV32I 指令集如图所示,把带下划线的字母从左至右连接组合就是组成了RV32I指令。{}表示集合中垂直方向的每个项目指令不同变体。变体用下划线字母或者下划线表示表示,如果大括号里面只有下划线,则表示对此变体不需要用字母表示

我们结合具体例子来看:下图表示了bge、blt、bgeu、bltu四个指令。

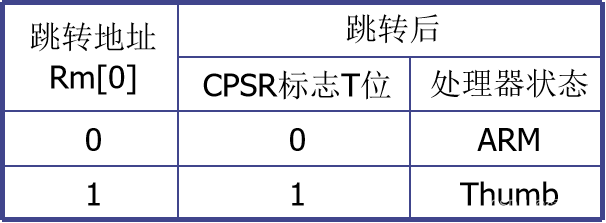

ARM状态和Thumb状态

-

Thumb指令集是16位,是32位ARM指令集的子集

-

ARM处理器支持两种运行状态:ARM状态和Thumb状态,

- ARM指令必须在ARM状态下执行;

- 同样,Thumb指令也必须处于Thumb状态下执行。

- ARM处理器可以在两种状态下进行切换。

-

必须使用ARM指令的情况:

- ARM处理器启动的第一句指令必须是ARM指令

- 访问程序状态奇存器CPSR或协处理器时必须是ARM指令

- ARM在处理异常中断时会自动切换到ARM状态,执行中断处理程序入口处的程序。返回时,会再次自动切换到ARM状态

-

V4版本中的函数调用,如果不需要进行状态切换,只需要用到BL指令就可以实现了

-

如果需要进行状态切换,需根据情况,把BL与BX合用

-

ARMv5版本后,引入了一条新的指令BLX,结合了BL和BX指令各自的功能特

点,可一条指令就能实现切换

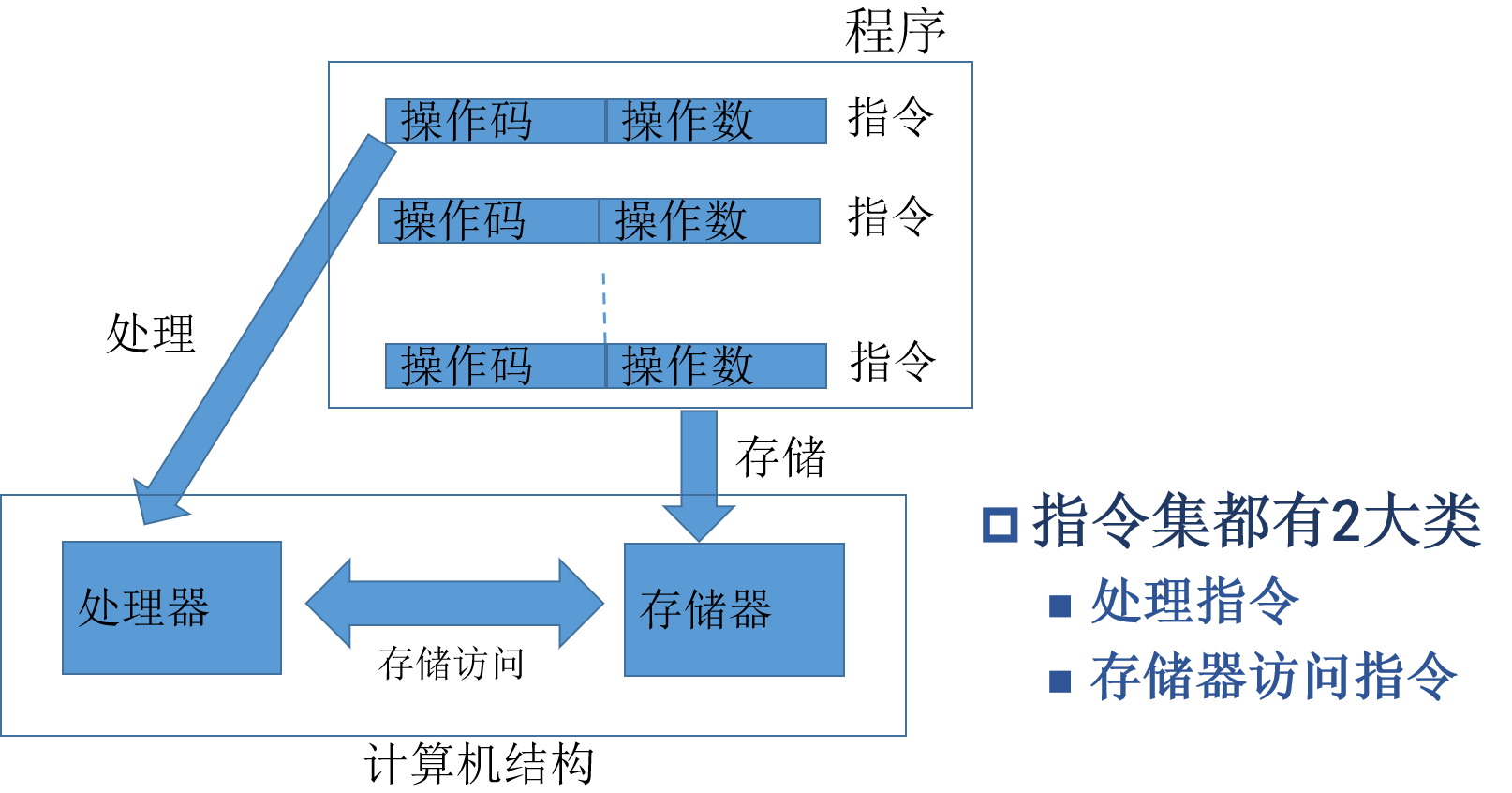

计算机的基本工作原理

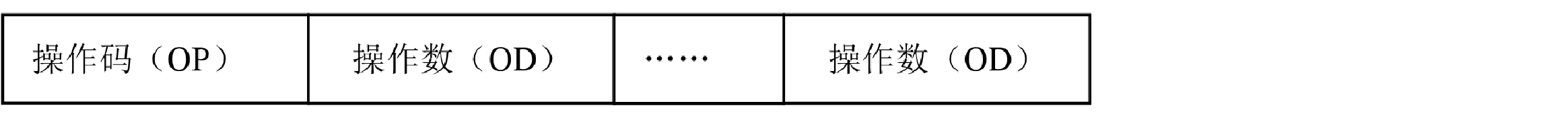

指令就是指挥计算机完成某个基本操作的命令,它完全由二进制数0和1编码构成,其操作由硬件电路来实现。

- 一台计算机上所有指令的集合构成了该计算机的指令系统。指令系统是一台计算机能够直接执行的全部基本操作。

- 为了实现特定的目标将一系列的指令进行有序的组合就形成了程序。

- 任何复杂的问题在计算机中都会被分解为一系列的指令,一个指令规定计算机执行一个基本操作,一个程序规定计算机完成一个完整的任务。

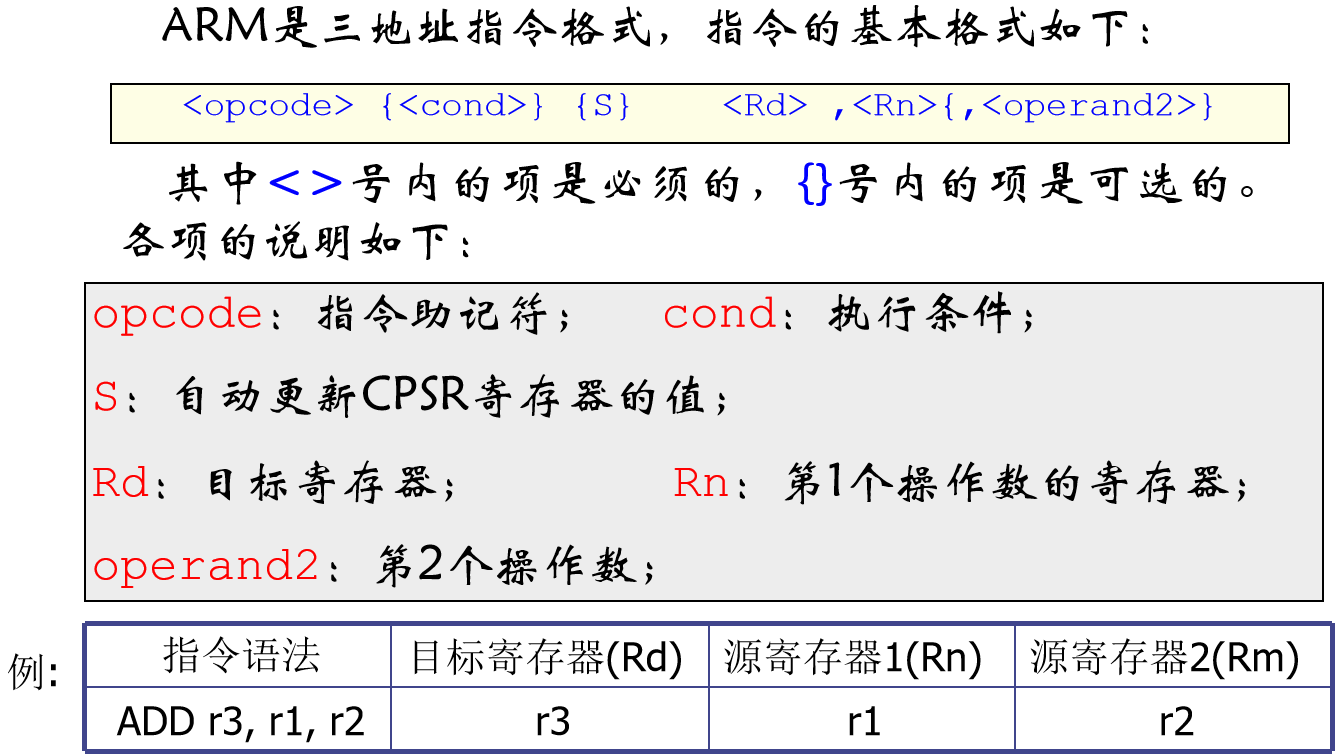

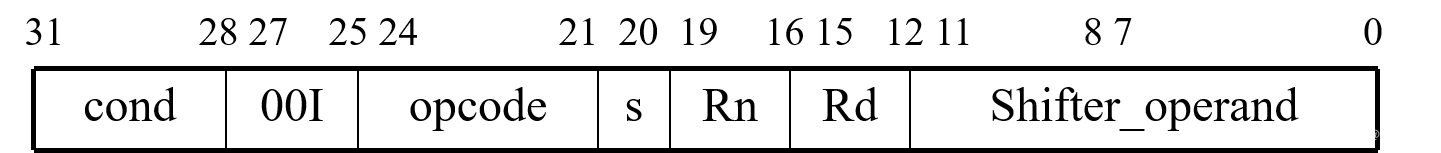

ARM指令格式——三地址指令

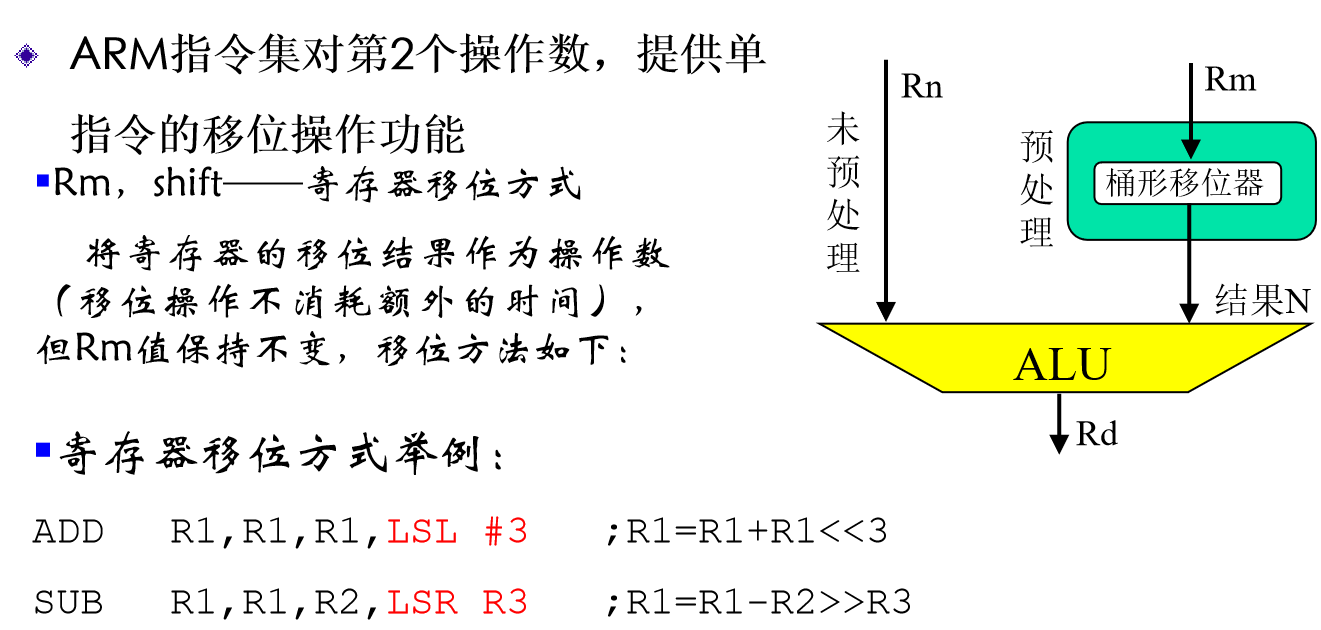

ARM体系结构的主要特征-单指令移位操作

ARM体系结构的主要特征-条件执行

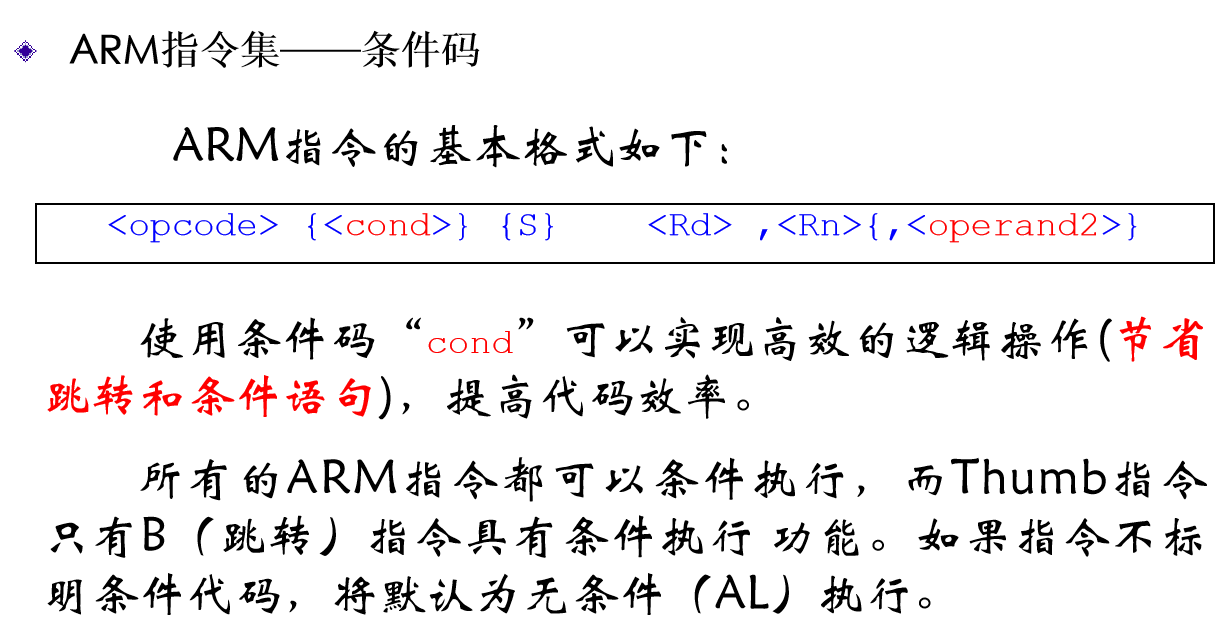

条件码

< shift_op2>形式非常灵活,共有11种形式

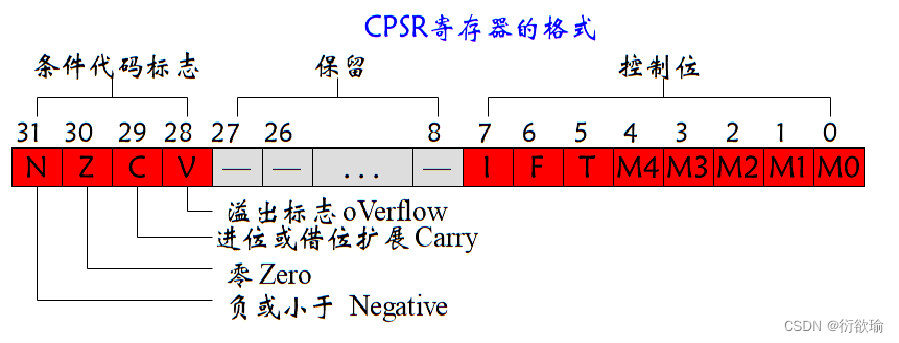

ARM指令集的5种形式的位移操作

-

LSL逻辑左移

-

LSR逻辑右移

-

ASR算术右移

-

ROR循环右移

-

RRX带扩展的循环右移

-

逻辑左移( Logical Shift Left):操作时在移位操作时,用0补足低位;而逻辑右移( Logical Shift Right)移动的方向相反,并用0补足高位

-

算术右移( Arithmetic Shift Right):在移位操作时,根据符号位来补足高位,若原数符号位是1,即当原数为负数时,移位空出的高位都用1补足,反之则用0补足

-

循环右移( ROtate right):可以将数字看作首位相接的“环形”,当最低位被移出后,它会绕到数组的最高位去,继续参与移位操作

-

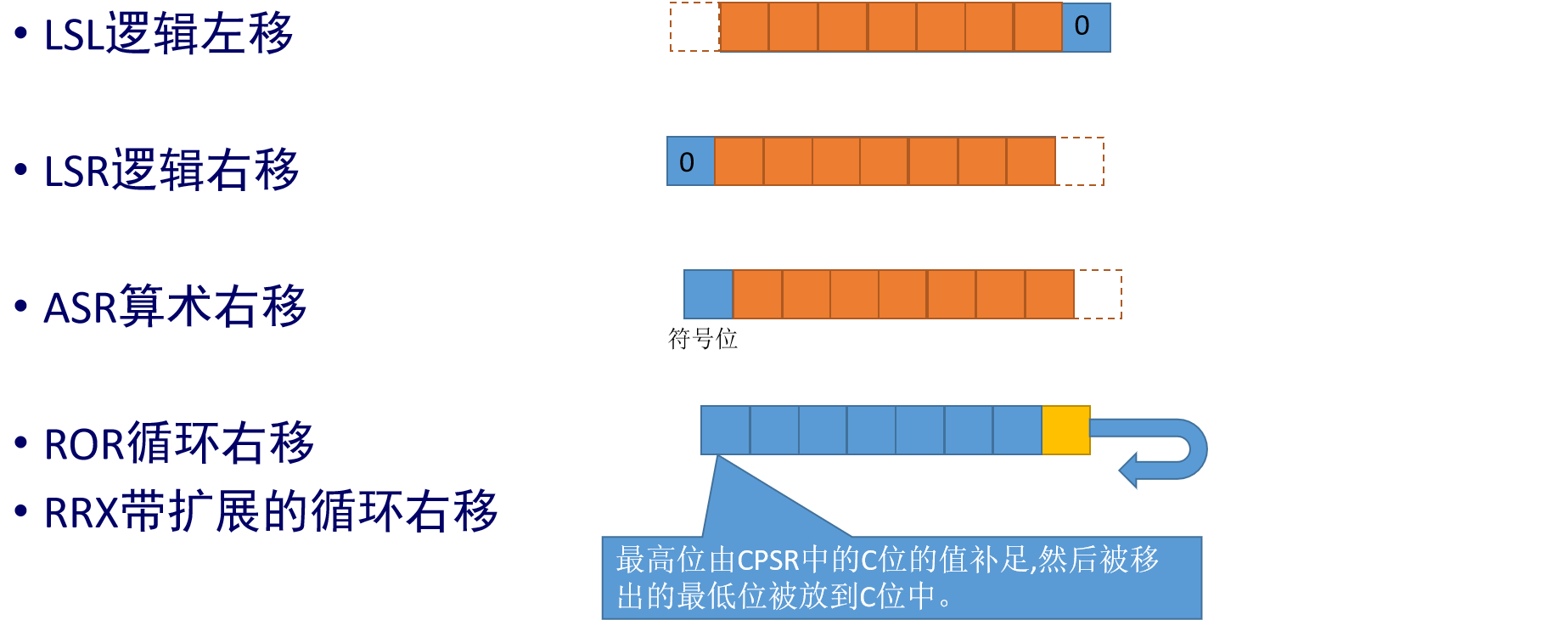

带扩展的循环右移( Rotate right one bit with eXtended):较前面的几种移位方法复杂一些,它需要用到CPSR中的C位。当最低位被向右移出后,最高位由C位的值补足,然后被移出的最低位被放到C位中。

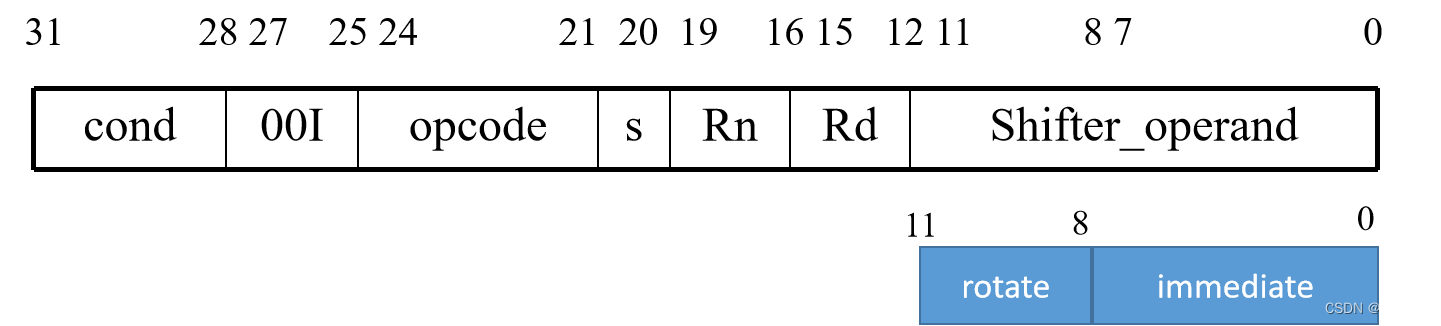

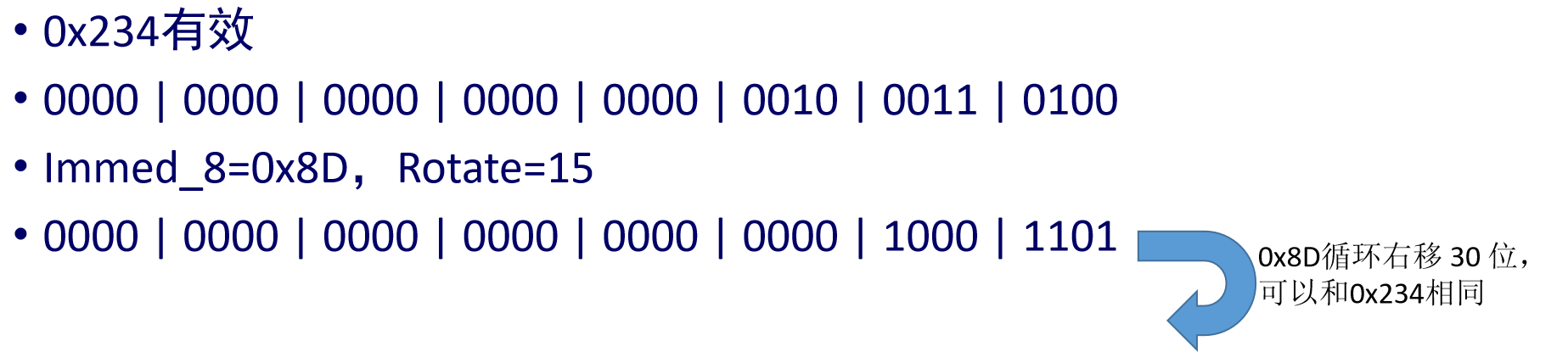

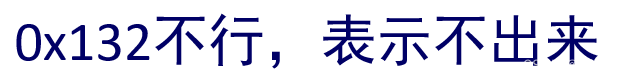

- 立即数# 并不是任意数都是合法的,在立即数寻址中,分配给立即数的空间是12位,8位用于保存一个常数,4位用于保存循环右移基数,而循环右移每次需要移动偶数位,即右移的位数是基数*2

- 假设常数为A,循环右移位数为N,则最后得到的立即数=A循环右移(N*2位)

- 0x1FE不合法

ARM的立即数只能表示有限个32位数

- ARM指令是32位(4字节)的,

- shifter_operand所占的位数:12位。要用一个12位的编码来表示任意的32位数是绝对不可能的(12位数有212 种可能,而32位数有232种)。

- 但是又要用12位的编码来表示32位数,怎么办?

只有在表示数的数量上做限制。通过编码来实现用12位的编码来表示32位数。在12位的shifter_operand中:8位存数据,4位存移位的次数。

4位存移位的次数:4位只有16种可能值,而32位数可以循环移位32次(32种可能),那就只好限制:只能移偶数位(两位两位地移)。这样就解决了能表示的情况是实际情况一半的矛盾。

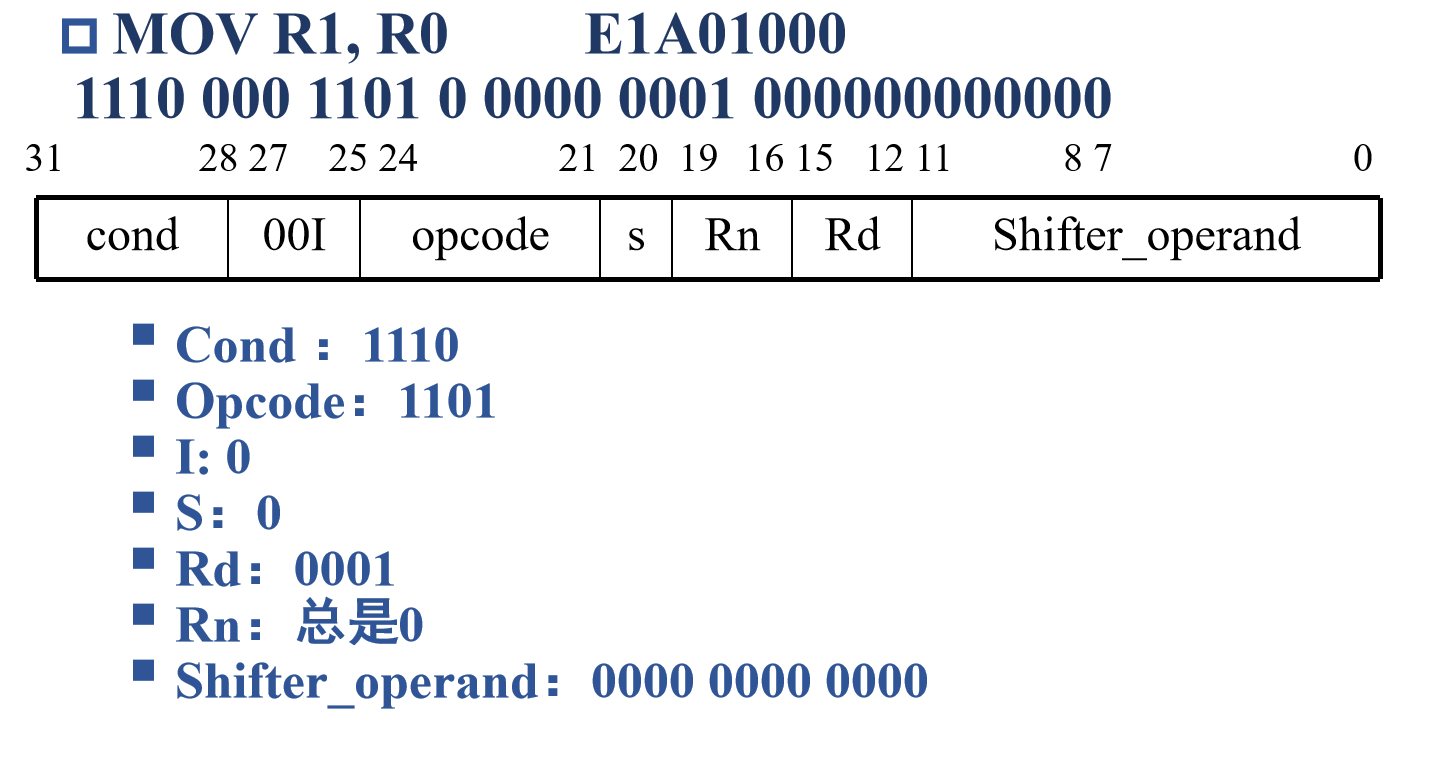

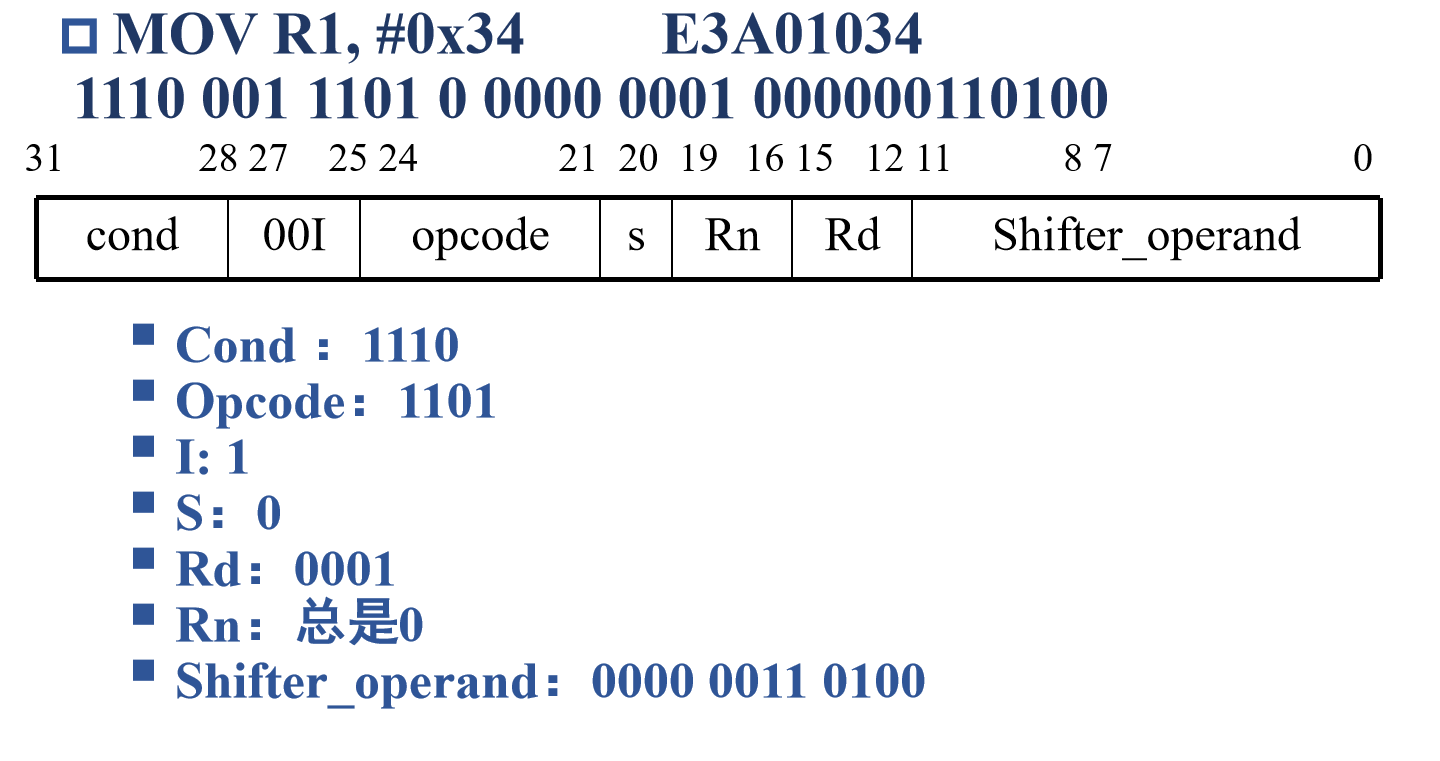

指令格式——数据处理指令

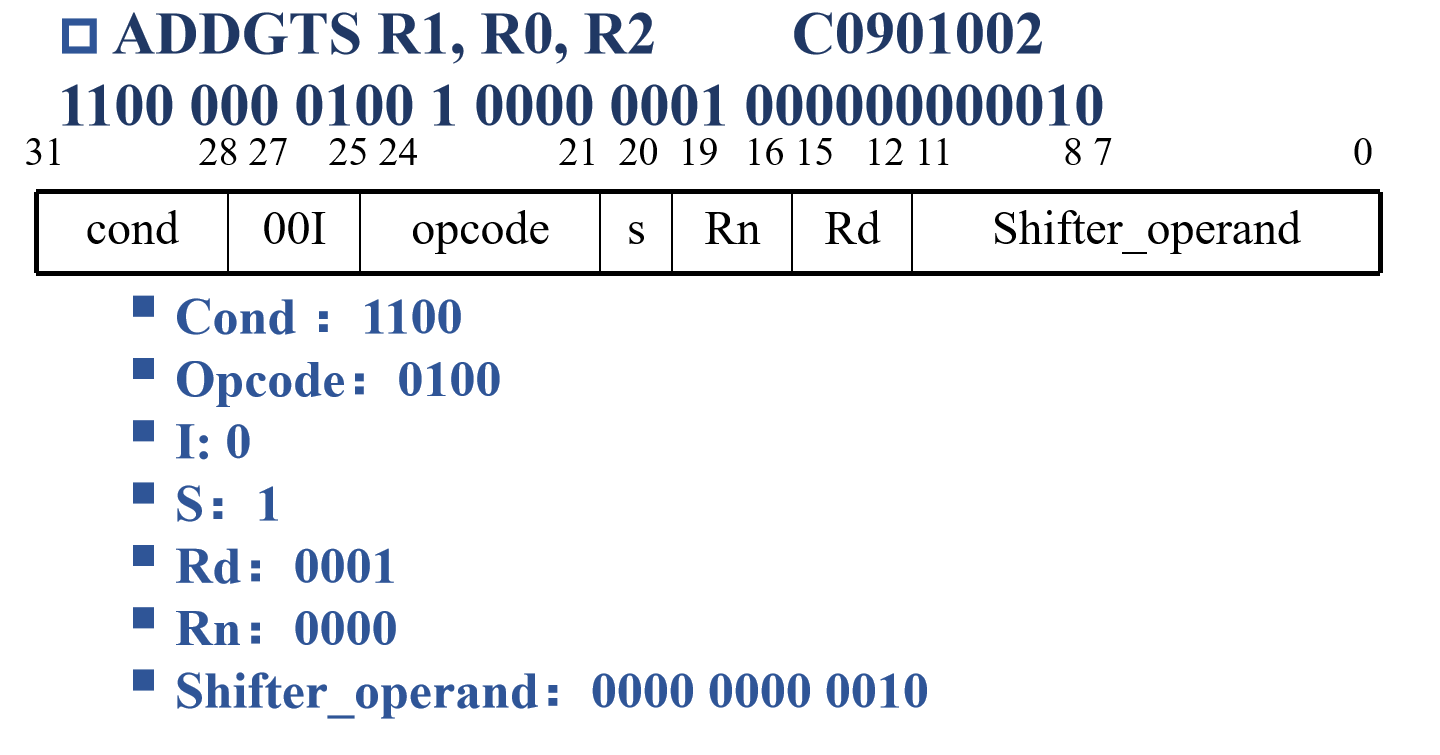

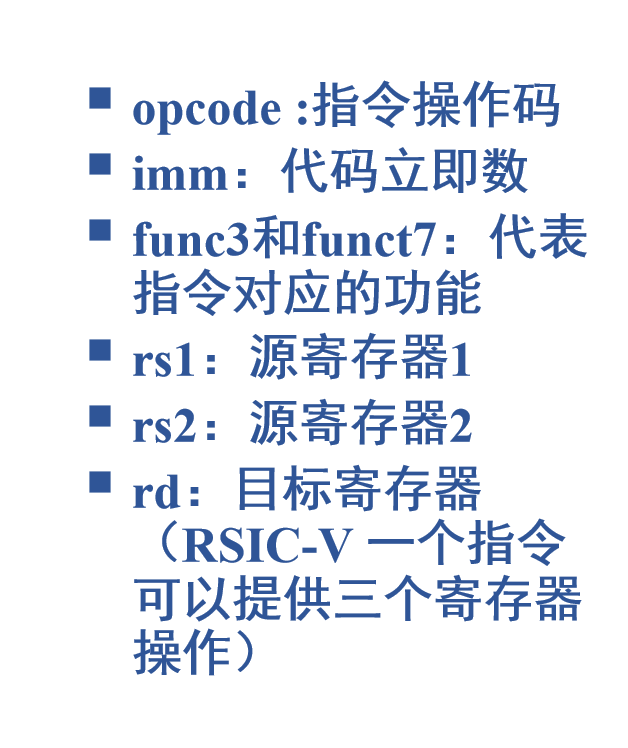

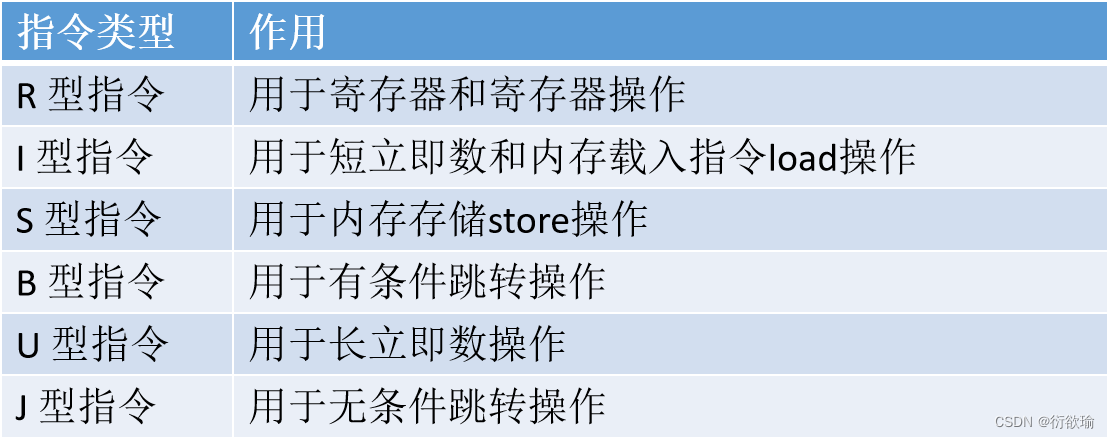

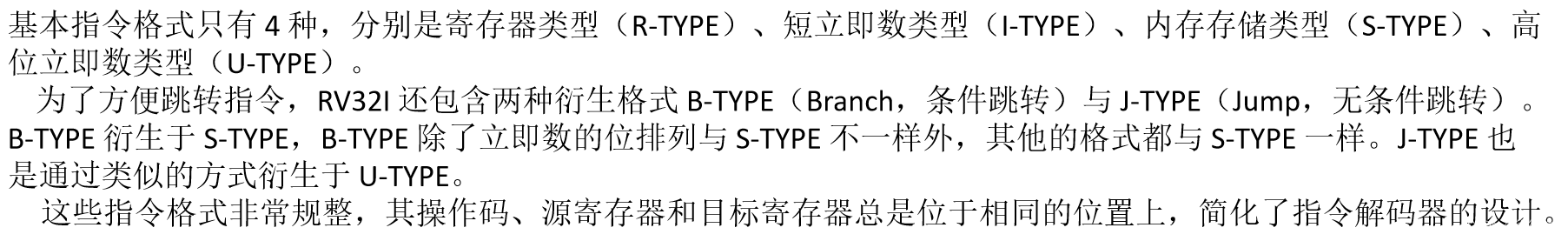

RISC-V 指令格式——共六种指令格式

六种指令格式作用如下:

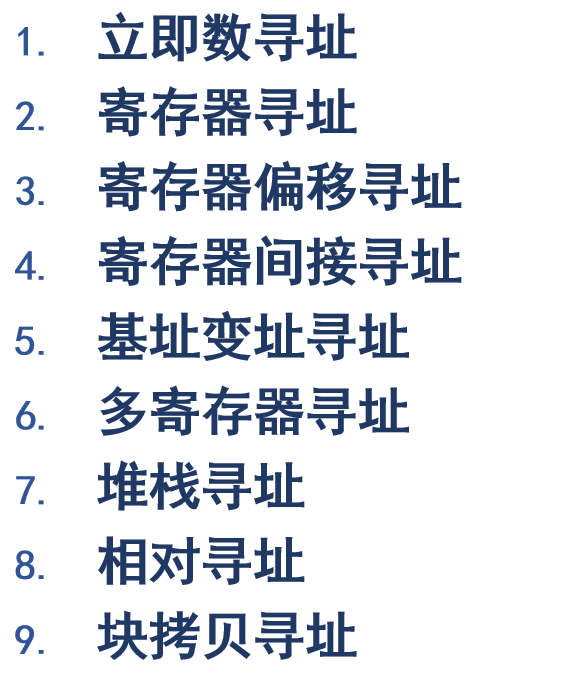

ARM指令的寻址方式

ARM寻址方式

ARM寻址方式——立即数寻址

- 立即寻址也可被称为立即数寻址,读取指令后可以立即得到操作数,而不需要去物理内存得到相应内容。这个给出的操作数叫立即数,它一般以“#”为前缀,“#0x”“#0d”,“#0b”开头的计数用来表示十六进制,十进制和二进制

- ADD R0,R0,#x1 ;R0+1 -> R0

- MOV R1,#0xFF00 ;0xFF00 -> R1

编译结果 E3A01CFF,二进制表示如下:

1110 001 1101 0 0000 0001 110011111111

第二操作数分成两个部分,高4位为移位次数/2,低8位为基数

ARM寻址方式——寄存器寻址

寄存器寻址是一种不需要访问存储器内容的寻址方式,指令中直接指明操作数所在的寄存器,执行时处理器直接访问寄存器获取操作数

MOV R1, R2 ;R2->R1

SUB R0, R1,R2 ;R1-R2 -> R0

ARM寻址方式——寄存器偏移寻址

寄存器偏移寻址是ARM指令特有的一种寻址方式,第2操作数可以在与第1操作数结合之前,进行各种形式的移位操作

ADD R1, R1, R2 , ROR #0x2

; R2循环右移两位后与R1相加,结果放入R1

MOV R1, R0, LSL R2

; R0逻辑左移R2位后放入R1中

ARM寻址方式——寄存器间接寻址

寄存器间接寻址的指令中虽然也是指定寄存器,但并不是直接拿寄存器中的值来进行运算操作,此时寄存器中储存的是地址,处理器需要根据这个地址从存储器中获取操作数。所以寄存器间接寻址是需要进行存储器访问的,所以执行效率比寄存器寻址要慢。

STR R1, [R2];

将R1的值存入以R2内容为地址的存储器中

SWP R1, R1, [R2];

交换以R2为地址的存储器内容和R1内容

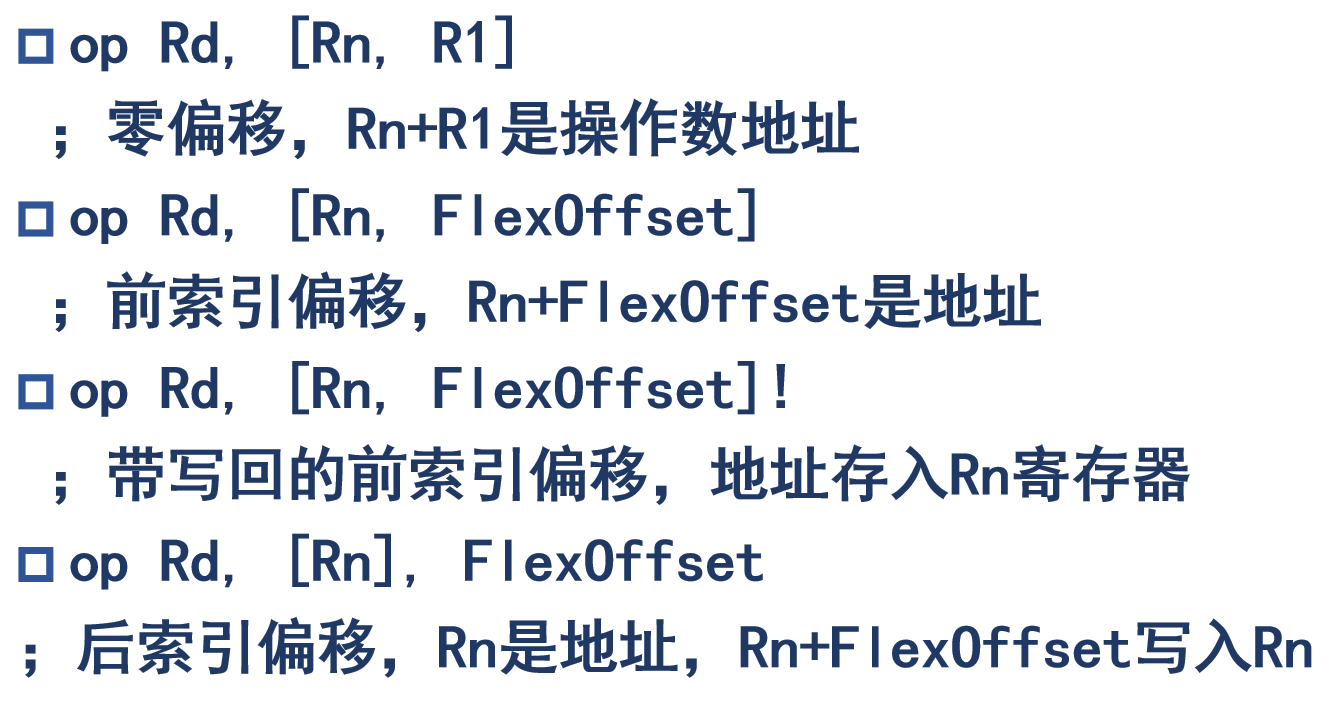

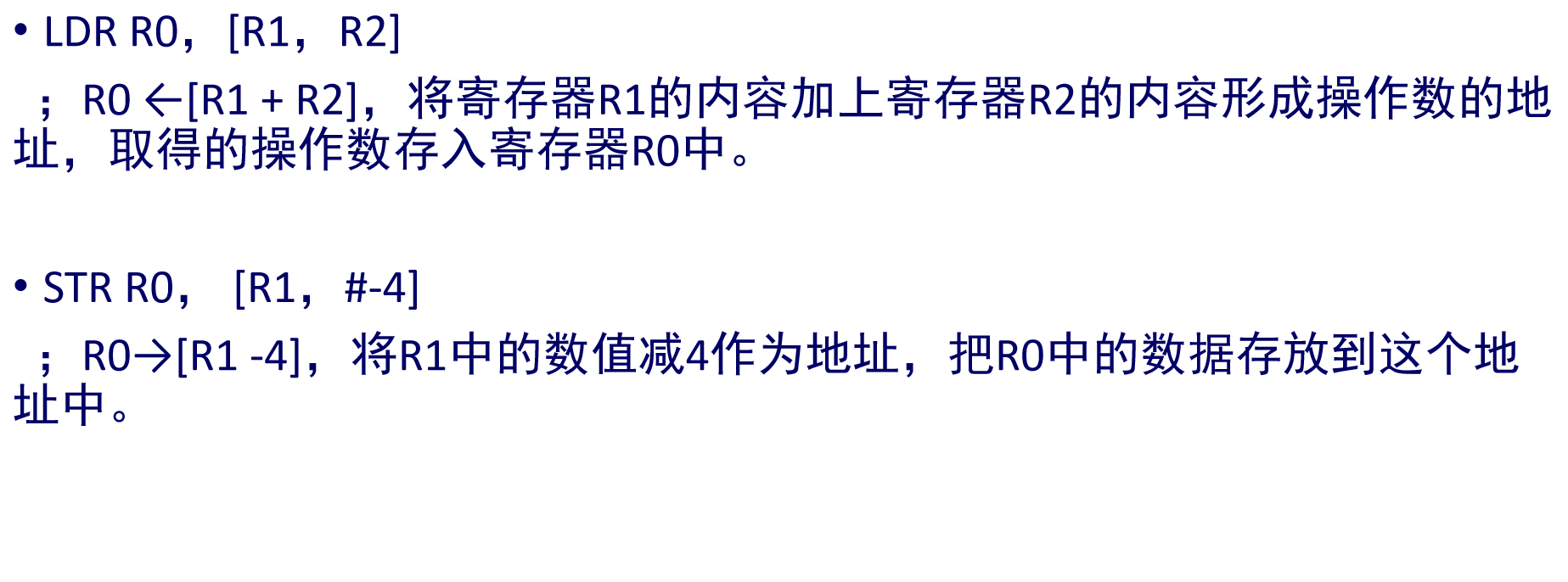

ARM寻址方式——基址变址寻址

基址变址寻址与寄存器间接寻址相似,但此时从寄存器取出的内容需要加上指令所给定的偏移量,这样才构成操作数的有效地址。

变址寻址方式通常用于访问基地址附近的地址单元,常用于查表,数组操作功能部件寄存器访问等

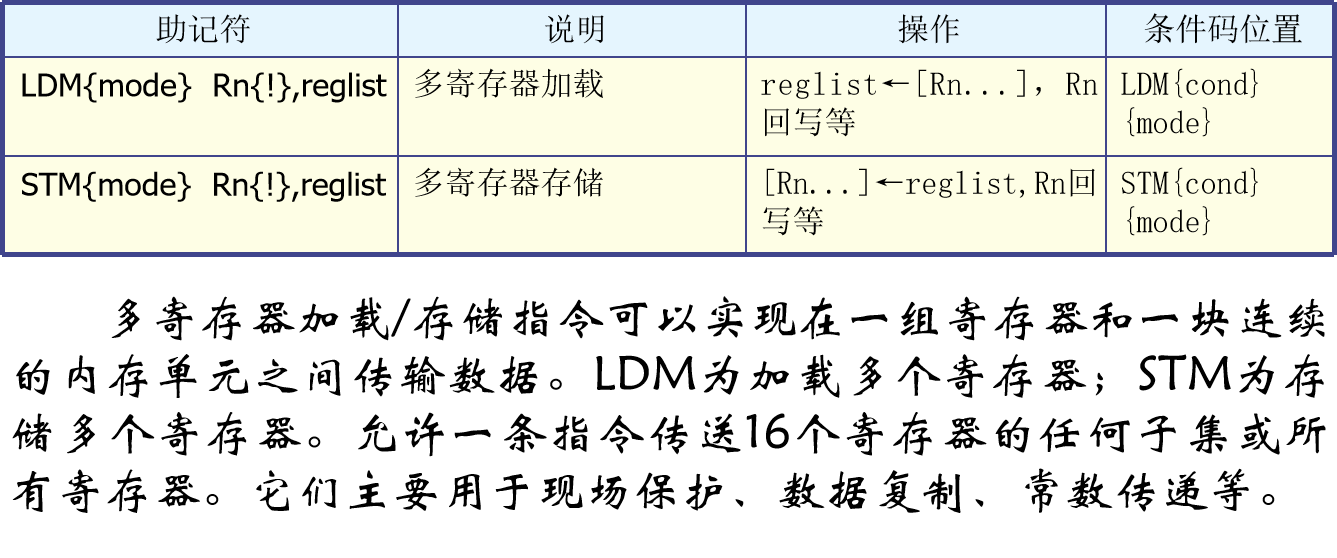

ARM寻址方式——多寄存器寻址

一次完成多个寄存器值的传送

LDMIA R0, {R1, R2, R3, R4, R5} ; R1<- R0, R2<- R0+4, …, R5<-R0+16

后缀IA表示在每次执行完加载/存储操作后,R0按字长度增加,因此,指令可将连续存储单元的值传送到多个通用寄存器(最多16个)。

STMIA R0, {R2-R5, R7}; R0<-R2, R0+4<-R3, … , R0+12<-R5, R0+16<-R7

连续的寄存器可用“-”连接,不的寄存器用“,”分隔

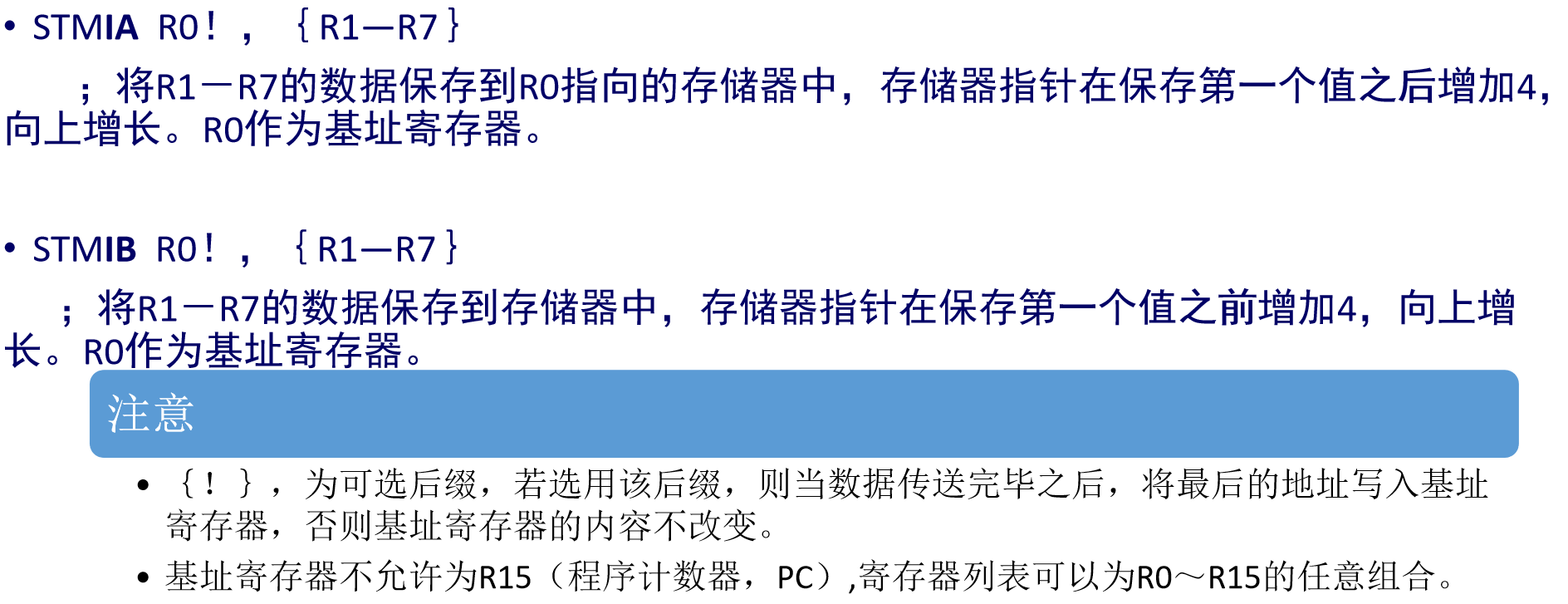

ARM存储器访问指令——多寄存器存取

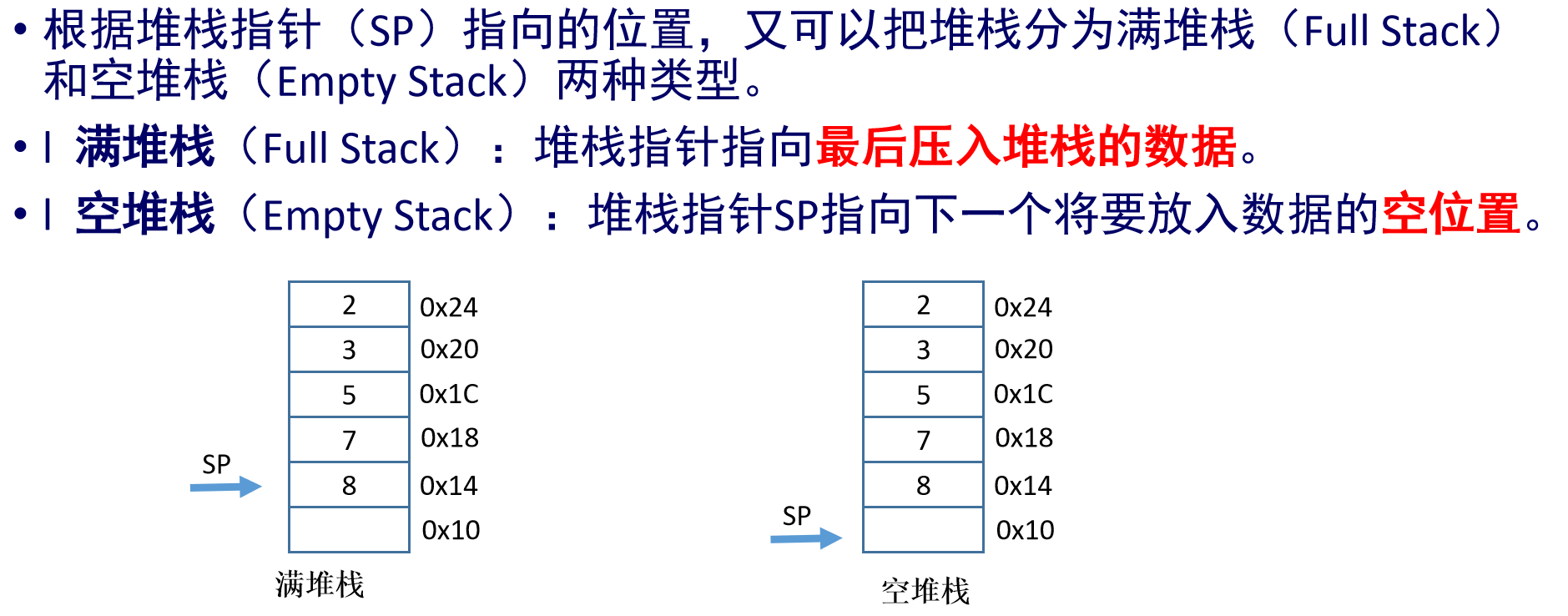

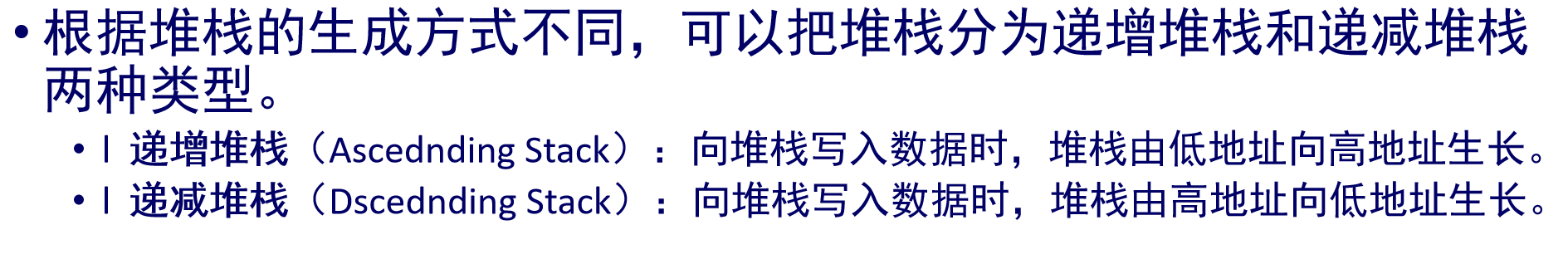

ARM寻址方式——堆栈寻址

- 堆栈是一个后进先出的数据结构,使用堆栈指针(Stack Pointer, SP)指示当前的操作位置,堆栈指针总是指向栈顶。这个指针需要用一个专门的寄存器来存放,这个寄存器一般是R13

- STMFD SP!, {R1-R7, LR} ; 将R1-R7,LR存放到堆栈中,这条指令一般用来保护现场

ARM寻址方式——相对寻址

相对寻址是一种特殊的基址寻址,特殊性是它把程序计数器PC中的当前值作为基地址,语句中的地址标号作为偏移量,将两者相加之后得到操作数的地址。

BL Label ;

转跳到Label标签处

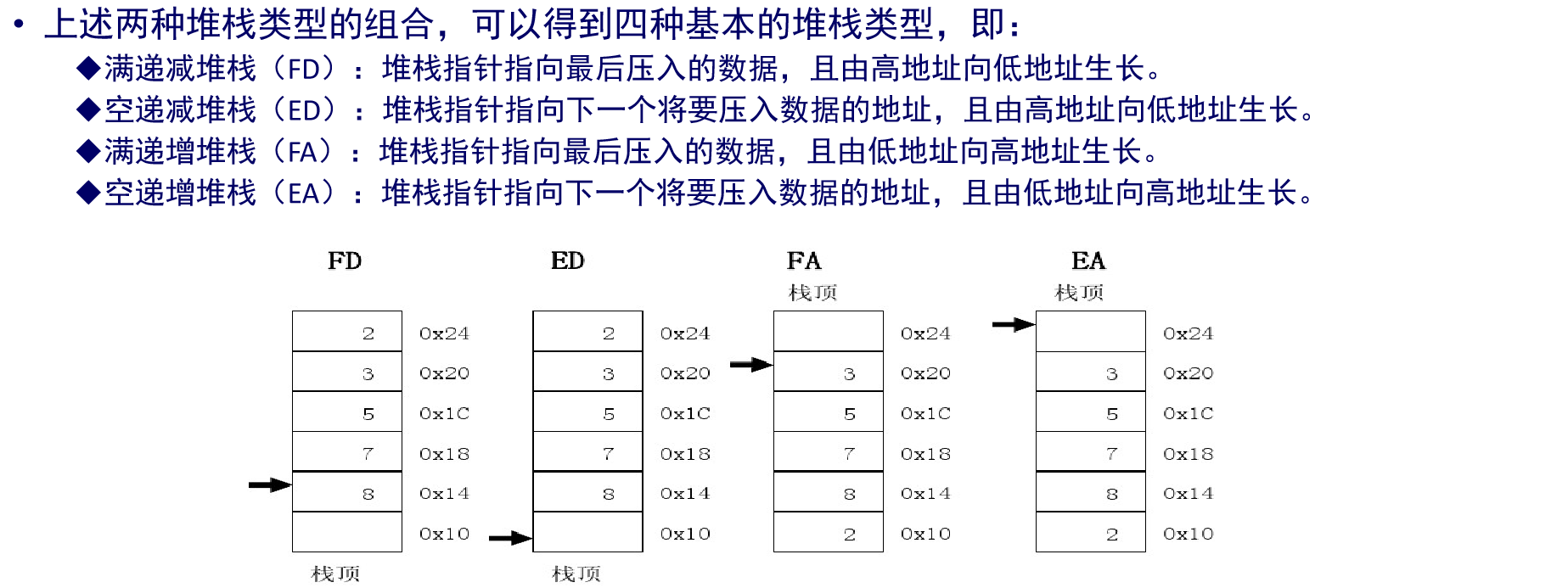

ARM寻址方式——块拷贝寻址

- 块拷贝寻址用于寄存器数据的批量复制,它实现从由基址寄存器所指示的一片连续存储器到寄存器列表所指示的多个寄存器传送数据。块拷贝寻址与堆栈寻址有所类似。

- 两者的区别在于:堆栈寻址中数据的存取是面向堆栈的,块拷贝寻址中数据的存取是面向寄存器指向的存储单元的。

- 在块拷贝寻址方式中,基址寄存器传送一个数据后有4种增长方式,即:

- IA:每次传送后地址增加4;(Increment After Operating)

- IB:每次传送前的地址增加4;(Increment Before Operating)

- DA:每次传送后地址减少4;(Decrement After Operating)

- DB:每次传送前地址减少4。(Decrement Before Operating)

对于32位的ARM指令,每次地址的增加和减少的单位都是4 个字节单位。

计算机怎么处理指令

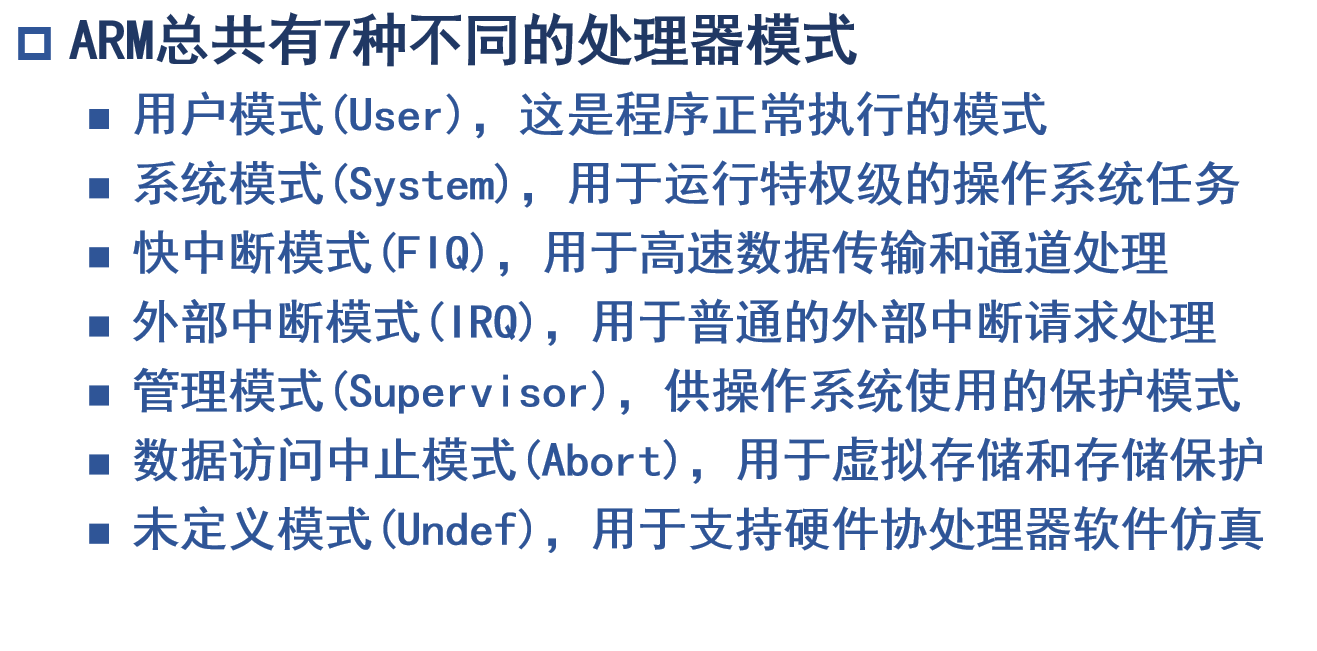

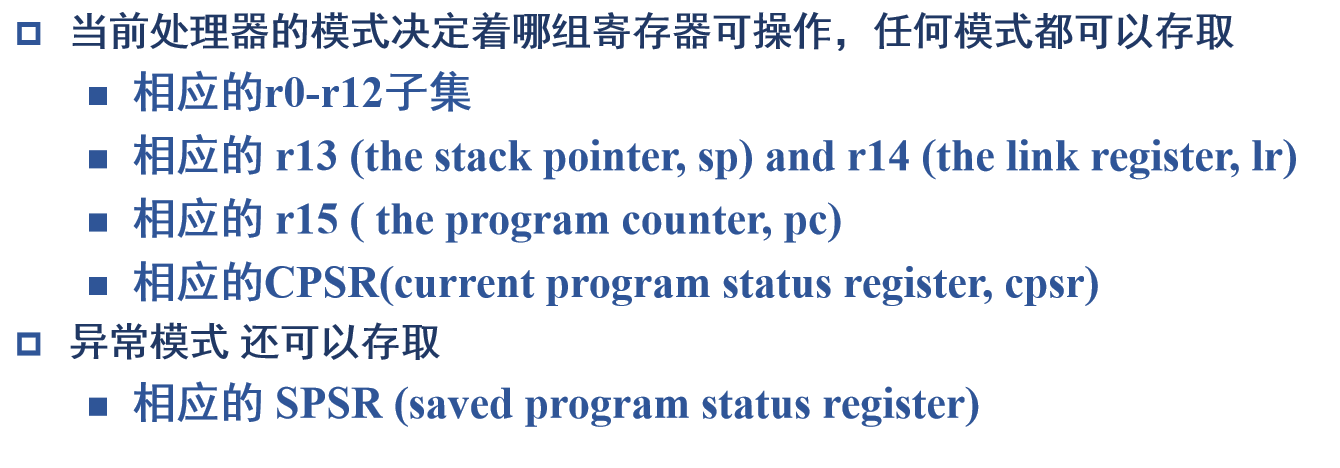

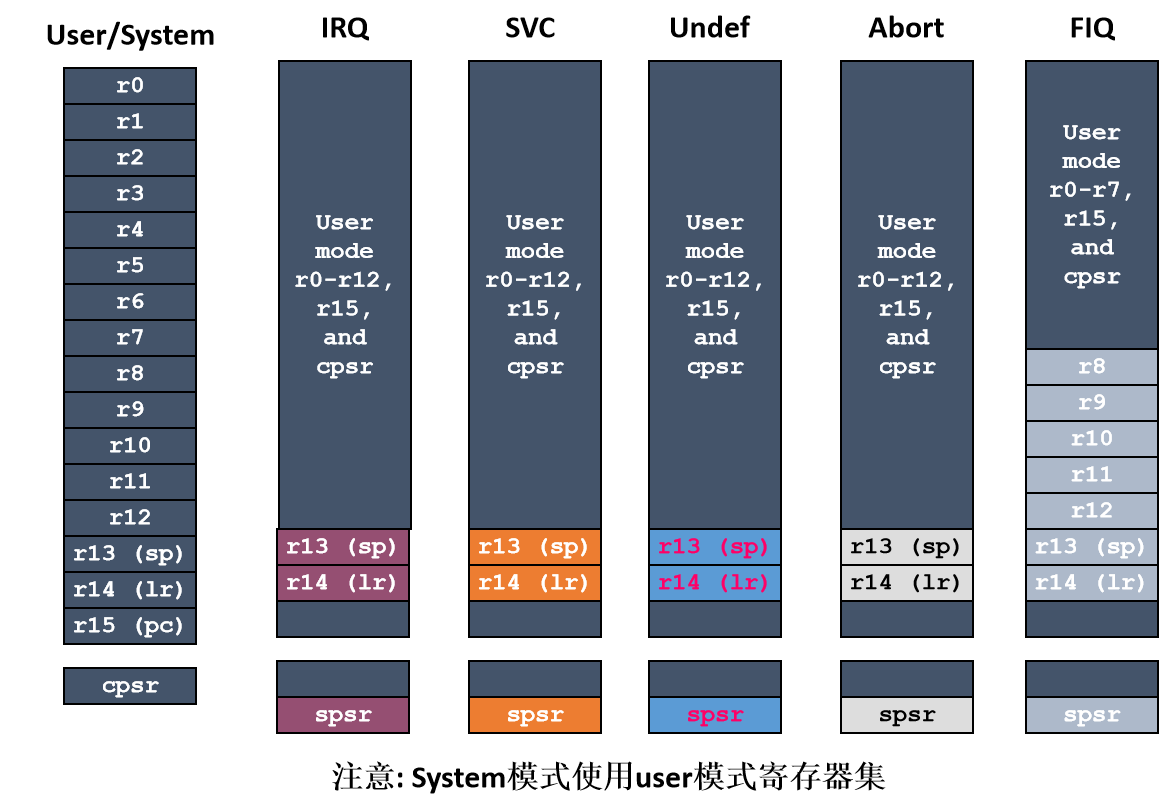

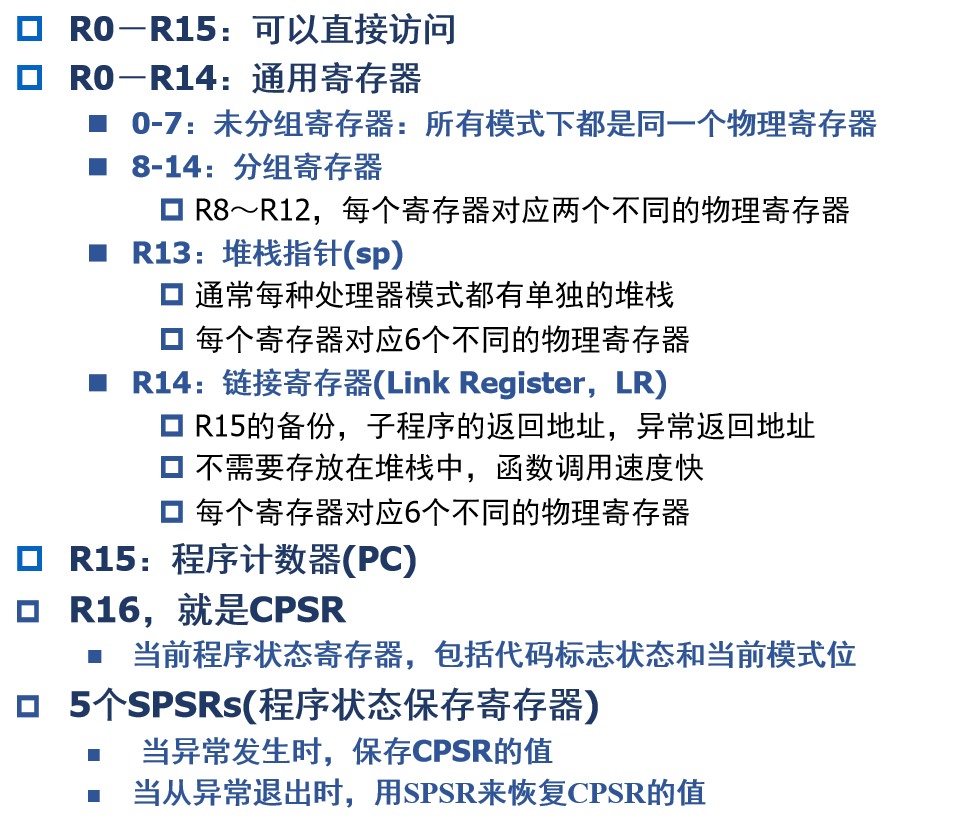

ARM寄存器组织

由于用户模式和系统模式不属于异常模式,所以不需要SPSR

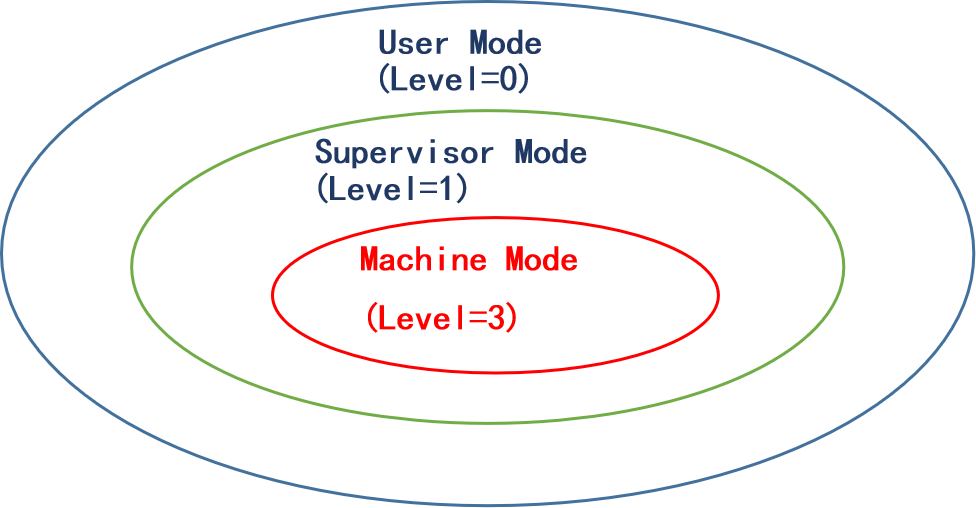

特权层级

RISC-V 处理器中的软件代码都是在硬件线程上运行的。为了加强对操作系统和信息安全的支持,RISC-V 替硬件线程(Hardware Thread,HART)定义了 3 种工作模式:机器模式、超级用户模式(Supervisor Mode,S-Mode)和普通用户模式(User Mode,U-Mode)。每种模式分别对应一个特权层级(Privilege Levels)。其中机器模式的特权层级最高,而普通用户模式的特权层级最低。在高特权层级运行的代码比在低特权层级的代码拥有更多的权限,受到的约束也比低特权层级的代码要少。

在 RISC-V 的术语中,每个处理器核可以包含多个硬件线程,称作硬件线程。每个 HART 都有自己的程序计数器和寄存器空间,独立顺序运行指令。不同的 HART 会共享同一个内存地址空间,从这一点上来说,HART 和 Intel 处理器中的超线程(Hyper Thread)非常类似。在 RISC-V 中,当这些不同的 HART 需要做内存访问同步时,需要显式地(Explicitly)使用 FENCE 指令来同步数据。

在处理器设计时,机器模式是强迫要求实现的。其他的两个模式,处理器设计者则可以选择性地加以实现。一般来说,小规模的嵌入式系统只需要机器模式就可以了,而对信息安全有特殊要求的系统,则可能需要机器模式加普通用户模式。运行类似 UNIX 这样大型操作系统的处理器,则需要实现以上所有的模式。

ARM9系列处理器共有37个物理寄存器

RSIC-V 寄存器说明

在RISC-V 的规范里面定义了32 个通用寄存器。其中31个是常规寄存器,1个恒为0值的x0寄存器。

0值寄存器是为了满足汇编语言程序员和编译器编写者的使用需要,他们可以使用x0寄存器作为操作数,来完成功能相同的操作。

- RISC-V 的官方标准主要分成两部分:用户指令集(User-Level Instruction Set Architecture)与特权架构(Privileged Architecture)。

- 在 RISC-V 的特权架构部分还对控制与状态寄存器(Control Status Register,

CSR)做了定义,并单独分配了 12 位的地址空间。在这 12 位地址当中,最高的两位 [11:10] 被用来指示寄存器的读写权限。地址位 [9 :8] 表示有权访问该寄存器的最低特权层级。在用户指令集中,则专门定义了 Zicsr 指令集扩展来对 CSR 进行操作。

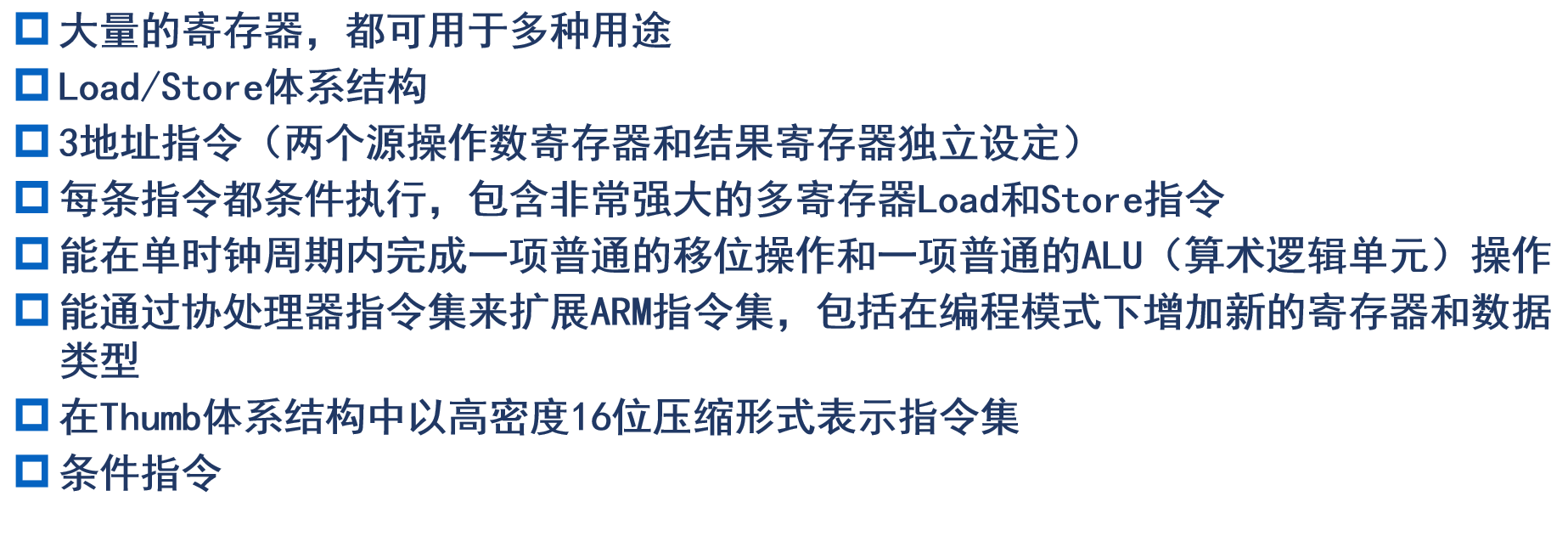

ARM体系主要特征

编辑于2022/12/20日;

距离考试还有三天。