NPU架构与算力分析

参考文献链接

https://mp.weixin.qq.com/s/xc_-5SmtWLGQuX3w-ptPfA

https://mp.weixin.qq.com/s/samT5gYMsrwBguvMTHbS9Q

https://mp.weixin.qq.com/s/uJkAhJzUpGeyYvO92p4-Ow

https://mp.weixin.qq.com/s/BRY2ExcWztl7vf69UyNAUw

https://mp.weixin.qq.com/s/BKzNwfVe-Bsoh_2090HHcQ

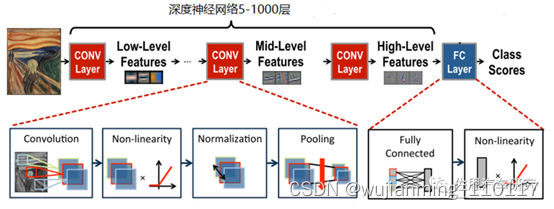

芯片的NPU算力

算力简单说就是计算能力,按《中国算力发展指数白皮书》中的定义算力是设备通过处理数据,实现特定结果输出的计算能力。2018年诺贝尔经济学奖获得者William D. Nordhau滤《计算过程》一文中提出:“算力是设备根据内部每秒可处理的信息数据量"。算力实现的核心是CPU、GPU等各类计算芯片,并由计算机、服务器、高性能计多集群和各类智能终端等承载,海量数据处理和各种数字化应用都离不开算力的加工和计算。

以AI为例,CPU、GPU、DSP等都可以运行,但是还是有专用的AI芯片,为什么呢?也跟算力有关。

• CPU(central processing unit)是通用处理器,可以处理一切事物,就像一把瑞士军刀,哪方面都能做但都不是专业高效的。

• GPU(Graphics Processing Unit)是专门用来处理图形图像相关的处理器,与CPU相比GPU处理的数据类型单一,因为运算与AI相似以及容易组成大的集群,所以进行AI运算时在性能、功耗等很多方面远远优于CPU,经常被拿来处理AI运算。

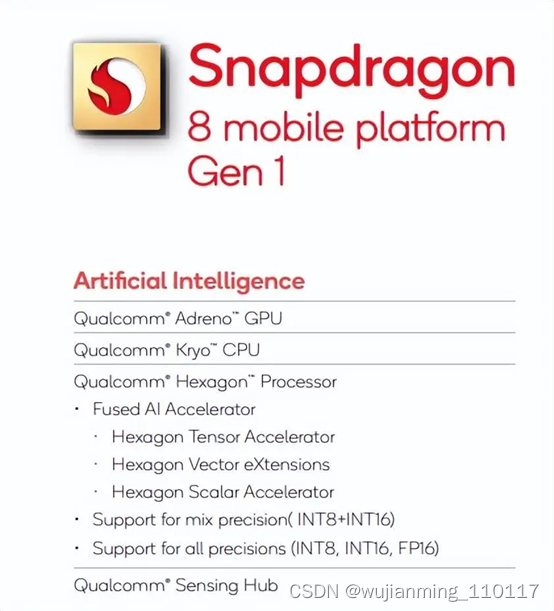

• DSP(digital signal processor),是专门用来处理数字信号的,DSP与GPU情况相似,也会被拿来做AI运算,比如高通的手机SoC。

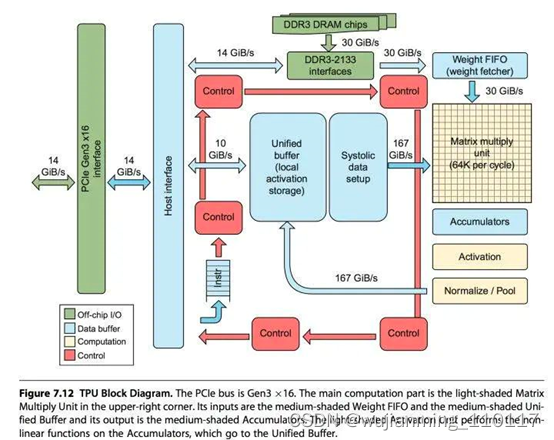

AI芯片是专门用来处理AI相关运算的芯片,这与CPU、GPU、DSP的“兼职”做AI运算不同,即便是最高效的GPU与AI芯片相比也是有差距的,AI芯片在时延、性能、功耗、能效比等方面全面的超过上面提到的各种处理器。以知名的谷歌的TPU为例,如下图所示,TPU的主要计算资源为:

• Matrix Multiply Unit:矩阵乘单元

• Accumulators:存储矩阵乘加输出的中间结果

• Activation:激活单元

• Unified Buffer:统一缓存

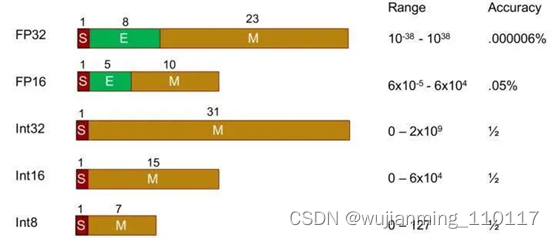

当时谷歌资深硬件工程师Norman Jouppi表示,谷歌的专用机器学习芯片TPU处理速度要比GPU和CPU快15-30倍(和TPU对比的是英特尔Haswell CPU以及Nvidia Tesla K80 GPU),而在能效上,TPU更是提升了30到80倍,这并不意外,因为TPU运行的CNN运算主要就是矩阵乘,专用芯片好处就是这样。其实对于对于AI来说,又分为训练和推理,训练就像AlphaGo一样需要学很多的棋谱(数据),通常采用数据精度为FP32。

• FP32(Full Precise Float 32,单精度)占用4个字节,共32bit,

• FP16(float,半精度)占用2个字节,共16bit,

• INT8,占用1个字节,也就是8bit,精度更低,因此数据量小、能耗低,计算速度相对更快,更符合端侧运算的特点。

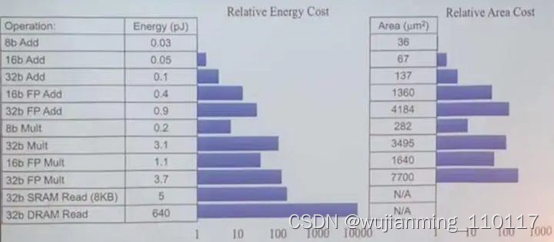

不同精度计算消耗的Bill Dally 在ACMMM 2017 上的《Efficient Methods and Hardware for Deep Learning》演讲中曾经列过一个不同精度计算的消耗能量和硅片面积对比,可以看出一个FP32精度的乘法运算消耗是INT8精度的18.5倍。因此同样一块芯片运算INT8的数据与运算FP32的数据在同一时间内运算次数相差很多,也就是说不同精度OPS不同,算力不同。

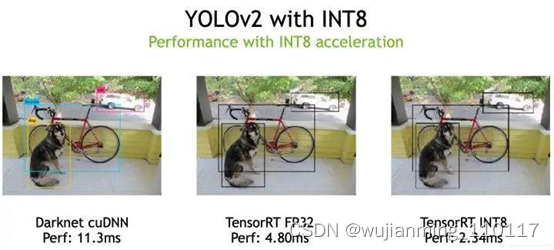

这样的精度如果运行在手机等终端上是不行的,所以在在手机、汽车、安防等终端领域,都是执行模型的推理,现有的推理芯片有很多,比如特斯拉FSD、寒武纪NPU、地平线BPU、OPPO的马里亚纳、荣耀使用的AI-ISP等。与训练阶段不同,在推理的时候,精度要求并不高,以知名的对象监测算法YOLO(You Only Look Once)为例,FP32的精度与INT8的精度相差甚小,但是因为模型更小,神经网络模型的推理速度却大幅加快。这在终端上很重要,比如在汽车的自动驾驶上,如果推理计算的数据慢了会造成巨大的影响。

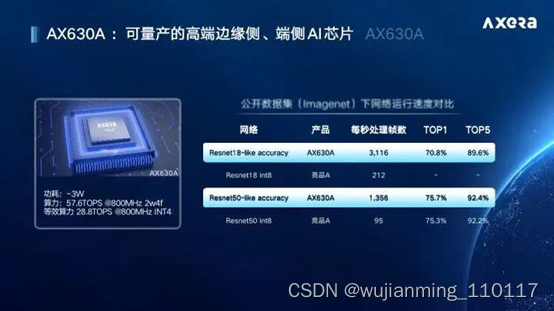

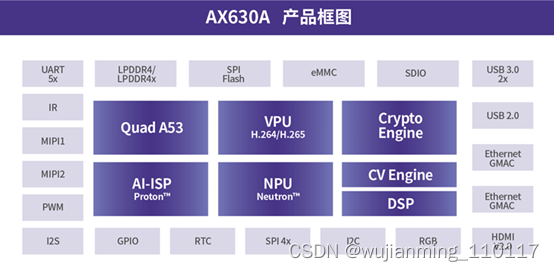

当然在安防等对精度要求更低的地方,还有很多采用的是INT4精度的,比如爱芯科技的AX630A在INT4精度下的算力达到了28.8TOPS,可应用于智能盒子,运动相机,智能加速卡,工业摄像头等领域,如果是INT8精度就是7.2TOPS(这里要注意的是并不是所有的AI芯片支持不同精度下的算力转换,这需要硬件实现上的支持)

在终端芯片上,厂商宣称的算力有时候甚至不是AI芯片的算力,因为CPU、GPU、DSP都可以进行AI的运算,所以在宣传算力的时候采用的是CPU算力 + GPU算力 + DSP算力的算法,虽然这些处理单元都在一颗芯片上但是在实际使用上不可能同时进行AI运算。

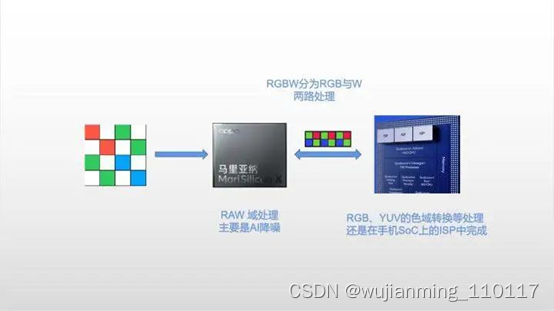

因为一些手机芯片的AI处理能力不足,以及处理流程在YUV域较为靠后,所以像OPPO等厂商开始推出马里亚纳这样的AI芯片,18TOPS并前置在手机SOC之前在RAW域进行 AI降噪的处理,可以大幅的提升夜景拍摄能力,保留更多细节。

荣耀采用的AI-ISP也是一样的道理,其实这类芯片本质上是一个处理AI运算的NPU,从业务上来说更好的叫法是Pre-ISP,并不是真正的ISP芯片。

打破内存墙、功耗墙,国产芯片AI-NPU

随着5G的落地,物联网的成本效益显现,工业数字化、城市智慧化等演进趋势日益明显,越来越多的企业和城市开始在物联网创新中加入数字孪生这种颠覆性的概念,来提高生产力和生产效率、降低成本,加速新型智慧城市的建设。值得一提的是,数字孪生技术已被写进国家“十四五”规划,为数字孪生城市建设提供国家战略指引。

关于数字孪生,可以举个例子,前几年亚马逊和京东推过的无人零售概念型实体店,将线下零售店变成了线上淘宝店,人们去店里购物前只需打开APP,在设置中完成刷脸登录,脸部认证成功后,在刷脸开门时即可自动关联账户,购物后不用排队手动结账,只靠刷脸即可离开。看似无人管理,但背后却是人工智能的全程跟踪,消费者的一举一动都被摄像头捕捉了下来,比如把什么商品拿起来看了又看,意味着对这个商品很有兴趣,但是出于某种顾虑又没买,最终买了另外的商品,这样的数据会被抓取下来,进行深层次的分析,形成基础数据库,之后就可以根据所有的购物记录和消费习惯进行周期性的推送等。

通过这个例子,可以看到将物理世界数字化带来的便利性。而视觉是人类感知世界的一个重要手段。人类进入智能社会的基础是数字化,感知是将物理世界数字化的前提,而前端视觉感知的种类、数量和质量决定了这个社会智能化程度的高低。由此可见,智能化未来的基础是“感知 + 计算”,AI视觉在智能化的进程中会起到非常关键的作用,具备非常广阔的应用前景。有行业分析师认为,数字孪生技术即将超越制造业,进入物联网、人工智能和数据分析等整合领域。这也就是选择了这个创业方向的原因。

而视觉芯片作为物理世界到数字孪生世界最重要的入口,正受到广泛关注,尤其是能够对物理世界进行80%-90%还原的AI视觉感知芯片。

那么什么是AI视觉感知芯片呢?从需求端的角度来看,AI视觉感知芯片需要具备两大功能:一是看得清,二是看得懂,其中AI-ISP负责的就是看得清,AI-NPU负责看得懂。

图 | AI视觉芯片的技术特点

事实上,从广义上来讲,在人工智能应用中能实现AI加速的芯片都可以被称为AI芯片,而其中用来提高AI算法运行效率的模块往往被称为NPU(神经网络处理器)。目前,使用NPU加速的AI视觉芯片已被广泛地应用于大数据、智能驾驶和图像处理领域。

根据IDC发布的最新数据显示,2021年加速服务器市场规模达到53.9亿美元,同比增长68.6%。其中,GPU服务器以90%的市场份额占据主导地位,ASIC和FPGA等非GPU加速服务器以43.8%的增速占有了11.6%的市场份额,达到6.3亿美元。这意味着神经网络处理器NPU的应用已走出早期试点阶段,正成为人工智能业务中的关键需求。所以,今天就来聊聊负责“看得更清”以及“看得懂”的AI-NPU。

为什么会说看得更清和AI-NPU也有关系呢?从人们直观感受的角度出发,“看得清”很好理解,比如在夜间想要把东西看得比较清楚,但传统摄像头拍摄出的图片往往会出现过曝、色彩细节被淹没的现象,同时走动的人和远处的建筑物周围会布满噪点。那么,在类似这种情况下,如何才能更好地实现“看得清”呢?事实上,视觉芯片要“看得清”离不开的正是AI-NPU大算力的支撑。

图 | 夜间视频效果对比图

以智慧城市为例,已经使用500万像素的摄像头在做智能分析。传统的视频画质的改善使用的是传统的ISP技术,在暗光的场景下,会有大量的噪声,使用AI-ISP可以解决此问题,在暗光场景下依然可以给出清晰的画面,但是使用AI-ISP的技术,就必须用AI算法全分辨率、全帧率地对视频进行处理,而不能采用投机取巧的缩小分辨率或者跳帧的方式进行,因为人眼对于画质的闪烁非常敏感。而500万像素的视频码流,要做到全分辨率、全帧率的处理,就会对NPU的算力提出非常高的要求。

在智能分析的场景中,比如车辆检测和车牌识别的应用,目前常见的是采用500万的摄像头来录制30fps帧率的视频,然后每3/5帧做一次检测,在做检测的时候分辨率降到720P的方法,对于在视频画面中远处的车牌就会识别不出来,对于高速行驶的车辆就可能会漏检,解决方法也是尽量采用全分辨率、更高帧率检测的方式进行处理,而这种做法对NPU的算力同样提出了非常高的要求。

此外,如同前面提到的,除了看得清之外,还需要看得懂,所谓看得懂就是要做智能分析,要做智能分析也需要AI-NPU大算力的支撑,可以从两个角度来看这个问题。

首先,知道AI本身是一个提高效率的工具,最终还是要落入到场景里面去,这也就是早期的AI+和最近的+AI的概念。那么,当AI落到行业里面去时,能做些什么事情呢?事实上,AI能做的事情很多,比如可以把一些行业的专家系统用神经网络的方式做一些替代,这就相当于要把这样一个“专家”装到AI芯片里,这个专家系统要足够聪明,对应的就是一个比较聪明或者比较大的网络,网络比较大就相当于脑容量比较大,能够维持存储更多的权重值,这就会对NPU算力提出很高的要求。

其次,从部署的角度来看,目前模型的训练大都是在大算力的Server上跑出来的,而部署是在算力有限的端侧设备上,只有将模型或算法的计算量降到端侧能跑起来的程度,才能在应用侧更好的落地。因此需要模型压缩的过程,而模型压缩对技术人员的技术要求很高。如果端侧的算力比较高,其实这个过程是可以缩短的。这类似于做嵌入式软件开发的过程,早期受限于算力瓶颈,为了能够跑更多的功能,需要非常认真地来压榨硬件的性能,所以用汇编来写程序,但如果算力比较高,就可以用C语言来做开发。换言之,用一部分算力来换取开发效率的提升、AI落地的加速是可行的,但这种做法又反过来提高了对NPU算力的要求。开发难度是非常大的

众所周知,算力是NPU性能的重要指标,然而很多早期AI芯片的算力其实是标称值,真正使用时并不能达到标称的性能。比如号称1T的算力,结果实际跑下来发现只能用到200G或者是3~400G的水平。所以,大家现在使用更加实用的FPS/W或FPS/$作为衡量先进算法在计算平台上运行效率的评价指标。

图 | AI-NPU的设计难点和驱动力

在自动驾驶领域,2017年特斯拉发布FSD芯片时,马斯克用FSD和此前在特斯拉上应用的英伟达Drive PX2相比,表示:“从算力的角度来看,FSD是Drive PX2的3倍,但在执行自动驾驶任务时,其FPS是后者的21倍。”

在AI视觉芯片领域,爱芯元智发布的第一款高性能、低功耗的人工智能视觉处理器芯片AX630A,在公开数据集下的不同神经网络运行速度对比,每秒处理帧数分别为3116和1356,远超其他同类芯片产品,且功耗仅约3W。

图 | AX630A产品框图

到底是什么拉开了这些NPU利用率的差距?这背后其实是内存墙和功耗墙的问题。所谓内存墙就是当通过堆MAC单元来拉高算力指标的同时,数据带宽一定要跟上,否则数据供应能力不足,就会带来MAC单元不断等待数据的现象,处理性能就会下降。而功耗墙的问题主要来自两个方面:MAC单元和DDR。当通过堆MAC单元来拉高算力指标时,MAC单元本身的耗电总量会提升,同时还需要高带宽的支撑,在服务器侧可以使用比较贵的HBM,如此一来DDR所需的功耗势必会拉升上去,而在端侧,出于成本的考量,还没有特别好的DDR方案。

为了解决阻碍AI落地的内存墙和功耗墙这两个共性问题,业界常用的方法有两种,一种是存算一体,但会受到工艺节点瓶颈的限制,距离量产还有一定的距离;另外一种是减少数据搬运。爱芯元智就是通过混合精度技术减少了数据搬运,从而在一定程度上减小了内存墙和功耗墙的阻碍,提高了整个NPU的效率。

那么,混合精度是如何减少数据搬运的呢?首先要明确混合精度的概念——混合精度就是将不同精度的浮点数/定点进行数值计算。

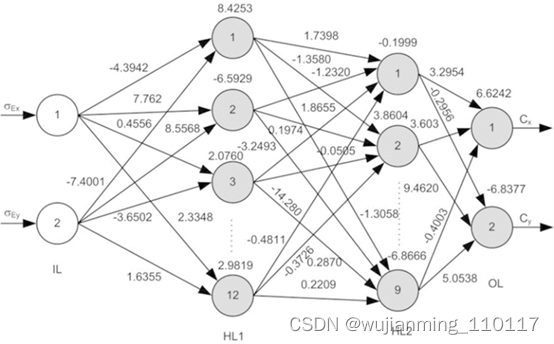

图 | 神经网络示意图(简化版)

如上图所示,其每一数列被称为一个layer层,最左边的是输入层,最右边的是输出层,中间的部分是隐藏层。图中的每个圆圈代表一个神经元,每一个神经元上都有很多链接,链接上的数字是权重,是参与计算的重要组成。如果权重是小数的话,则代表着其为浮点数。

在整个神经网络中,权重系数比较复杂,传统NPU的数据表示格式一般是8比特、16比特和浮点数,才能达到AI算法的精度,所以运算量繁重。但爱芯元智发现,在实际应用中,AI网络中有的信息是有冗余的,这意味着并不是所有的计算都需要高精度的浮点或是高精度的16比特,而是采用8比特或者4比特等低精度混合运算就足够了。

在爱芯元智的AI-ISP应用中,就是基于混合精度技术,网络中许多中间层都是采用INT4精度。相比原来的8比特网络,数据搬运量可能就变成原来的1/2,计算量缩减为1/4。由此便可以提升NPU的使用率和效率,在单位面积内提供数倍于传统NPU的等效算力,同时还能把成本和功耗降下来,更有利于端侧和边缘侧AI落地。

当然,在AI落地的过程中,除了要解决内存墙和功耗墙问题以外,还需要考虑算法和硬件的结合问题。尤其是在端侧和边缘侧,芯片天生就和场景有一种弱耦合的关系,所以爱芯元智在设计AI视觉芯片时,采用了从应用到算法再到NPU的联合优化设计。

图 | 算法与NPU的协同设计

具体来讲,在传统的AI方案中,算法和硬件通常是相互独立的两部分。但爱芯元智的算法团队会在NPU设计早期就将算法网络的结构、量化需求/算子需求、内存访问的需求等很多详细信息提供给NPU设计的架构师,硬件架构师可以根据这些算法的需求来调整或优化整个NPU的设计,从而使算法跑起来的效率达到优化后的水平。与此同时,硬件工程师也会把算子硬件加速条件,例如数据流优化、存储优化、量化限制等硬件限制提供给算法工程师,如此算法工程师在设计算法时,可以考虑到硬件限制,从算法的角度来规避一些硬件上的短板。两者结合,便可以兼顾NPU的硬件和软件开发,加快AI开发的落地效率。

基于以上优势与积累,爱芯元智先后推出了AX630A、AX620A、AX620U、AX170A两代四颗端侧、边缘侧AI视觉感知芯片。其中,AX170A针对手机应用场景,可对4K 30fps的影像进行实时画质优化,配合主控芯片可实现超级夜景视频和优秀的暗光拍摄功能,实现夜晚低照度下高清影像的细腻呈现;AX620A针对智慧城市、智能家居等应用,不仅能实现暗光环境下优异的画质效果,同时还能兼顾约1W的低功耗优越性能,满足电池应用方案的功耗需求,兼顾IoT、智能运动相机、手机等应用场景;AX630A针对智慧城市、智慧交通等密集场景,以强大的暗光图像视频处理能力和20路1080p 30fps的解码能力,能将高画质、全智能、全感知和实时分析的能力优势发挥到极致,可轻松满足客户“全天候”和“看得清”的核心诉求。

图 | AX170A

爱芯元智深知垂直化生态是AI芯片的归途,所以在提供芯片的同时,还提供demo板等开发套件、开源软件包,降低用户的开发难度,缩短用户的开发周期。

而从用户的角度来讲,采用第三方的NPU芯片除了能够降低自身研发难度,获得充足的有效AI计算能力以外,还能降低开发成本,这是AI-NPU使用量越大越好用的优势。

就像爱芯元智创始人兼CEO仇肖莘博士曾在2021世界人工智能大会上所说的:“希望尽一些努力,能够为世界的数字化和智能化新基建,提供更多在边缘侧和端侧的支持,给社会带来更多深刻的变化。”

AI技术成熟度越来越高,NPU大时代来临

随着互联网、移动互联网,以及物联网的发展,人类创造的数据量在快速增加,这些海量的数据为AI的发展提供了肥沃的土壤。加上神经网络算法的进步,及CPU、GPU、NPU、FPGA等各种芯片性能的快速提升,极大地提升了计算机处理海量视频、图像等数据的计算能力。也就是说,在算力、算法和数据三要素快速发展的背景下,AI技术的成熟度越来越高,AI产业不断演进,落地应用也变得更加丰富,AI正在与各行各业的典型应用场景相融合。

这些年,可以明显看到AI在智能手机、智能音箱等消费类电子产品,以及互联网应用等To C端的应用场景中大量落地后,开始向工业制造、能源、交通、金融、医疗、教育、零售、汽车等传统To B端行业渗透。

现在的AI技术已经开始渗透进人们日常生活的方方面面了,那么什么样的AI最有前景,最容易被市场所接受呢?其实未来的AI落地应用可能更多的是一些碎片化的市场,能够在性能和成本之间取得良好平衡的应用可能更加有市场前景。

碎片化将增加企业成本

不论是工业制造、能源、金融、还是交通行业,很多应用场景都是需要根据具体的场景做更多定制化的服务,这必然会增加AI企业的成本负担。比如在工业场景中,AI企业需要帮助工厂设计并训练工业级的高性能AI模型,这就需要AI企业大量的成本投入和深厚的技术沉淀,包括多场景海量数据收集、复杂模型的设计和算法训练、以及包括软件框架和硬件系统在内的AI基础设施来支持大规模运算。而且,由于每个工厂制造的产品是不一样的,产线环境也各不相同,开发的解决方案可能只适用于一家客户,成本得不到均摊,自然就会更高。

还有在交通领域,AI需要对特殊的交通事故、道路塌陷、以及火灾等不同场景进行识别、分析、评估损失等,这些都是极其具体的要求。

碎片化的应用场景还可能会带来另一个问题,由于单个场景发生的频次比较低,可用的数据量会偏少。加上每种模型的生产都需要大量的算力和人力,AI行业的人力投入将会增加,相应AI企业的成本也会增加。

当然,这些碎片化的应用场景,也会有一些好处,那就是大部分的客户其实是不懂AI的,需要的不是一个AI模块,或者开发包,而是一整套定制化的解决方案,而且,因为这种定制化的方案确实也帮助解决了实际问题,因此,也更愿意为此类解决方案付费。

AI背后的NPU

所有落地AI应用中,都需要硬件的算力支持,包括目前市场比较火热的自动驾驶。随着汽车中摄像头、毫米波雷达、激光雷达,以及超声波雷达等环境感知传感器的增多,自动驾驶系统收集的传感器数据将会更多,自动驾驶计算芯片需要通过算法处理、汇算这些数据,实现车、路、人等信息融合,对驾驶控制做出决策。而传感器数量的增多,对自动驾驶计算芯片的算力要求将显著提升。

算力的提升,离不开NPU(Neural-network Processing Unit,神经网络处理器)的支持。是一类基于DSA (Domain Specific Architecture) 领域专用架构技术的专用于人工智能(特别是人工神经网络、机器视觉、机器学习等)硬件加速的微处理器。相比于CPU、GPU,NPU在硬件架构上就是针对AI设计的,非常适合神经网络运算。

NPU与CPU和GPU等通用处理器设计思路不同。通用处理器考虑到计算的通用性,提升的计算能力大部分不能直接转化为神经网络处理能力的提升,比如没有针对MAC运算做专门的提升,而NPU针对神经网络设计,无需考虑神经网络并不需要一些计算单元。相较于CPU擅长处理任务和发号施令,GPU擅长进行图像处理、并行计算,NPU更擅长处理人工智能任务。NPU通过突触权重实现存储和计算一体化,从而提高运行效率。

因此,可以在很多支持AI应用的处理器,或者SoC中发现NPU的身影,比如苹果的A15、特斯拉的FSD芯片、地平线的征程系列芯片、OPPO的马里亚纳X芯片等等。除了这些规模较大,性能较高的SoC芯片,其实现在有些MCU产品也开始集成NPU模块了,以满足一些边缘智能应用的需求。

其实,很多支持AI的SoC芯片都是通过集成神经网络IP来实现的,一般来说,神经网络IP会于神经网络算法同步发展,能够进一步扩展,以应对神经网络性能日益增长的需求。

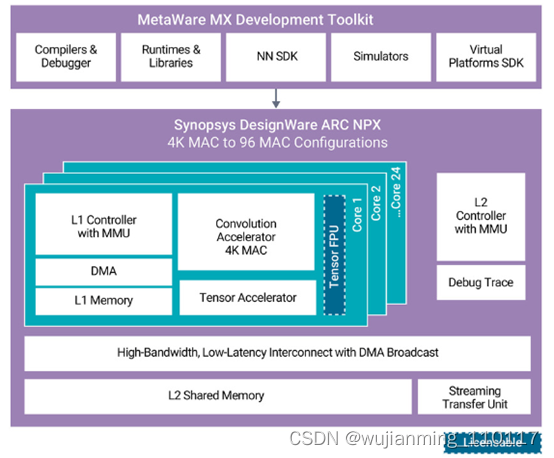

新思科技ARC NPX6 NPU IP

新思科技最近推出了全新的NPU IP核和工具链,以满足神经网络不断发展的需求。同时提供了强大的可扩展性,单个NPU处理器支持从4K MAC到96K MAC的扩展,可以满足不同的应用需求,比如:ADAS,监控,数据电视,摄像头,自然语言处理等等。其ARC NPX6和NPX6FS NPU IP可满足面向AI应用的具有超低功耗的实时计算需求,提供业界最佳性能,并支持最新、复杂的神经网络模型。

图:ARC NPX6 NPU IP

单个NPU可在5nm工艺中以每秒1.3GHz的速率提供高达250TOPS的算力,或通过使用全新稀疏特征提供高达440TOPS的算力,因此可以提高执行神经网络性能并降低能耗需求;新IP集成了硬件和软件链接功能,支持实施多个NPU实例,在单个SoC上可以实现高达3500TOPS的性能;在神经处理硬件内部提供可选的16位浮点支持,以极大提高层性能,并简化了从用于AI原型设计的GPU向大容量功耗和面积优化型SoC的过渡。

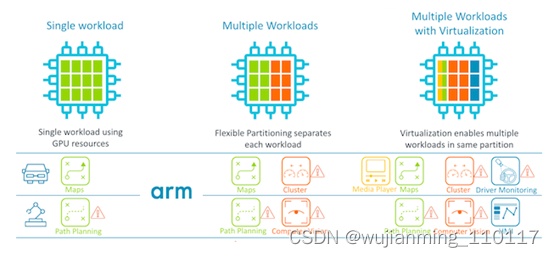

ARC NPX6FS NPU IP是针对功能安全应用的神经网络处理器IP,满足严格的随机硬件故障检测和系统功能安全开发流程要求,完全符合ISO 26262汽车安全完整性等级(ASIL)D级标准。并且,这些处理器包含全面的安全文档,具有符合ISO 26262标准的专用安全机制,并满足下一代区域架构的混合关键性和虚拟化要求。

此外,为了方便工程师使用,加快产品上市时间,新思科技还提供了全新的DesignWare ARC MetaWare MX开发工具包,该工具包包括了编译器和调试器、神经网络软件开发工具包、虚拟平台软件开发工具包、运行时库以及先进仿真模型。

MetaWare MX提供的单一工具链在MAC资源中自动划分算法以实现高效处理,帮助工程师加速应用开发。另外,对于安全关键型汽车应用,该MetaWare MX 安全开发工具包包含了安全手册和安全指南,可帮助开发者满足ISO 26262要求并为ISO 26262合规性测试做好准备。

结语

AI技术正在跟各个细分行业紧密结合,以发挥其优势,在AI技术落地应用越来越多的时候,NPU也变得越来越重要,未来对NPU的需求也将会进一步提升,相信NPU的大时代正在来临。

ADS-NPU芯片架构设计的五大挑战

AI算法在自动驾驶ADS领域的行业应用,其当前从感知到认知的演进方向,主要体现在:

1)能够在统一空间支持多模传感器感知融合与多任务共享,在提升有限算力的计算效率的同时,确保算法模型在信息提取中对极端恶劣场景(雨雪雾、低照度、高度遮挡、传感器部分失效、主动或被动场景攻击等)的泛化感知能力,降低对标注数据和高清地图的过度依赖;

2)预测与规划联合建模,离线与在线学习相结合,监督与自监督学习相结合,从而能够处理不确定性下的安全行驶与有效决策,提供认知决策行为的可解释问题,通过持续学习解决新场景问题。

当前,对应于ADS传感器负载多样化和融合感知决策算法多样化的演进趋势,ADS的算力需求和芯片加速能力以(十倍速/每几年)的持续高增长态势呈现。ADS领域大算力NPU芯片的当前发展现状,真可谓是:大算力之时代,以感知策,四两拨千斤者;狂洗牌乎战局,唯快应变,一力降十会也。

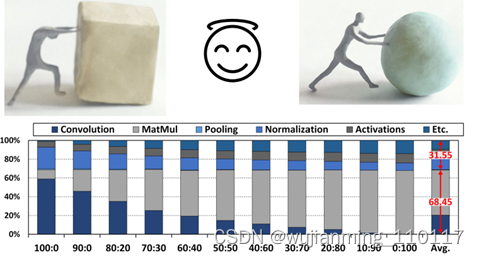

图1. DNN任务占比分析: CNN vs Transformer

(图表分析来自文献1)

如图1 所示,ADS算法从Compute-bound向Memory-bound演进。ADS的存算混合需求,可以通过“硬件预埋,算法迭代,算力均衡“ ,来提供一个向前兼容的解决方案,以通用大算力NPU设计来解决算法未来的不确定性,具体体现在:1) 底层架构的演进:从存算分离到近内存计算,最终走向内存计算; 2) 数据通道与模型:高速数据接口+数据压缩+模型压缩+低精度逼近计算+稀疏计算加速; 3) 并行的顶层架构:模型-硬件联合设计,以及硬设计可配置+硬件调度+软运行可编程调度引擎。

老子曾曰“合抱之木,生于毫末;九层之台,起于垒土;千里之行,始于足下。” 老子又曰 ”天下难事,必作于易;天下大事,必作于细。”处理艰难问题从易入手,致力远大目标从微着力。ADS-NPU芯片的架构设计,同样需要用【见微知著】的能力,来解决异构计算、稀疏计算、逼近计算、内存计算等几类常见的难题与挑战。

- 异构计算之设计挑战

图2. 脉动阵列架构(图表分析来自文献1)

图3. 可配置的脉动阵列架构(图表分析来自文献1)

对比CPU十百级的并行处理单元和GPU上万级的并行处理单元,NPU会有百万级的并行计算单元,可以采用Spatial加速器架构来实现,即Spatial PE空间单元阵列通过NoC,数据总线,或跨PE的互联来实现矩阵乘运算(全卷积计算或全连接FC计算)、数据流高速交互、以及运算数据共享。

粗颗粒度的可配置架构CGRA是Spatial加速器的一种形态,即可配置的PE Array通过纳秒或微秒级别可配置的Interconnect来对接,可以支持配置驱动或者数据流驱动运行。

如图2和图3所示,脉动Systolic加速器架构也是Spatial加速器的一类实现方式,其主要计算是通过1D或2D计算单元对数据流进行定向固定流动处理最终输出累加计算结果,对DNN输出对接卷积层或池化层的不同需求,可以动态调整硬件计算逻辑和数据通道,但存在的问题难以支撑压缩模型的稀疏计算加速处理。

NPU的第二类计算单元是Vector矢量加速器架构,面向矢量的Element-wise Sum、Conv1x1卷积、Batch Normalization、激活函数处理等运算操作,其计算可以通过可配置的矢量核来实现,业界常用的设计是标量+矢量+阵列加速器的组合应用来应对ADS多类传感器的不同前处理需求和多样化算法模型流水线并行处理的存算混合需求。

NPU SoC也可以采用多核架构技术,即提供千百级的加速器物理核来组件封装和Chiplet片上互联提供更高程度的平行度,尤其是适合大算力下高并行数据负载,这需要底层硬件调度与上层软件调度相结合,提供一个分布式硬件计算资源的细颗粒度运行态调用。

NPU另外一个在演进中的内存处理器PIM架构,即通过将计算靠近存储的方式来降低数据搬移能耗和提升内存带宽。可以分成近内存计算与内存计算两种类型。近内存计算将计算引擎靠近传统的DRAM或者SRAM cell,保持设计特性。

内存计算需要对内存cell添加数据计算逻辑,多采用ReRAM或者STT-MRAM新型工艺,目前采用模拟或数字类型的设计,可实现>100TOPS/Watt的PPA性能,但技术难题是如何在运行态时进行大模型参数动态刷新,工艺实现可能也落后于市场预期。

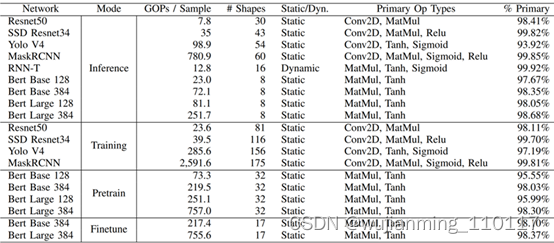

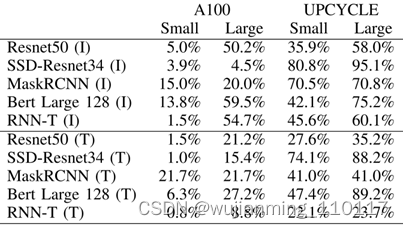

图4. AI算法模型负载的算子分布统计(图表分析来自文献2)

图5. nVidia A100的TensorCore架构与UPCYCLE 融合架构的计算效率对比

(图表分析来自文献2)

当前市场上主流AI芯片,常用的架构有以下几种形态:1) GEMM加速架构(TensorCore from nVidia, Matrix Core from AMD); 2) CGRA (初创公司); 3) Systolic Array (Google TPU); 4) Dataflow (Wave, Graphcore,初创公司); 4) Spatial Dataflow (Samba Nova, Groq); 5) Sparse架构 (Inferentia)。

如图4与图5所示案例可以看出,ADS-NPU设计其中有一个挑战是低计算效率问题。异构计算架构一个主要的目的是希望从设计方法学上找到一个硬设计时优化可配置与软运行时动态可编程的平衡点,从而能够提供一个通用的方案覆盖整个设计空间。

另外值得一提的是,UPCYCLE 的融合架构案例,涉及到SIMD/Short Vector, Matrix Multiply, Caching, Synchronization等多核优化策略,这个案例,说明只是通过短矢量处理+传统的内存缓存+同步策略的传统方法结合,在不使用标量+矢量+阵列的微架构组合条件下,依旧可以从顶层软件架构层面的优化(指令集和工具链优化策略,模型-硬件联合优化)来实现7.7x整体计算性能提升与23x功耗效率提升。

2. 稀疏计算之设计挑战

ADS-NPU低效率计算问题,从微架构设计领域,可以涉及到:1) 稀疏数据(稀疏DNN网络,或者稀疏输入输出数据)导致PE对大量零值数据的无效计算问题;2)PE之间由于软件硬件调度算法的效率低,PE之间互相依赖导致的延迟问题;3)数据通道与计算通道峰值能力不匹配导致的数据等待问题。

上述问题2和问题3可以从顶层架构和存算微架构设计上来有效解决。问题1可以对稀疏数据进行压缩处理来有效提升微架构计算单元PE的效率。如图6和图7所示,稀疏数据图编码的案例,可以有效提升数据存储空间和对数据通道的冲击,计算单元依据非零数据NZVL分布图进行有效甄别计算,以添加简单的逻辑单元为代价就可以将一个72PE的计算效率提升到95%,数据带宽降低40%。

图6. 稀疏计算微架构案例(图表分析来自文献3)

图7. 稀疏数据图编码案例(图表分析来自文献3)

3. 逼近计算之设计挑战

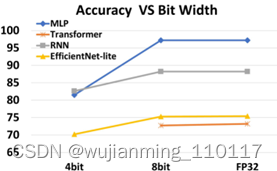

图8. 算法模型与量化表征的关系案例(图表分析来自文献6)

算法模型与量化表征的关系案例如图8所示,逼近计算设计可以通过算法模型的低比特参数表征+量化后训练的方式,在不降低算法模型精度的情况下,通过时间和空间复用的方式,等效增加低比特MAC PE单元。

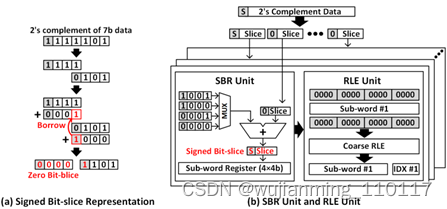

逼近计算的另外一个优势是可以与稀疏计算相结合。低比特表征会增加数据的稀疏特性,类似ReLU等激活函数和池化计算也会产出大量零值数据。另外浮点数值如果用bit-slices进行表征,也会有大量高位零比特特征。

零值输出数据意味着可以通过预计算可以直接跳过后续大量的卷积计算等。如图9所示的案例,其中简单的bit-slice数据分解表征会产生偏置分布,可以通过Signed Bit-Slice方法来解决,从而将PPA性能有效提升到(x4能耗,x5性能,x4面积)。

图9. Signed Bit-Slice和RLE游程编码案例 (图表分析来自文献4)

4. 内存计算之设计挑战

ADS-NPU设计其中有一个挑战是数据墙问题能耗墙问题,即计算单元PE存算分离设计导致数据重复搬移,数据共享困难,数据通道与计算通道峰值能力不匹配会导致PE的低效率和SRAM/DRAM高能耗。

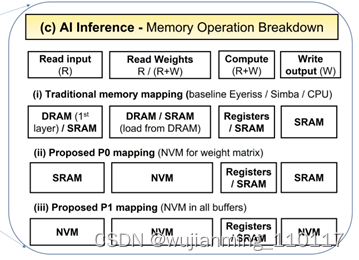

图10. MRAM取代SRAM案例 (图表分析来自文献5)

一个有趣的尝试是用新型工艺MRAM (STT/SOT/VGSOT-MRAM) 来部分或全部取代SRAM, P0方案是只取代算法模型参数缓存和全局参数缓存;P1方案是MRAM全面取代SRAM。对比SRAM-only架构,从图10 的案例可以看出MRAM-P0解决方案可以有>30%能耗提升,MRAM-P1解决方案有>80%能耗提升,芯片面积减少>30%。

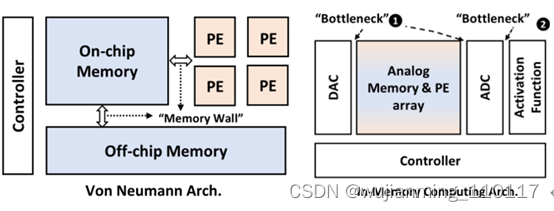

图11. Von Neumann与内存计算的架构对比 (图表分析来自文献6)

图12. 内存计算的模拟墙问题 (图表分析来自文献6)

当前初创公司的内存计算架构策略需要对内存cell添加数据计算逻辑,通过采用ReRAM或者STT-MRAM新型工艺,采用模拟或数字类型的设计来实现。模拟内存计算IMC对打破传统的Von Neumann计算机架构内存墙和能耗墙应该更有优势,但需要同时打破设计中的模拟墙问题,这也是当前数字设计IMC-SRAM或者IMC-MRAM占多数的原因。

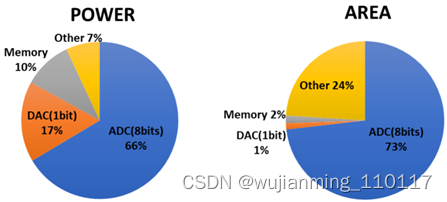

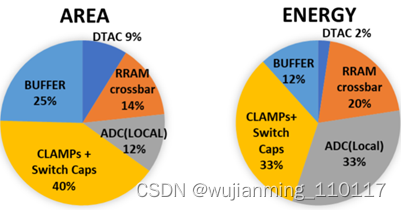

如图11和图12所示,IMC的主要问题来自于模数转换ADC/DAC接口和激活函数的接口带来的设计冗余。一种新的实验设计是用基于RRAM的RFIMC微架构(RRAM cells + CLAMP circuits + JQNL-ADCs + DTACs)。每个RRAM cell代表2比特内存数据,4个RAM cell来存储8比特的权重,JQNL-ADC采用8比特浮点数。

从图13可以看出RFIMC的微架构能够部分解决模拟墙的问题,可实现>100TOPS/Watt的PPA性能,但存在的问题是,只支持小规模的全矢量矩阵乘,超大尺寸的矩阵乘,需要将模拟数据进行局部搬移,是否有数据墙的问题仍未知。

图13. RFIMC的性能分解图 (图表分析来自文献6)

5. 算法-硬件之共同设计挑战

ADS算法多样化的演进趋势和对NPU大算力存算的混合需求,需要算法-NPU联合设计来实现模型整体效率。

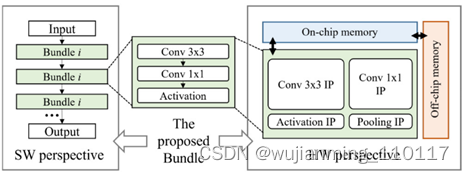

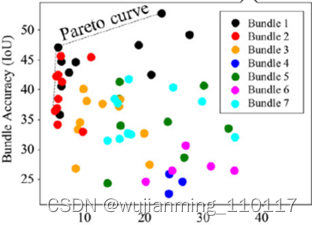

常用的量化与模型裁剪能够解决一部分问题,模型-硬件联合搜索,可以认为NPU预定义的硬件架构是模板,网络模型ASIC-NAS是一个典型的案例,即在有限硬件计算空间内进行DNN的模型搜索和模型小型化,寻求计算单元的最佳组合模型来提升相同计算复杂度下的等效算力效率。

NPU添加了硬件的可配置和细颗粒可调度,但依旧存在很大的性能约束性。如图14 和图15所示,SkyNet算法与硬件共同设计的案例,是将NPU细颗粒度的PE单元进行Bundle优化封装,其价值在于可以降低NAS架构搜索的高维空间,从而减低对硬件底层架构的依赖关系和优化算法的复杂度。

图14. SkyNet算法与硬件共同设计案例 (图表分析来自文献7)

图15. SkyNet-Bundle-NAS示例 (图表分析来自文献7)

ADS算力芯片NPU数据流的重用性

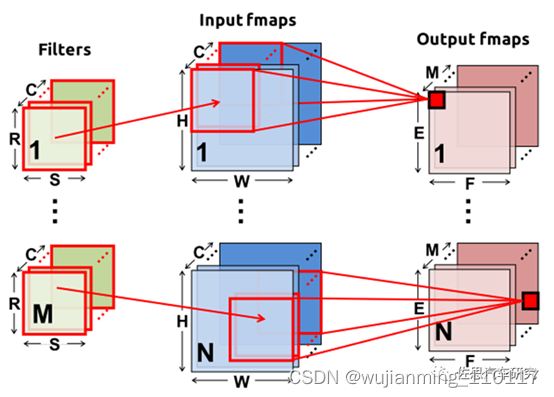

深度神经网络正在以越来越大的规模部署,横跨了从云端,自动驾驶到IoT等平台。比如用于图像识别,语音识别及翻译,癌症检测以及自动驾驶中对感知层海量数据的处理等。在很多领域,深度神经网络的精度已经超越人类,优越性来源于对原始数据的特征提取,并通过对大量数据的学习来获取输入空间的有效表征,但是高精度是以超高计算复杂度为代价。因此很多厂商都在追逐NPU的算力来解决这些复杂问题,但是随着算力的提高,NPU设计也越来越复杂,将伴随着面积和功耗的增加,这对于那些面积和功耗有很大限制的设备带来了挑战,因此如何提升NPU的能效比就成了亟待解决的问题。

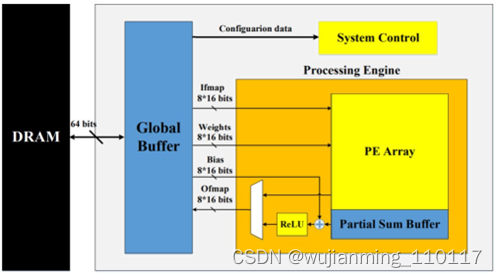

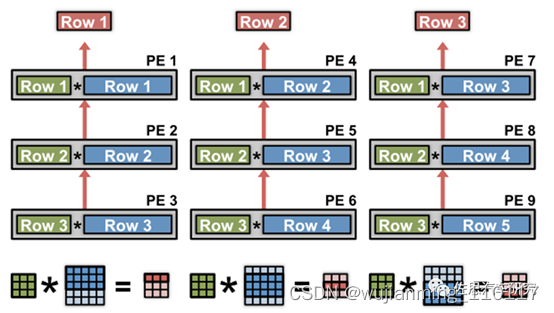

NPU通过数据分区和有效调度,利用数据的重用以及执行分段来提高能效比和硬件利用率,而实现高利用率,数据重用将直接依赖于如何调度深度神经网络的计算和如何将这些计算有效的映射到NPU的硬件单元上。以CNN为例,数据流无非包含三个方面filter(Weight),ifmap和ofmap,如下图。

因此在设计NPU时需要考虑如利用内存的层次结构,决定哪些数据要读到那一层的内存中以及什么时候被处理,如何可以重用filter,ifmap和ofmap,将存放在本地内存中,从而大大减少DRAM的访问次数,这将在很大程度上提高NPU的硬件利用率及性能,并减少由于DRAM访问带了的额外功耗。根据数据处理特征可以将数据流分为以下几类:

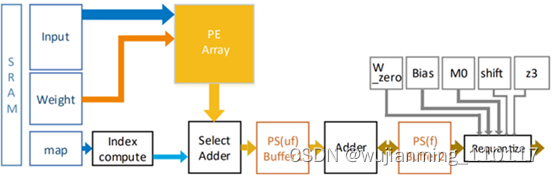

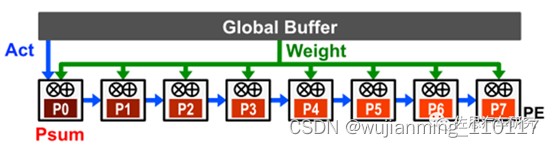

1)、静态weight

weight静态数据流的设计是通过在PE的RF(Register File)中存取weight,来减少读取weight产生的功耗。weight从DRAM读取到RF并保持静态以供进一步访问,NPU在计算时尽可能多的利用RF中的weight以达到最大程度的重用。通常的实现是将ifmap广播给所有的PE,部分和(Psum)将穿过所有的PE来完成空间上的累加。

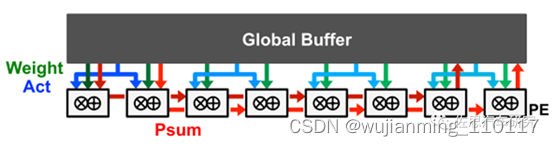

2)、静态输出

输出静态数据流的设计是通过将accumulator产生的Psum存放到本地的RF中,以避免将Psum刚写入DRAM再读回,从而减少因Psum读写产生的功耗。通常的实现是流式输入Activation,并将weight广播给所有的PE。

3)、无本地重用

如果考虑到RF会增大面积,可以将所有的数据都存放到Global Buffer中,这样没有任何数据会留在PE的RF,也不会增设RF单元来减小面积,但是增加了PE和Global Buffer的数据交互。具体来说是通过多广播Activation,单广播Weight以及Psum穿过所有的PE进行累加来实现的。

4)、静态行

静态行数据流的目标是将所有的数据类型(Activation, weight, psum)的重用和计算都在RF中完成,来提升总体的能效。区别于上面的静态weight和静态输出,只是分别对weight和psum进行优化。

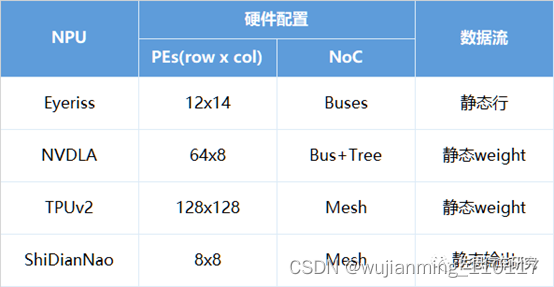

具体选用哪种数据流方式要结合NPU微架构的设计。下面总结了来自于几个厂家的NPU,分别利用了不同数据流类型来提高能效比。

架构升级,ARM v9与v8版本有何不同?

自Arm在2011年10月首次发布Armv8架构以来,已经过去了近十年的时间。这对Arm来说是一个相当可观的十年,因为在这段时间内,指令集架构受到移动市场和服务器市场的高度关注,并铆足劲在包括笔记本电脑和台式机设备市场发力。过去多年里,Arm对ISA进行了改进,也对体系结构进行了各种更新和扩展。当中一些可能很重要,有些可能也是一瞥而过。

参考文献链接

https://mp.weixin.qq.com/s/xc_-5SmtWLGQuX3w-ptPfA

https://mp.weixin.qq.com/s/samT5gYMsrwBguvMTHbS9Q

https://mp.weixin.qq.com/s/uJkAhJzUpGeyYvO92p4-Ow

https://mp.weixin.qq.com/s/BRY2ExcWztl7vf69UyNAUw

https://mp.weixin.qq.com/s/BKzNwfVe-Bsoh_2090HHcQ